使用AXI4接口IP核进行DDR读写测试

描述

一、实验任务

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

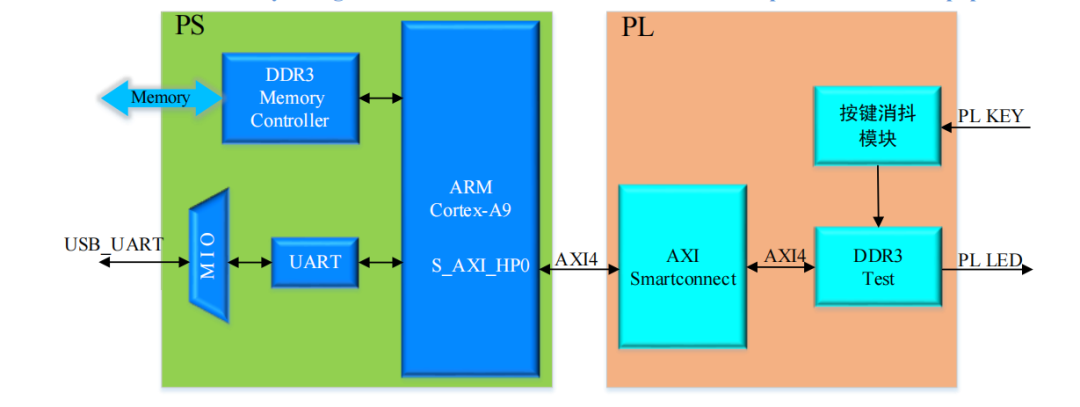

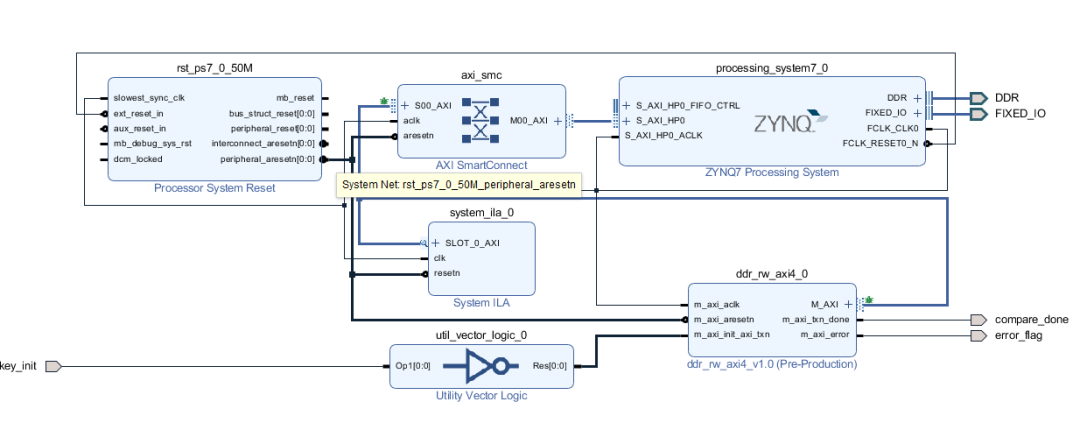

二、实验整体框架

三、实验步骤

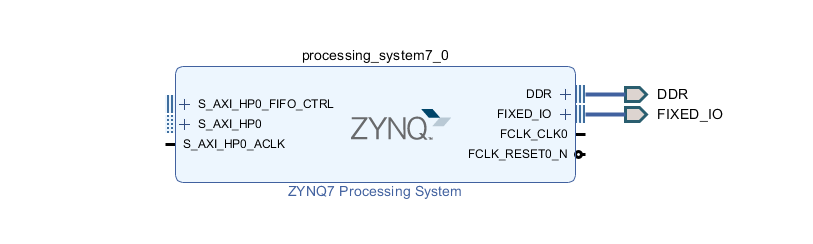

一、在原来的hello_word工程另存并修改zynq ip。添加axi hp接口,恢复以前的ip状态

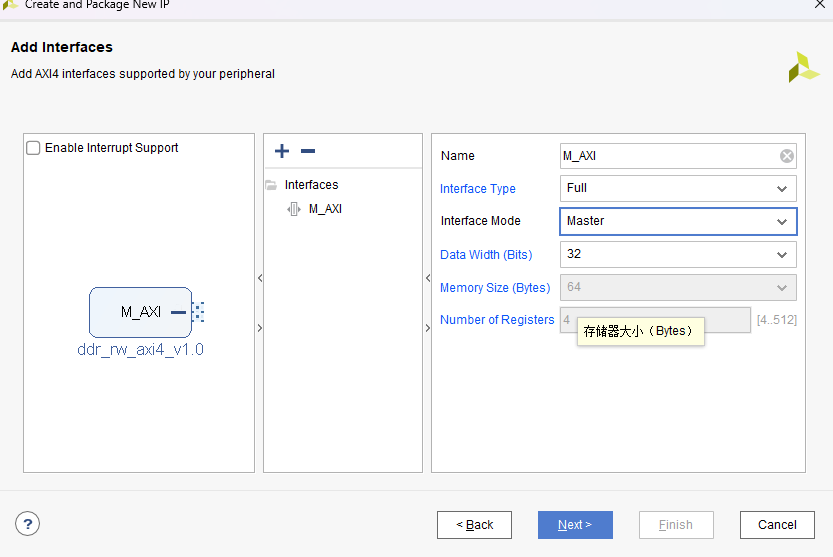

二、自定义axi4 full ip核将ip改为主机接口。如图

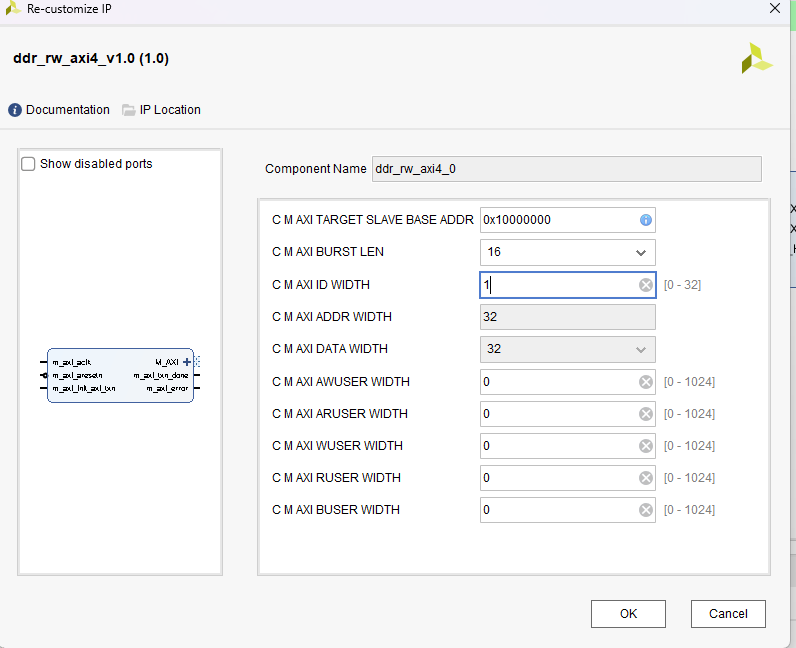

三、添加自定义ip并修改参数

四、点击自动连接

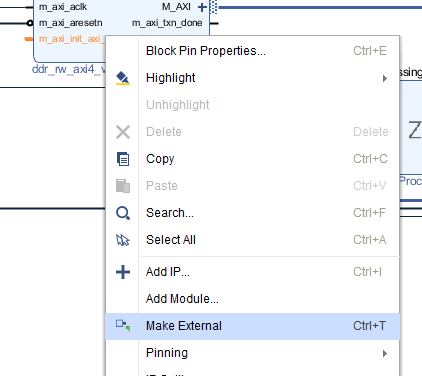

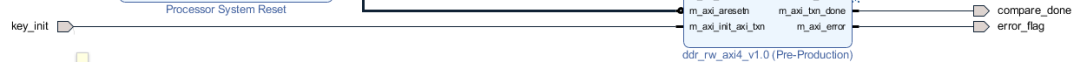

五、添加pl端信号,m_axi_init_txn这个信号是初始化信号,检测到上升沿的时候才有效,检测到高电平后会立马对地址指向的数据内存初始化,然后我们对齐重命名。m_axi_txn_done这个是对写入和读出的数据对比完成信号。m_axi_erro这个是写入和读数据对比有误信号。这几个信号都改名和引出。如下几个图:

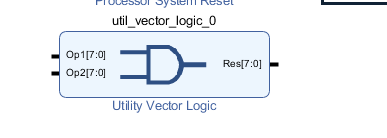

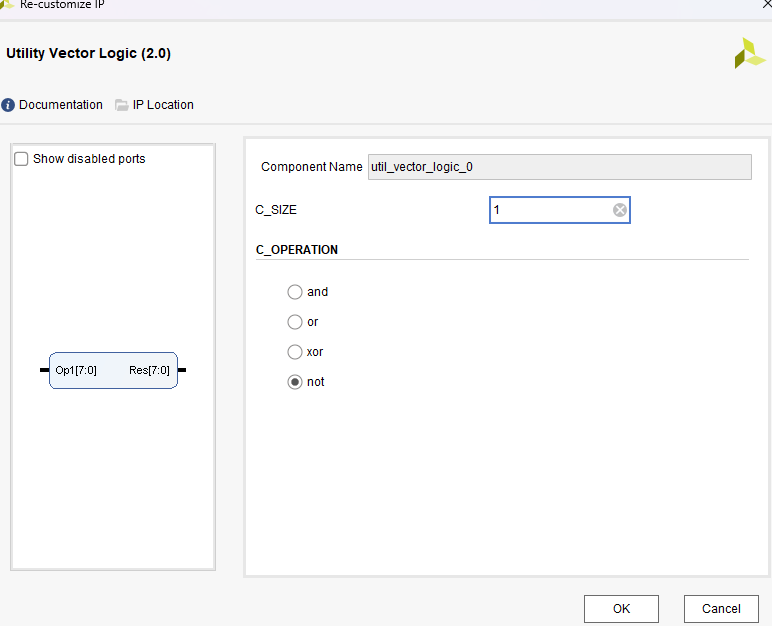

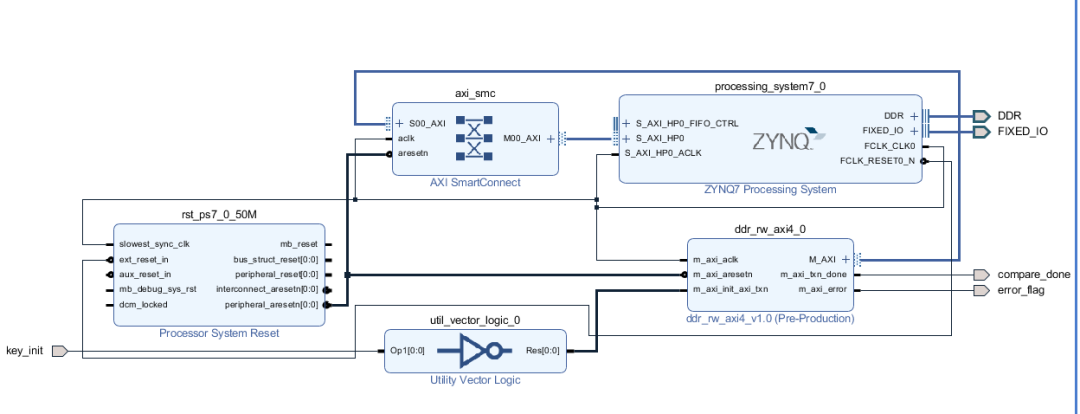

五、m_axi_init_txn连接按键,m_axi_txn_done和m_axi_erro连接led用作观察。由于我的板子只有一个pl端的led因此我就将m_axi_erro信号随便连接一个GPIO外设由于我们的按键一开始为高电平,而DDR初始化信号检测到上升沿才初始化。因此我们这里加一个取反模块。修改属性并手动连接。并验证整个设计

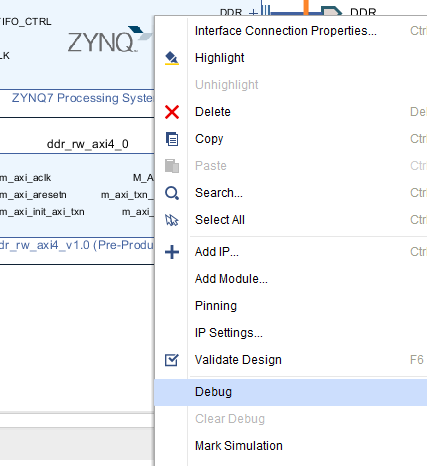

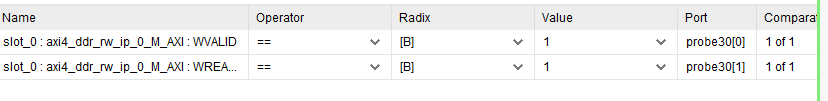

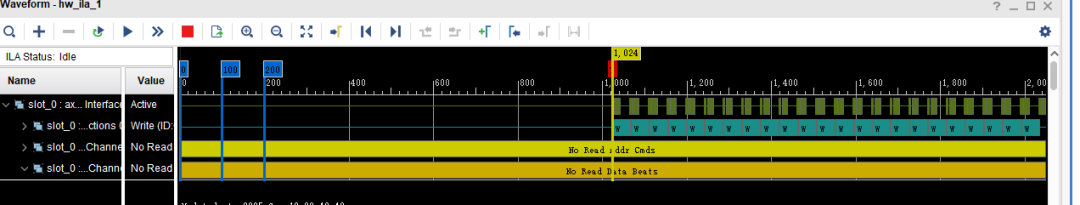

6、为AXI读写添加debug信号,并自动连接

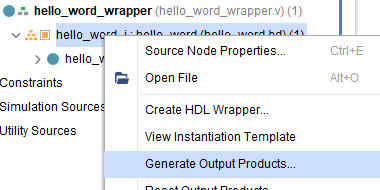

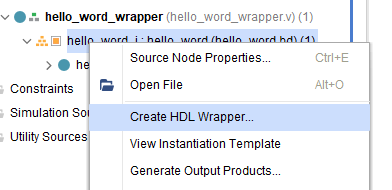

7、生成模块并且更新顶层文件,其他的保持默认ok即可

8、综合以便添加引脚

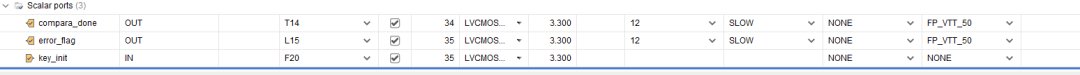

9、添加引脚

10、生成bit流。

11、导出硬件设计,打开SDK,将原来的SDK删掉

12、新建项目添加以下文件。

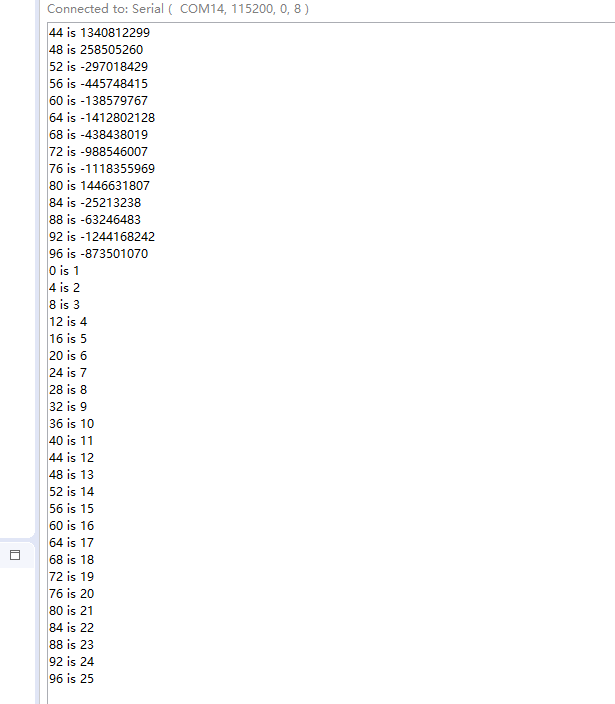

这里由于我用不了scanf因此我就添加一个延迟烧录后在延迟这段时间进行初始化和生成debug触发信号。

#include"stdio.h"#include"xil_cache.h"#include"xil_io.h"#include"xil_printf.h"#include"sleep.h"intmain(){Xil_DCacheDisable();//char *data_in="I have write and read ddr data!

";for(int i=0;i<100;i+=4) {printf("%d is %d

",i,(int)(Xil_In32(0x10000000+i))); }sleep(10);for(int i=0;i<100;i+=4) {printf("%d is %d

",i,(int)(Xil_In32(0x10000000+i))); }return0; }

12、观察数据,正确

-

使用AXI-Full接口的IP进行DDR的读写测试2022-07-18 6968

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 5132

-

NVMe IP之AXI4总线分析2025-06-02 6042

-

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.02025-11-14 758

-

PCIE项目中AXI4 IP核例化详解2019-12-13 3697

-

【正点原子FPGA连载】第十五章AXI4接口之DDR读写实验--领航者ZYNQ之嵌入式开发指南2020-09-04 5129

-

【正点原子FPGA连载】第九章AXI4接口之DDR读写实验--摘自【正点原子】达芬奇之Microblaze 开发指南2020-10-22 4478

-

看看在SpinalHDL中AXI4总线互联IP的设计2022-08-02 3193

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 17715

-

AXI4接口协议的基础知识2020-09-23 6915

-

ZYNQ中DMA与AXI4总线2020-11-02 5012

-

FPGA AXI4协议学习笔记(二)2023-05-24 2747

-

基于AXI总线的DDR3读写测试2023-09-01 7257

-

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍2024-07-18 1423

-

AMBA AXI4接口协议概述2024-10-28 1370

全部0条评论

快来发表一下你的评论吧 !