ADS54RF63 12 位 500/550MSPS 高速模数转换器(ADC)产品手册总结

描述

ADS5463/ADS54RF63 是一种 12 位、500/550 MSPS 的模数转换器(ADC),可同时使用5伏电源和3.3伏电源,同时提供兼容 LVDS 的数字输出。该ADC属于一系列12位、13位和14位ADC,运行频率范围为210 MSPS。ADS5463/ADS54RF63输入缓冲器隔离了板载轨道和保持(T&H)内部的切换,避免干扰信号源,同时提供高阻抗输入。

*附件:ads54rf63.pdf

当模拟输入频率超过~350 MHz或需要高达550 MSPS时,ADS54RF63相比ADS5463提供更优的SFDR。

ADS5463/ADS54RF63提供TQFP-80 PowerPAD™封装。ADS5463/ADS54RF63基于德州仪器互补双极工艺(BiCom3)构建,并适用于整个工业温度范围(-40°C至85°C)。

特性

- 12位分辨率

- 片上模拟缓冲

- ADS5463:500 MSPS

- ADS5463 SFDR:300 MHz f频率时77dBc

在 - ADS54RF63:550 MSPS

- ADS54RF63 SFDR:900 MHz f 频率下 70dBc

在 - 2.3 GHz 输入带宽

- LVDS兼容输出

- 极低延迟:3.5个时钟周期

- 高模拟输入摆幅无损伤,> 10 V

PP差分交流信号 - 总功耗:2.2瓦

- 80针TQFP PowerPAD封装(14毫米×14毫米封装)

- 工业温度范围:-40°C至85°C

- 引脚相似/兼容12位、13位和14位系列:ADS5440/ADS5444/ADS5474

- 应用

- 测试与测量仪器

- 软件定义无线电

- 数据采集

- 功率放大器线性化

- 通信仪器

- 雷达

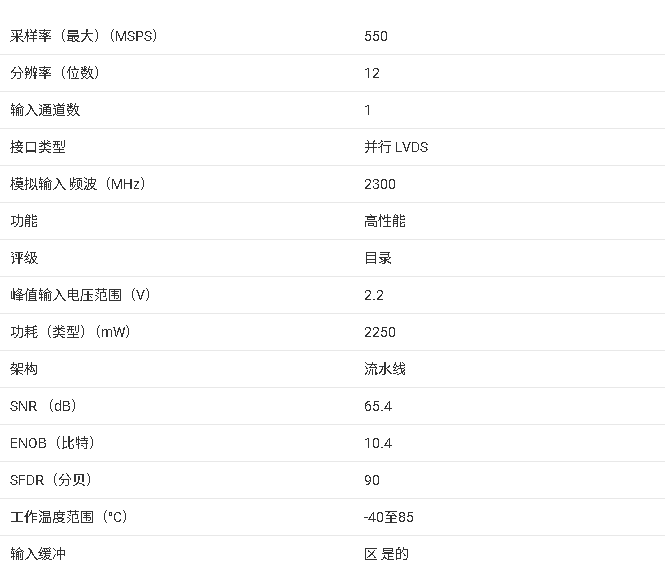

参数

一、产品核心概述

ADS5463/ADS54RF63 是德州仪器推出的两款高性能单通道高速 ADC,核心优势为超宽带输入、低延迟与高动态性能。ADS5463 最高采样率 500MSPS,ADS54RF63 达 550MSPS(高频输入场景性能更优),分辨率均为 12 位,工作温度范围 -40°C~85°C,采用 80-TQFP PowerPAD™ 封装(14mm×14mm),供电为 5V(模拟)与 3.3V(模拟 / 数字),集成片上模拟缓冲器、LVDS 输出接口,适用于测试测量仪器、软件无线电、雷达、功率放大器线性化等高速高带宽数据采集场景。

二、关键特性与规格

1. 核心性能参数

- 分辨率与线性度 :12 位无丢失码,微分非线性(DNL)±0.95LSB,积分非线性(INL)±4.5LSB(ADS54RF63 550MSPS);偏移误差 ±11mV,偏移温漂 0.0005mV/°C,增益误差 ±5% FS。

- 动态性能:输入带宽 2.3GHz,300MHz 输入时 ADS5463 SFDR 77dBc、ADS54RF63 78dBc;900MHz 输入时 ADS54RF63 SFDR 70dBc(远超 ADS5463 的 55.5dBc);SNR 典型 64.7dBFS(10MHz 输入),双音互调失真(IMD3)最高 96.1dBFS。

- 输入与参考:差分输入范围 2.2Vpp,共模电压 2.4V;支持内部(2.4V 标称)/ 外部参考,输入阻抗 1kΩ,输入电容 2.3pF。

- 功耗与延迟:总功耗 2.2~2.5W,孔径延迟 200ps,孔径抖动 150fs rms;数据延迟仅 3.5 个时钟周期,为高速系统提供实时响应。

2. 核心功能

- 超宽带输入:片上模拟缓冲器隔离内部开关噪声,输入带宽覆盖 2.3GHz,支持 >10Vpp 差分交流信号输入而不损坏,适配高频射频(RF)信号直接采样。

- 低噪声与抗干扰:电源抑制比(PSRR)85dB,共模抑制比(CMRR)90dB(10MHz),有效抑制电源噪声与共模干扰;空闲通道噪声仅 0.7~0.8LSB rms。

- 灵活输出与指示:12 路 LVDS 兼容输出(偏移二进制格式),含数据就绪(DRY)与过范围(OVR)指示;DRY 信号为源同步时钟,支持 DDR 模式捕获数据。

- 高频优化:ADS54RF63 针对 350MHz 以上高频输入优化,SFDR 性能显著优于 ADS5463,更适合超宽带通信、雷达等高频场景。

三、封装与引脚

1. 封装信息

- 80-TQFP PowerPAD™ 封装:外露热焊盘(6.15mm×6.15mm~7.5mm×7.5mm)接 AGND 优化散热;MSL 等级 4,支持 260°C 回流焊,符合 RoHS 标准,ESD 防护等级 2kV(人体模型)。

2. 关键引脚功能

- 电源与地:AVDD5(5V 模拟供电)、AVDD3(3.3V 模拟供电)、DVDD3(3.3V 数字 / 输出供电)、AGND/DGND(模拟 / 数字地),需就近并联 0.1μF 陶瓷电容去耦。

- 输入与参考:AIN/AIN(差分模拟输入对)、VREF(参考电压输入 / 输出,需并联 0.1μF 滤波电容)。

- 控制与输出:CLK/CLK(差分时钟输入,上升沿触发转换)、D0~D11(LVDS 数据输出,D11 为 MSB)、DRY/DRY(数据就绪 LVDS 对)、OVR/OVR(过范围指示 LVDS 对)。

四、工作模式与核心功能

1. 核心工作模式

- 采样模式:单通道流水线架构,采样率 20MSPS(ADS5463)/40MSPS(ADS54RF63)

500/550MSPS,时钟支持差分(0.53.5Vpp)或单端输入, duty cycle 兼容 40%~60%。 - 输出模式:LVDS 差分输出(100Ω 端接),DRY 频率为时钟频率的 1/2,数据在 DRY 上升 / 下降沿更新,支持多片同步采集。

- 过范围处理:输入超 2.2Vpp 时输出钳位至全 0 或全 1,OVR 信号置高,方便系统增益动态调整。

2. 关键功能

- 片上缓冲器:隔离输入源与内部采样开关,降低对信号源的负载影响,提升高频输入时的信号完整性。

- 外部参考校准:支持通过 VREF 引脚外接参考电压,实现信号增益微调(约 -0.3dB/100mV),适配多设备同步场景。

- 低延迟设计:3.5 个时钟周期的极短延迟,满足雷达、实时信号处理等对响应速度要求严苛的应用。

五、应用场景与设计支持

1. 典型应用

- 测试测量:高速示波器、频谱分析仪、数据采集卡(DAQ)。

- 通信与雷达:软件无线电(SDR)、5G 基站、脉冲雷达信号采集、卫星通信接收端。

- 工业与国防:功率放大器线性化、电子战系统、精密仪器高速数据采集。

2. 设计资源

- 电源与去耦:模拟与数字电源分开布线,每个电源引脚就近放置 0.1μF 陶瓷电容;外露热焊盘必须焊接到接地平面,通过 6×6 阵列热过孔增强散热。

- 布局要点:输入与时钟走线远离数字信号线,LVDS 输出采用 100Ω 差分阻抗控制,走线长度匹配;高频应用时时钟需低抖动源(如 CDC7005),推荐差分时钟输入以抑制共模噪声。

- 输入驱动:支持变压器(单端转差分)、THS9001(RF 增益放大器)、THS4509(差分放大器)等驱动方案;高频输入推荐差分驱动,确保信号完整性。

- 时钟设计:时钟抖动直接影响动态性能,450MHz 输入时推荐时钟 rms 抖动 ≤181fs;时钟幅度建议 ≥0.5Vpp,高频场景优先选择 ≥3Vpp 差分时钟。

六、可靠性与订单信息

- 可靠性保障:绝对最大额定值:AVDD5 5.25V,引脚电压 -0.3V~AVDD5+0.3V,结温 150°C;85°C 无气流环境下,2.4W 功耗时结温约 142°C,建议通过气流或散热片降低结温以延长寿命。

- 可订购型号:ADS5463IPFP(托盘 96 片)、ADS5463IPFPR(卷盘 1000 片);ADS54RF63IPFP(托盘 96 片)、ADS54RF63IPFPR(卷盘 1000 片),引脚镀层 NIPDAU,支持国防、航空航天增强版本(ADS5463-EP/SP)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析ADS5463/ADS54RF63:高性能12位ADC的卓越之选2025-11-28 673

-

ADS1675 24 位 4MSPS 高精度模数转换器(ADC)产品手册总结2025-11-24 801

-

ADS7863A双路,12位,2MSPS,模数转换器(ADC)数据表2024-07-30 518

-

ADS5522高性能、12位、80 MSPS模数转换器(ADC)数据表2024-07-27 780

-

ADS5520高性能、12位、125 MSPS模数转换器(ADC)数据表2024-07-26 893

-

ADS5463/ADS54RF63一款12位、500/550 MSPS模数转换器(ADC)数据表2024-07-24 704

-

ADS5463-SP 12位500 MSPS模数转换器数据表2024-07-22 627

-

ADS7883一款12位、3 MSPS模数转换器(ADC)数据表2024-07-19 593

-

ADS5403单通道12位,500Msps模数转换器数据表2024-07-17 444

-

ADS5424 14位、105 MSPS模数转换器(ADC)数据表2024-07-16 737

-

ADS7886一款12位、1 MSPS模数转换器(ADC)数据表2024-07-15 586

全部0条评论

快来发表一下你的评论吧 !