基于软件无线电数字下变频的FFT技术在频谱分析仪中与单片DSP里实现

描述

引 言

在频谱分析仪中,传统的FFT实现方法首先是对低中频信号进行ADC低采样率采样,然后将采样数据保存在RAM中;当数据足够后,进行FFT运算,将获得的频谱数据显示在屏幕上。这种FFT方法可以说是简单易行,但在处理宽带高中频信号方面,由于受Nyquist采样定理的约束,需要使用高采样率。此时实现窄的分辨率带宽将需要大量的采样数据,这就使得系统不仅需要提高存储空间,而且增加了运算量,同时有很多冗余输出数据,导致算法的效率非常低下。

随着高速A/D变换和DSP技术的发展,软件无线电设计思想也被应用到频谱分析仪中,基于软件无线电数字下变频的FFT技术能够有效减少上述传统FFT技术存在的问题。在高中频、高采样率系统中,能实现信号频谱的高分辨率、低存储量和低运算量,从而极大地提高了系统的实时性。

1 频率分辨率

在频谱分析仪的FFT谱分析中,信号的频率分辨率RBW定义为:

式中:fs为采样率;N为FFT点数。

如果考虑采用窗函数,则分辨率带宽RBW定义为:

式中:K为窗函数-3 dB带宽因子。

由于fs是ADC的采样频率,是常数,K也是一个定值,因此要减小RBW值,只能增加N。但增加N会增加处理时间,还要增加存储器容量,所以N的增加受到限制。在频谱分析仪中一般N不大于64K。

2 数字下变频FFT技术

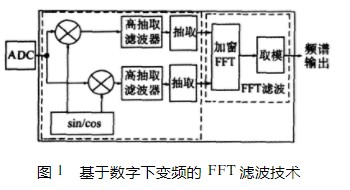

基于数字下变频的FFT技术的实现原理框图如图1所示。

假设希望对整个频带中频率为fIF的两边±B/2的一段频率范围内进行FFT,整个处理过程可分为数字下变频和FFT滤波2个模块。

数字下变频模块的处理过程包括以下3个步骤:

(1) 数字变频,将感兴趣部分的频谱下变频到零频附近。先以fs对信号进行采样,得到N点序列x(n),然后与数字本振复信号cos(2πfIFnT)+jsin(2πfIFnT)(T=fIF/fs)进行数字混频,获得I/Q两路信号,将x(n)的频谱x(k)平移了fIF,此时原信号频率fIF的分量被移至零频处。

(2) 高抽取滤波,用一个带宽等于B的高抽取滤波器(如5级CIC抽取滤波器)对变频至零频的信号滤波,则输出信号含有x(n)在fIF±B/2范围内的频率成分。

(3) 抽取,实现对滤波后信号的抽取。若fs/B=D,得D为抽取因子,此时输出数据的采样频率缩小了D倍;又因为使用了高抽取抗混叠滤波器,此时的信号频谱是不会发生混叠的。

FFT滤波模块的处理过程则包括以下2个步骤:

(1) 加窗FFT,对经过数字下变频的I/Q两路信号先乘上窗函数,然后进行复数FFT。此时FFT的点数为M=N/D,其频谱就是fIF±B/2内的频谱,但却有传统N点FFT的分辨率效果。

(2) 取模,就是获取复信号的幅度信息,由于FFT输出值的每个点对应一个频率点,所以输出的就是信号的频谱。

高抽取滤波的运算量和存储量一般都比较小,比如CIC抽取滤波器的滤波系数都是1,不需要乘法运算,所需的存储空间等于抽取比D;而后续的FFT只需对M=N/D点数据进行FFT变换,数据存储量和运算量都远低于传统的N点FFT,数据存储量和运算量的大幅度降低必将导致大幅度减少处理时间。上述内容均说明,基于数字下变频的FFT技术比传统的FFT技术在提高系统的实时性方面具有更大的优越性。

3 数字下变频FFT在频谱分析仪中的实现

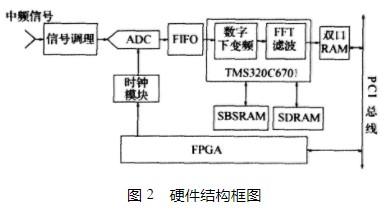

在某新型频谱分析仪中,基于数字下变频的FFT技术得到成功实现,该技术是在基于TI公司DSP芯片TMS320C6701的数字信号处理系统中通过软件处理得以实现的。

图2是该数字信号处理系统的硬件结构框图。在该系统中,模拟中频信号由同轴电缆输入,经中频预滤波和ADC采样后,数据通过FIFO送给TMS320C6701。TMS320C6701主要是做基于数字下变频的FFT,其实现依据前面描述的实现原理来设计的。全局控制器FPGA主要是完成整个系统的扫描控制。当FPGA在收到采样指令后启动ADC采集,采集的数据直接缓存在FIFO中。当FIFO数半满时,将触发TMS320C6701外部中断和内部DMA中断,DMA处理程序将FIFO数据送入DSP的外部SDRAM数据存储器。当数据足够时,TMS320C6701对采样数据进行数字下变频和FFT处理,把结果转化成主机能接收的数据格式送人双口RAM,主-机则实时从双口RAM读取频谱数据,转换成数据显示在屏幕上。此外,主机则把控制指令送到双口RAM,通过HPI中断通知DSP接0收。

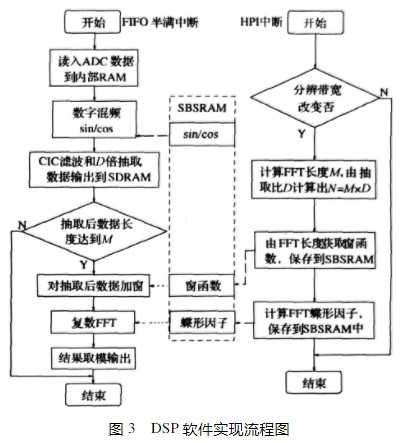

图3是其DSP基于中断响应的软件实现流程图,该DSP软件主要由2个中断处理程序共同完成。其中,2个中断分别为HPI中断和FIFO半满中断。

主机的HPI中断通过访问DSP的HPI接口产生,该中断用来通知DSP得到当前频谱分析仪的分辨率,并根据式(2)由分辨率、窗函数-3 dB带宽因子K和采样率计算出FFT长度M,并由预先设定的抽取比D计算出采样数据长度N=M×D。

FPGA控制产生的ADC采样FIFO半满中断,则先让DSP完成数据采集、软件数字下变频;当所采集的数据足够时,再进行FFT处理(此时FPGA控制ADC停止采样)。由于DSP片内数据空间较小,ADC采样数据先保存在内部RAM,经CIC抽取滤波后,其输出数据和FFT处理数据都存放在外部SDRAM空间,而SBSRAM是参数存放和传递的空间,里面包括数字本振(该数据是在开机时由主机加载)、窗函数和FFT蝶形因子等参数。

4 处理时间比较与分析

本文选择在相同ADC采样数据下将传统FFT和数字下变频FFT 2种方法的处理时间进行对比测试,在测试中选择的采样数据量为64K,基于数字下变频的FFT方法选择的抽取比为64,所有FFT数据访问都是在片外SDRAM,测试结果如表1所示。

由表1可以知,基于数字下变频的FFT方法总共耗时为1.92+0.95=2.87 ms,远小于传统法的320.7 ms。传统法处理时间过长,主要是因为FFT算法本身的大数据量运算耗时较多,而且DSP访问外部SDRAM较之片内耗时更多。64K数据都在外部SDRAM,而FFT算法需要多次对数据进行读写操作,这必然导致整个处理中的数据访问时问增加,从而引起整个处理时间增加。相比而言,基于数字下变频的FFT方法只需进行1K点的FFT;而且CIC抽取滤波处理是在片内进行的,均是简单的加法运算,整个处理时间自然就少多了。

5 结 论

本文分析了基于数字下变频的FFT技术的具体方法,在实现宽带频谱分析和窄的分辨率方面,该方法比传统的FFT更能有效降低整个处理过程的运算量、存储量和处理时间。实际应用证明:在某新型频谱分析仪中,通过在单片DSP里的软件实现,并由处理时间对比测试可知,该方法较之传统FFT方法能大幅度提高系统的实时性。

-

扫频式频谱分析仪的技术原理和应用场景2025-02-14 524

-

频谱分析仪在无线通信中的应用2024-11-27 1730

-

无线通信频谱分析仪的技术原理和应用场景2024-11-07 3759

-

实时频谱分析仪FFT功能如何采集信号?2024-01-19 2291

-

频谱分析仪的使用方法2023-09-19 3734

-

虹科实时频谱分析仪新手使用手册2022-10-17 1820

-

带你走进频谱分析仪“世界”,了解频谱分析仪!2022-06-16 17594

-

基于软件定义无线电的实时频谱分析仪功能概述(二)硬件架构2021-11-10 1193

-

求一款应用于数字化中频频谱分析仪的数字下变频电路2021-04-15 1338

-

什么是频谱分析仪2019-07-02 2921

-

你不知道的频谱分析仪基本原理有哪些呢?---安泰频谱分析仪维修2018-04-24 2782

-

FPGA在软件无线电中的工程应用之数字上下变频篇2010-02-09 523

-

基于DSP技术的虚拟式FFT频谱分析仪2009-06-22 1010

全部0条评论

快来发表一下你的评论吧 !