CAT24C64 64Kb I²C CMOS串行EEPROM技术深度解析

描述

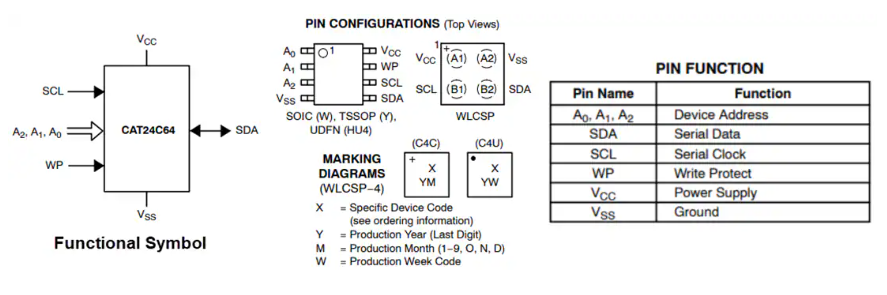

安森美 (onsemi) CAT24C64 64Kb I^2^C CMOS串行EEPROM在内部为每个8位安排有8192个字。这些EEPROM具有32字节页面写入缓冲区,并支持标准(100kHz)、快速(400kHz)和快速增强(1MHz)I^2^C协议。外部地址引脚允许同一总线上最多连接八个CAT24C64设备。安森美 (onsemi) CAT24C64提供SOIC、TSSOP、UDFN 8焊盘和超薄WLCSP 4焊球封装。

数据手册:*附件:onsemi CAT24C64 64Kb I2C CMOS串行EEPROM数据手册.pdf

特性

- 支持标准、快速和快速增强I^2^C协议

- 1.7V至5.5V的电源电压范围

- 32字节页面写入缓冲器

- 硬件对整个存储器进行写保护

- I^2^C总线输入(SCL和SDA)上的施密特触发器和噪声抑制滤波器

- 低功耗CMOS技术

- 1,000,000个编程/擦除周期

- 100年数据保留期

- 工业和扩展温度范围

- SOIC、TSSOP、UDFN 8焊盘和超薄WLCSP 4焊球封装

- 无铅、无卤/无BFR,符合RoHS标准

引脚配置与功能

CAT24C64 64Kb I²C CMOS串行EEPROM技术深度解析

一、核心架构与特性总览

1. 存储器结构

- 容量组织:64Kbit存储空间,内部划分为8192个字,每个字8位

- 页写缓冲:32字节页写缓冲区,支持高效批量写入

- 寻址能力:通过A0/A1/A2地址引脚可实现最多8个器件并联(除WLCSP封装)

2. 电气特性

- 宽电压范围:1.7V至5.5V工作电压

- 多速率支持:

- 标准模式:100kHz

- 快速模式:400kHz

- 快速增强模式:1MHz(限-40℃至+85℃)

- 低功耗设计:读取电流≤1mA,写入电流≤2mA

3. 可靠性指标

- 耐久性:1,000,000次编程/擦除周期(5V, 25℃)

- 数据保持:100年典型值

- 工作温度:工业级(-40℃至+85℃)/扩展级(-40℃至+125℃)

二、关键硬件设计要点

1. 引脚功能定义

| 引脚名称 | 功能描述 | 设计注意事项 |

|---|---|---|

| SCL | 串行时钟输入 | 需配置上拉电阻,支持三种速度模式 |

| SDA | 串行数据I/O | 开漏输出,需要外部上拉 |

| A0/A1/A2 | 器件地址选择 | 未连接时内部下拉至GND |

| WP | 写保护控制 | 高电平有效,悬空时内部下拉 |

2. 极限参数保护

- 电压容限:任意引脚对地电压-0.5V至+6.5V

- 瞬态保护:允许20ns内-1.5V至VCC+1.5V的瞬态过冲

- 存储温度:-65℃至+150℃

3. 电源管理特性

- 上电复位:集成POR电路,防止异常电源状态

- 待机模式:静态电流仅1μA(VCC≤3.3V)

三、通信协议深度解析

1. I²C总线时序规范

- 起始条件:SCL高电平时SDA由高变低

- 停止条件:SCL高电平时SDA由低变高

- 数据有效性:SCL高电平期间SDA必须保持稳定

2. 器件寻址机制

- 从机地址:固定前4位为1010,后3位由硬件地址引脚确定

3. 应答协议

- ACK响应:第9个时钟周期接收方拉低SDA

- 无应答:接收方保持SDA高电平

四、写操作模式详解

1. 字节写入模式

- 操作流程:起始条件→从机地址→高地址字节→低地址字节→数据字节→停止条件

- 写周期时间:tWR = 5ms(最大值)

2. 页写入模式

- 缓冲优势:最大32字节连续写入,单次写周期完成

- 地址回绕:页内地址自动递增,到达页尾时回绕至页首

3. 硬件写保护

- 保护触发:WP引脚拉高

- 保护时机:首个数据字节前的SCL下降沿采样

五、读操作模式分析

1. 立即读取

- 当前地址访问:从上次操作结束地址开始读取

- 终止条件:主机发出无应答后跟停止条件

2. 选择性读取

- 指定地址访问:先执行伪写入设置地址,再发起读取

3. 顺序读取

- 连续输出:内部地址自动递增,支持跨页读取

六、封装选型指南

1. 可选封装类型

- 传统封装:SOIC-8、TSSOP-8

- 微型封装:UDFN-8、WLCSP-4

2. WLCSP特殊限制

- 无地址引脚:仅响应000地址(CAT24C64C4xTR)

- 无写保护:WP功能不可用

- 防紫外线:禁止暴露在紫外线下,会导致数据丢失

七、噪声抑制与可靠性设计

1. 输入滤波

- 施密特触发器:SCL和SDA输入带噪声抑制滤波

- 瞬态滤波:可滤除≤100ns的噪声脉冲

2. 内部下拉特性

- 地址引脚:50μA下拉电流(VCC=5.5V)

- 功耗优化:输入超过阈值电压后转换为弱电流源

八、应用场景建议

1. 高密度存储配置

- 多器件并联:利用地址引脚扩展至512Kbit存储容量

2. 电源敏感系统

- 低功耗优势:适合电池供电设备

- 宽压适应性:兼容1.8V/3.3V/5V系统

3. 工业环境应用

- 温度适应性:支持严苛工业环境

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析 CAT24C02/04/08/16:I²C 串行 EEPROM 的卓越之选2026-04-15 162

-

STMicroelectronics M24C64X-DRE 64Kb I²C EEPROM技术解析与应用指南2025-10-15 1058

-

FM24C64 64KB的串行存储器中文手册2025-02-28 541

-

N24C64 EEPROM串行64-Kb I2019-08-01 1319

-

CAT24C64 EEPROM串行64-Kb I.2019-04-18 1685

-

2KB,4KB,8KB和16KB I2C串行CMOS,EEPROM,CAV24C02YE-GT32017-09-06 1703

-

64KB的串行CMOS EEPROM的CAV25640VE-GT32017-09-05 1156

-

CAT25640-64Kb的SPI串行CMOS EEPROM2010-03-04 564

全部0条评论

快来发表一下你的评论吧 !