深入解析ADC08B3000:高性能8位3GSPS A/D转换器的技术奥秘

电子说

描述

在电子工程师的设计世界里,A/D转换器是至关重要的组件之一。今天,我们将深入探讨德州仪器(TI)的ADC08B3000,这是一款8位、3GSPS的高性能、低功耗A/D转换器,它在众多领域都有着广泛的应用前景。

文件下载:adc08b3000.pdf

一、产品概述

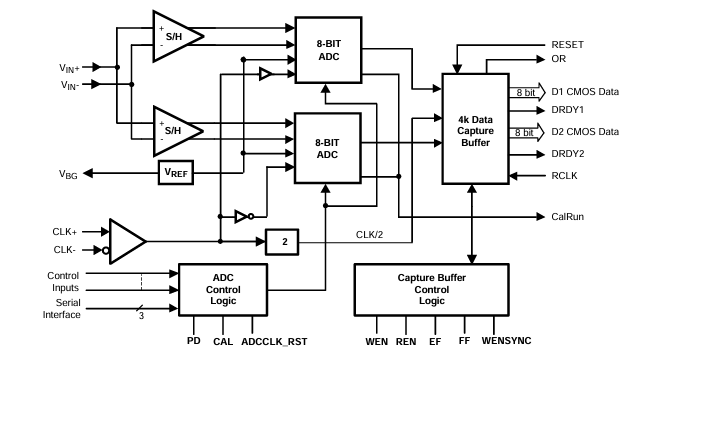

ADC08B3000采用单+1.9V ±0.1V电源供电,能够以高达3.4Gsps的采样率将信号数字化为8位分辨率。在3Gsps的采样率下,其典型功耗仅为1.6瓦,并且在整个工作温度范围内保证无漏码。该转换器独特的折叠和插值架构、全差分比较器设计、创新的内部采样保持放大器以及校准方案,使其在高达奈奎斯特频率的所有动态参数方面都表现出色。在748MHz输入信号和3GHz采样率下,可实现7.1的有效位数(ENOB),同时提供$10^{-18}$的码误差率。

二、关键特性与优势

(一)架构优势

ADC08B3000采用校准的折叠和插值架构,折叠放大器大大减少了比较器的数量和功耗,插值则减少了前端放大器的需求,降低了输入信号的负载并进一步降低了功耗。片上校准还减少了折叠架构中常见的积分非线性(INL)弯曲,从而实现了极快、高性能、低功耗的转换。

(二)校准功能

校准是ADC08B3000的重要特性之一。上电时会自动进行校准,用户也可以通过命令随时触发校准。校准过程会微调100Ω模拟输入差分终端电阻,最小化满量程误差、失调误差、差分非线性(DNL)和积分非线性(INL),从而最大化信噪比(SNR)、总谐波失真(THD)、信噪失真比(SINAD)和有效位数(ENOB)。需要注意的是,在时钟相位调整启用后启动校准,内部时钟会在校准序列开始时停止运行,因此在进行命令校准之前,要确保时钟相位使能位关闭或电阻修整禁用位打开。

(三)输出格式与缓冲器

输出格式为偏移二进制,逻辑为LVCMOS。该转换器包含一个4K捕获缓冲器,数据可通过两个8位LVCMOS输出总线输出,输出速率高达200MHz。捕获缓冲器的存在使得采样和处理任务可以分离,输入信号可以高速采样,采集的样本可以以较慢的速率卸载进行数字处理。

(四)时钟特性

ADC08B3000需要交流耦合的差分时钟信号驱动,采样时钟具有可选的占空比校正功能,默认启用,可支持占空比为20% - 80%的信号源。为了帮助用户从捕获缓冲器中读取数据,还提供了RCLK输入,它是一个自由运行的时钟,可与模拟输入采样时钟异步应用,最高运行频率可达200MHz。

(五)双边缘采样与双数据速率

为了实现3Gsps的采样率,该转换器使用两个ADC,一个在采样时钟的正边缘采样输入,另一个在负边缘采样,从而使每个采样时钟周期采样两次,整体采样率是采样时钟频率的两倍。此外,用户可以选择单数据速率(SDR)或双数据速率(DDR)输出,在非扩展控制模式下,允许引脚4浮空即可启用DDR时钟。

三、引脚与功能详解

(一)引脚配置

ADC08B3000采用128引脚的热增强型外露焊盘HLQFP封装,不同的引脚具有不同的功能,如串行接口时钟(SCLK)、边缘选择/双数据速率/串行数据(OutEdge/DDR/SDATA)、ADC采样时钟复位(ADCCLK_RST)等。在使用时,需要根据具体的功能需求正确连接和配置这些引脚。

(二)控制模式

该转换器有正常控制模式和扩展控制模式两种。在正常控制模式下,用户通过几个控制引脚完成设备的配置和控制;扩展控制模式则通过串行接口和一组6个内部寄存器提供更多的配置和控制选项。两种模式的选择通过引脚14(FSR/ECE)进行,且在设备运行时不建议动态切换。

(三)串行接口

在扩展控制模式下,ADC08B3000通过3引脚串行接口访问内部寄存器。串行时钟(SCLK)在其上升沿接受串行数据输入,无最低频率要求;串行数据(SDATA)输入需要特定的32位模式,包括固定头模式、寄存器地址和寄存器值。在使用串行接口时,要注意观察与SCLK相关的建立和保持时间,并且在ADC进行校准周期时,不要访问串行接口,以免影响设备性能。

四、电气特性与性能指标

(一)静态特性

包括积分非线性(INL)、差分非线性(DNL)、分辨率、失调误差、满量程误差等。INL和DNL反映了转换器的线性度,分辨率为8位且保证无漏码,失调误差和满量程误差会影响转换的准确性,校准过程可以有效减小这些误差。

(二)动态特性

如有效位数(ENOB)、信噪失真比(SINAD)、信噪比(SNR)、总谐波失真(THD)、无杂散动态范围(SFDR)等。这些指标衡量了转换器在动态信号处理方面的性能,在不同的输入频率下,各项指标会有所变化。例如,在748MHz输入信号和3GHz采样率下,ENOB可达7.1位,SNR为44.9dB。

(三)模拟输入与输出特性

模拟输入为差分输入,需要提供与$V_{CMO}$输出相等且跟踪其变化的输入共模电压。输入电容和电阻会影响信号的传输和处理,输出的共模电压和带隙参考电压也有相应的特性和要求。

(四)时钟特性

输入时钟的频率、占空比、高低时间等都会影响转换器的性能。ADC08B3000的时钟输入需要交流耦合的差分信号,且要保持在规定的电压范围内,同时要注意时钟的抖动和相位噪声,以避免抖动引起的噪声影响动态性能。

五、应用与设计注意事项

(一)应用领域

ADC08B3000适用于距离测距、测试与测量等领域,其高性能和低功耗的特点使其在这些应用中具有很大的优势。

(二)设计注意事项

- 电源与接地:电源供应要稳定,$V{A}$和$V{DR}$需要良好的旁路电容,每个电源引脚都要用单独的旁路电容去耦。建议使用单个接地平面,避免将接地平面分为模拟和数字区域,以减少数字噪声对模拟电路的干扰。

- 输入信号处理:模拟输入必须是差分信号,不建议使用单端信号。在直流耦合模式下,输入共模电压必须保持在$V_{CMO}$输出的±50mV范围内。选择驱动放大器时要注意其噪声、失真性能和增益,以满足应用需求。

- 时钟设计:时钟源要具有低均方根抖动,输入时钟线要尽量短,远离其他信号,并将其视为传输线处理。时钟信号的电平要在规定范围内,过高或过低的时钟电平都会影响转换器的性能。

- 热管理:由于转换器的功耗较高,需要注意热管理。要确保芯片的结温不超过130°C,可以通过将封装底部的外露焊盘与PCB上足够大的铜面积进行热连接来实现散热。

六、总结

ADC08B3000是一款性能卓越的A/D转换器,其独特的架构、丰富的功能和出色的电气特性使其在高速数据采集和处理领域具有很大的应用潜力。在设计应用时,电子工程师需要充分了解其各项特性和要求,注意各个环节的设计细节,以确保转换器能够发挥最佳性能。同时,要避免常见的应用陷阱,如未正确配置寄存器、输入信号超出范围、时钟抖动过大等问题。希望通过本文的介绍,能帮助大家更好地理解和应用ADC08B3000。你在使用类似A/D转换器的过程中遇到过哪些挑战呢?欢迎在评论区分享你的经验和见解。

-

深入解析PCM1803A:高性能立体声A/D转换器的技术奥秘2026-04-22 85

-

AD9699:高性能14位3GSPS模数转换器的深度解析2026-03-27 203

-

深入剖析ADC12081:高性能12位A/D转换器的技术解析2025-12-10 824

-

深入剖析ADC08L060:高性能8位A/D转换器的设计与应用2025-12-05 887

-

ADC081000:高性能低功耗8位、1GSPS A/D转换器的深度解析2025-12-03 734

-

ADC08D1000:高性能低功耗8位A/D转换器的设计与应用2025-12-02 821

-

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器2025-12-01 871

-

ADC08B200:高速8位A/D转换器的全方位解析2025-11-28 746

-

ADC08D1020:高性能8位A/D转换器的深度解析2025-11-27 705

-

ADC08B3000低功耗、高性能CMOS模数转换器数据表2024-07-17 513

-

ADC08B3000,pdf datasheet (8-Bi2009-10-10 636

全部0条评论

快来发表一下你的评论吧 !