ADS614X系列模数转换器产品资料

电子说

描述

在电子设计领域,模数转换器(ADC)的性能和功能对整个系统的表现起着关键作用。今天,我们将深入探讨德州仪器(TI)的ADS614X系列ADC,包括ADS6145、ADS6144、ADS6143和ADS6142,它们以其卓越的性能和丰富的特性,在众多应用场景中展现出强大的竞争力。

文件下载:ads6143.pdf

一、产品概述

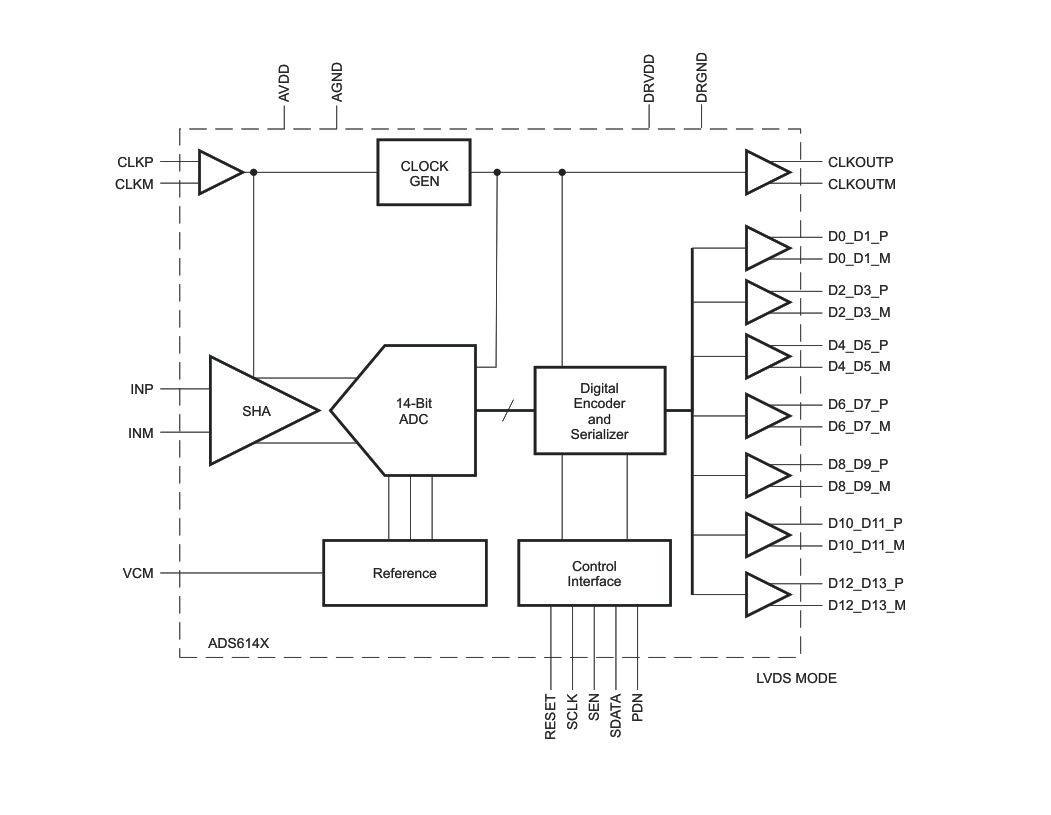

ADS614X系列是14位的ADC,具有高达125 MSPS的采样频率。该系列产品采用紧凑的32 QFN封装,将高性能与低功耗完美结合。内部的高带宽采样保持电路和低抖动时钟缓冲器,即使在高输入频率下也能实现高信噪比(SNR)和高无杂散动态范围(SFDR)。

特性亮点

- 高采样率:最高可达125 MSPS,满足高速数据采集需求。

- 14位分辨率:无丢失码,确保数据的准确性和完整性。

- 增益调节:具备3.5 dB的粗增益和最高6 dB的可编程细增益,可在SNR和SFDR之间进行权衡。

- 输出接口多样:支持并行CMOS和双数据速率(DDR)LVDS输出选项,适应不同的系统架构。

- 时钟兼容性强:支持Sine、LVCMOS、LVPECL、LVDS时钟输入,时钟幅度低至400 mVpp。

- 内部参考:内置参考,支持外部参考,无需外部去耦。

- 可编程输出:输出时钟位置和驱动强度可编程,方便数据采集。

应用领域

ADS614X系列广泛应用于无线通信基础设施、软件定义无线电、功率放大器线性化、测试测量仪器、高清视频、医学成像和雷达系统等领域。

二、技术细节剖析

电气特性

该系列ADC在不同采样频率下的电气特性表现出色。以ADS6145为例,在125 MSPS的采样频率下,其分辨率为14位,差分输入电压范围为2 Vpp,模拟输入带宽高达450 MHz。内部参考误差小,直流精度高,无丢失码,偏移误差和增益误差都在较小范围内。

在动态交流特性方面,SNR和SFDR在不同输入频率下都能保持较高水平。例如,在Fin = 10 MHz、0 dB增益时,SNR可达73.9 dBFS,SFDR可达90 dBc。这些特性使得ADS614X系列在处理复杂信号时能够提供准确的数字化结果。

数字特性

数字输入和输出的规格经过精心设计,以确保与各种数字系统的兼容性。在CMOS接口中,输出缓冲器电源(DRVDD)可在1.8 V至3.3 V的宽范围内工作,每个数据位在每个时钟周期以CMOS电压电平输出。在LVDS接口中,输出为LVDS电压电平,默认LVDS缓冲器输出电流为3.5 mA,可通过编程调整。

时序特性

时序参数对于确保数据的准确采集和传输至关重要。ADS614X系列的时钟传播延迟、输出时钟占空比、数据上升时间和下降时间等参数都经过严格设计和验证。在不同采样频率下,这些参数能够保证数据的稳定传输和正确采集。

三、设备编程模式

ADS614X系列提供了灵活的编程模式,可通过串行接口编程或并行接口控制来配置各种功能。

串行接口编程

使用串行接口编程时,需要先将内部寄存器复位到默认值,将RESET引脚保持低电平。SEN、SDATA和SCLK作为串行接口引脚,用于访问ADC的内部寄存器。通过在RESET引脚上施加脉冲或设置软件复位位(),可以实现寄存器的复位。

并行接口控制

通过并行接口控制时,将RESET引脚拉高(AVDD)。SEN、SCLK、SDATA和PDN作为并行接口控制引脚,可直接控制ADC的某些模式,如待机、输出格式选择、参考选择等。

四、应用设计要点

模拟输入

模拟输入采用基于开关电容的差分采样保持架构,具有良好的交流性能。为了获得最佳性能,建议采用差分驱动方式,以提高共模噪声抑制能力和偶次谐波抑制能力。同时,在每个输入引脚串联一个5-Ω电阻,以抑制封装寄生效应引起的振铃。

参考

ADS614X系列内置内部参考,无需外部组件。可通过编程选择内部或外部参考模式。在内部参考模式下,REFP和REFM电压内部生成,VCM引脚输出共模电压;在外部参考模式下,VCM引脚作为参考输入,通过内部缓冲和增益生成REFP和REFM电压。

时钟输入

时钟输入可以采用差分或单端驱动方式,建议采用差分驱动以减少共模噪声的影响。对于高输入频率采样,建议使用低抖动的时钟源,并进行带通滤波以减少抖动的影响。

电源管理

该系列ADC具有四种电源管理模式:全局掉电、待机、输出缓冲器禁用和输入时钟停止。通过串行接口或并行接口可以设置不同的电源管理模式,以满足不同的功耗需求。

数字输出接口

提供并行CMOS和DDR LVDS两种输出接口,可通过串行寄存器位或并行引脚进行选择。在CMOS接口中,需要注意输出时钟的使用和负载电容的匹配;在LVDS接口中,可通过编程调整LVDS缓冲器电流和内部终端电阻,以提高信号完整性。

五、总结与展望

ADS614X系列ADC以其高性能、高灵活性和低功耗的特点,为电子工程师提供了一个强大的工具。在实际应用中,我们需要根据具体的需求,合理选择和配置ADC的各种参数和功能,以实现最佳的系统性能。

随着电子技术的不断发展,对ADC的性能要求也越来越高。未来,我们期待德州仪器能够推出更多具有创新性的产品,进一步满足市场的需求。同时,作为电子工程师,我们也需要不断学习和掌握新的技术和方法,以应对日益复杂的设计挑战。

你在使用ADS614X系列ADC的过程中遇到过哪些问题?你对ADC的未来发展有什么看法?欢迎在评论区分享你的经验和见解。

-

ADS1241模数转换器产品资料2025-12-08 785

-

TI ADS614X系列14位ADC:高性能与灵活性的完美结合2025-11-27 785

-

ADS8881x模数转换器数据表2024-07-27 410

-

ADS1299-x模数转换器数据表2024-07-24 653

-

ADS126x 32位、38kSPS、精密模数转换器(ADC)数据表2024-07-17 723

-

ADS7x51同步采样模数转换器数据表2024-07-15 556

-

ADS1242模数转换器数据手册2024-06-29 731

-

高速率的逐次逼近模数转换器ADS8412是如何设计的?2021-04-14 2252

-

模数转换器ADS5287资料推荐2021-03-24 1229

-

ADS614X和ADS612X的英文原版数据手册(免费下载)2018-05-28 1063

-

ADS58X 16位模数转换器的详细原版资料免费下载2018-05-24 1119

全部0条评论

快来发表一下你的评论吧 !