TI ADS642X系列ADC:高性能与灵活性的完美结合

电子说

描述

在电子设计领域,模数转换器(ADC)的性能直接影响着整个系统的精度和稳定性。德州仪器(TI)的ADS6424、ADS6423和ADS6422(统称ADS642X)系列ADC,凭借其卓越的性能和丰富的功能,成为众多应用场景的理想选择。今天,我们就来深入探讨一下这款ADC的特点、应用以及设计要点。

文件下载:ads6422.pdf

一、产品概述

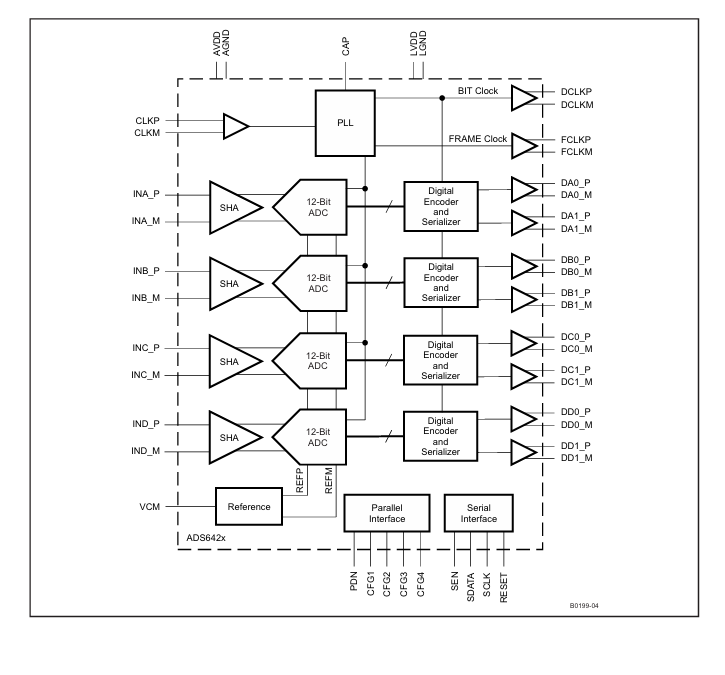

ADS642X是一系列高性能的12位、105/80/65 MSPS四通道A - D转换器。其采用串行LVDS数据输出,有效减少了接口线的数量,使得整个设备能够封装在一个紧凑的64引脚QFN(9 mm × 9 mm)封装中,大大提高了系统的集成密度。

二、产品特性

2.1 高精度与高分辨率

ADS642X具备12位分辨率,且无丢失码,能够提供精确的模数转换结果。同时,它采用了同时采样和保持技术,确保了多通道输入信号的同步采集。

2.2 增益灵活配置

该系列ADC提供3.5dB的粗增益选项,可在对SNR影响较小的情况下提高SFDR性能。此外,还具备可编程的精细增益选项,可在1dB步长下从0dB调整到6dB,进一步优化系统性能。

2.3 丰富的时钟输入支持

ADS642X支持多种时钟输入类型,包括Sine、LVCMOS、LVPECL和LVDS,且时钟幅度可低至400mVPP,为不同的应用场景提供了更多的选择。

2.4 内部参考与外部参考兼容

ADS642X内置了参考电压,同时也支持外部参考模式,用户可以根据实际需求灵活选择。而且,参考电压无需外部去耦电容,简化了设计。

2.5 低功耗设计

该系列ADC具有多种功耗模式,包括全局掉电、通道待机和输入时钟停止模式,可有效降低系统功耗。例如,在全局掉电模式下,典型功耗可降至约77mW。

三、应用领域

ADS642X的高性能和灵活性使其适用于多种应用场景,包括基站中频接收器、分集接收器、医学成像和测试设备等。

四、技术细节分析

4.1 模拟输入设计

ADS642X的模拟输入采用了基于开关电容的差分采样和保持架构,这种拓扑结构在高频输入时仍能保持良好的AC性能。为了获得最佳性能,模拟输入必须采用差分驱动方式,以提高共模噪声抑制能力和偶次谐波抑制能力。同时,建议在每个输入引脚串联一个5Ω的电阻,以抑制封装寄生效应引起的振铃。

4.2 时钟输入与缓冲增益

时钟输入对ADS642X的性能至关重要。为了减少时钟抖动对性能的影响,建议使用差分时钟输入,并选择低抖动的时钟源。此外,时钟缓冲器具有可编程增益,可根据需要调整时钟幅度,以支持极低的时钟幅度输入。

4.3 数字输出接口

ADS642X提供了多种数字输出接口选项,包括1线和2线接口,以及不同的序列化和位时钟模式。用户可以根据实际需求选择合适的接口选项,以满足不同的采样频率和数据速率要求。

4.4 增益设置与性能优化

通过合理设置粗增益和可编程精细增益,用户可以在SFDR和SNR之间进行权衡,以获得最佳的系统性能。例如,在需要提高SFDR性能的应用中,可以选择3.5dB的粗增益设置。

五、设计注意事项

5.1 电源供应与布局

在设计过程中,要确保AVDD和LVDD电源的稳定性。建议使用单独的电源为模拟和数字部分供电,以隔离数字开关噪声对敏感模拟电路的影响。同时,合理的PCB布局对于减少信号干扰和提高系统性能也非常重要。

5.2 时钟与数据布线

为了确保可靠的数据捕获,建议在PCB上尽量减少时钟和数据线路的相对偏移。特别是位时钟、帧时钟和输出数据线的布线,要保证它们之间的相对偏移最小。

5.3 测试与验证

在实际应用中,建议使用ADS642X提供的测试模式,如DESKEW和SYNC测试模式,来验证接收器的捕获时钟边缘是否正确定位,以及并行数据是否与帧边界对齐。

六、总结

TI的ADS642X系列ADC以其高性能、高灵活性和低功耗的特点,为电子工程师提供了一个强大的设计工具。无论是在通信、医疗还是测试设备等领域,ADS642X都能满足不同的应用需求。在设计过程中,我们需要充分考虑其技术细节和设计注意事项,以确保系统的稳定性和可靠性。希望通过本文的介绍,能帮助大家更好地了解和应用这款优秀的ADC产品。

你在使用ADS642X系列ADC的过程中遇到过哪些问题?或者你对这款产品有什么独特的见解?欢迎在评论区留言分享!

-

AD7621 16位ADC:高性能与灵活性的完美结合2026-04-01 604

-

AD1974音频ADC芯片:高性能与灵活性的完美结合2026-03-29 433

-

探索PCM186x系列音频ADC:高性能与灵活性的完美结合2026-01-30 654

-

探索PCM3120-Q1音频ADC:高性能与灵活性的完美结合2026-01-29 562

-

TAA3020音频ADC:高性能与灵活性的完美结合2026-01-28 474

-

TI ADS614X系列14位ADC:高性能与灵活性的完美结合2025-11-27 691

全部0条评论

快来发表一下你的评论吧 !