采用Flash存储器实现TMS320VC5410 DSP对多用户代码加载的方法研究

描述

引 言

在TMS320C54X系列DSP系统的开发中,由于DSP片内只有ROM和RAM存储器,如要将用户代码写入ROM中,必须要由DSP芯片厂家来完成;但这样做用户就不能再更改代码,很不实用。由于RAM在DSP掉电后不能再保存数据,因此,常常利用EPROM、Flash等一些外部存储器来存放用户代码。在DSP上电工作后,利用DSP提供的boot机制,再将程序下载到DSP RAM中运行。如果使用EPROM外部存储器存放用户代码,需要用代码转换工具将用户代码转换为二进制目标文件,然后用编程器将其烧写进EPROM;而如果使用Flash存储器存放用户代码,则可直接使用DSP仿真器和CCS(Code Composer Studio )仿真环境进行在线编程,使用灵活方便,不再需要其它编程设备。在某一以太网通信系统中,我们就采用Flash存储器来实现多份用户代码的有选择加载。下面就以此系统为例介绍对TMS320VC54X DSP的一种用户代码加载的方法。

1、系统构架

此通信系统基于802.3以太网标准,用以实现各终端之间的话音和其它数据的通信,以及实现局域网内终端与外界的话音和数据通信。为节约开发成本,提高系统的可扩展性、通用性和灵活性,我们对每个网内终端采用同样的硬件架构,通过使用不同的软件代码而使其实现不同的功能,发挥不同的作用。

每一通信终端由2块DSP芯片、1块网卡、1块CPLD和1块FPGA以及Flash存储器等器件组成可扩展的基本结构。其中,以TMS320VC5410 DSP作为主CPU,负责系统的逻辑控制和一般数据传输;以MS320VC5416 DSP作为从CPU,负责话音的编解码和回声消除、语音检测等工作。2块DSP之间通过主机接口(HPI)进行通信。为了实现代码的有选择下载,可由FPGA配置一端口作为拨码开关,使用户通过调节拨码开关,可以有选择地下载存储于Flash中的用户代码,其结构如图1所示。

配置拨码开关是为了扩充系统的功能,以实现一个硬件平台的多种用途。我们可以将实现不同功能的多份用户代码都写入Flash存储器中存放,通过硬件拨码开关的设置,选择其中一份用户代码下载执行。在系统上电加载用户代码时,系统先从Flash下载FPGA配置程序,然后通过FPGA读出拨码开关的值,再根据此值从Flash中选择对应的5410 DSP用户代码加载;而5416 DSP的用户代码加载是在5410代码加载完成,启动运行后由5410程序从Flash中读出相应的5416代码,再通过HPI加载到5416的,以此实现5416 DSP的代码加载与启动。

2、M29W800AB Flash存储器介绍及使用

在此系统中,我们选用的是M29W800AB Flash存储器,其容量为512K16位, 分为16页,每页32K。其中,第0页有4个模块:0x00~0x1fff、0x2000~0x2fff、0x3000~0x3fff、0x4000~0x7fff。其余各页,每页为1个模块,共有19个模块。

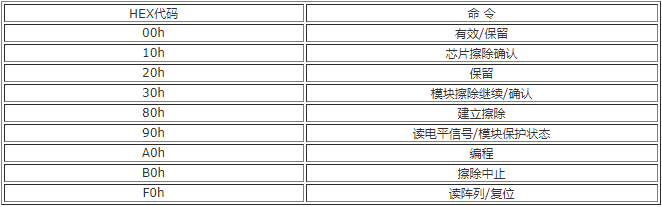

对Flash的操作要靠写入一系列特定的地址和数据序列来完成。在每次对Flash写入之前,要对其原来的内容进行擦除。Flash的擦除包括块擦除和芯片擦除两种。块擦除是对一个模块进行擦除,芯片擦除是擦除整个Flash的内容。因此,对Flash的操作,是以模块为基本单元的。对Flash的操作由指令决定,其必须满足Flash的时序要求,每条指令需要1~6个不等的指令周期。主要操作指令包括读数据指令、编程指令、复位指令、自动选择指令和擦除指令。每个指令周期由一个命令构成,每个命令代码所执行的任务如表1所列。

表1 Flash的命令说明

下面以M29W800AB Flash的块擦除指令为例,具体说明Flash的操作时序:块擦除指令需要6个总线周期,先以2个解锁周期开始,然后是1个擦除建立周期,接下来又是2个解锁周期,最后是1个擦除确认周期,其指令时序如表2所列。

表2 Flash擦除指令说明

其C语言程序设计代码如下:

#define flash ((volatile unsigned int*)0x8000)

Block_Erase(ADDR){

flash[0x5555] = 0x00AA;

wait(1000);

flash[0x2AAA] = 0x0055;

wait(1000);

flash[0x5555] = 0x0080;

wait(1000);

flash[0x5555] = 0x00AA;

wait(1000);

flash[0x2AAA] = 0x0055;

wait(1000);

flash[ADDR] = 0x0030;

}

需要注意的是,Flash相对于DSP来说是慢速设备,编程时,对Flash的访问需要有足够的延时等待。对其它指令这里就不一一介绍了。要了解更多内容,可参考具体的Flash存储器手册。

3 、引导装载

TMS320VC5410和TMS320VC5416片内ROM中固化有TI公司的引导装载(Bootloader)程序,用于在上电复位时把用户代码从外部存储器引导到片内RAM中运行。引导程序是在一些片内固化的一个程序,它负责上电时初始化存储器。换句话说,它将程序从非易失性存储器(如Flash存储器)中调入系统的存储器中。其提供的片内引导模式有: HPI(主机接口)引导、并行EPROM引导、并行I/O引导和串行口引导等。下面先介绍这两块芯片的上电引导过程。

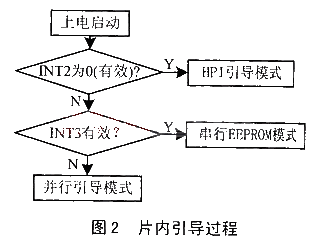

DSP上电复位后,先检测其MP/MC引脚,如果MP/MC=“0”,表示使用片内ROM引导。此时,DSP从0xFF80处开始执行TI的片内引导程序。进入引导程序后,HINT引脚变为低电平,然后开始检测INT2是否为低电平(有效)。如有效,则进入HPI引导方式;否则,检测INT3引脚。如有INT3请求中断,则进入串行引导方式;否则,就进入并行引导方式。在本系统中,我们采用TI公司提供的Bootlooder程序进行引导装载,为此,应将MP/MC引脚接低电平。引导程序流程如图2所示。

3.1 HPI模式实现TMS320VC5416的程序加载

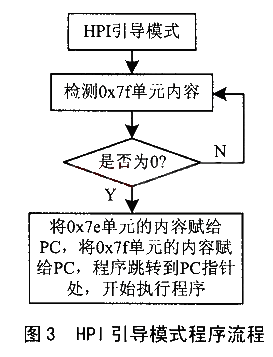

按以上设计,5416DSP的程序加载采用HPI(主机接口)模式。对于HPI引导模式,必须将HINT和INT2引脚连接在一起,以保证Bootloader程序能检测到INT2有效。当检测其为低电平时,进入HPI引导方式。主处理器5410启动运行后,5410程序从Flash中下载5416程序,通过5410与5416之间的HPI写入5416 RAM。在将程序写入5416时,要按照5416程序的cmd文件配置,将从Flash中读出的代码写入5416程序空间的代码段。写完代码后,还应将5416代码的起始地址写入5416的0x7f单元,将0写入0x7e单元,起始地址可在CCS仿真环境中编译5416代码后看出,此时PC所指向的位置就是代码的起始地址。这是因为,当5416进入HPI引导方式后,Boodloader程序开始检测0x7f单元的内容(0x7e和0x7f两单元内容在Boodloader程序开始执行时就清零)。当检测到其内容不为零时,即将0x7e的内容赋给XPC,将0x7f的内容赋给PC,程序跳转到PC所指向位置执行用户代码。这样就实现了从片5416的程序加载启动。图3是HPI模式加载用户代码的流程。

3.2 并行加载模式实现TMS320VC5410的程序加载

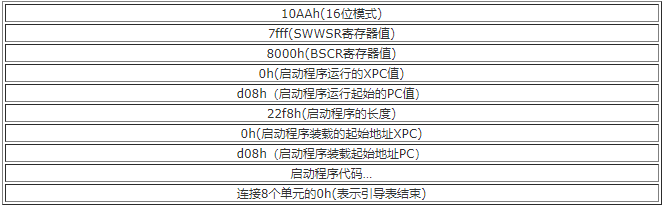

5410主处理器的用户代码加载采用并行模式加载。在本系统中,有多份5410用户代码存储于Flash中。系统上电后,先要从Flash中下载FPGA配置代码,然后读出拨码开关的值,再选择相应的用户代码下载,完成后,跳转到用户代码的入口地址开始执行用户代码。为此,需要设计一启动程序以实现以上功能。启动程序的内容包括下载FPGA配置代码,读拔码开关值,并根据此值选择下载相应的5410用户代码到其cmd文件配置的相应程序空间。完成后,跳转到用户代码起始地址。代码的起始地址通过CCS仿真环境编译后获得,启动程序的下载运行,则要依靠TI的片内引导程序,采用16位并行模式引导加载,需要构建引导表。所谓引导表就是引导程序要调入的代码。引导表中除了包括源代码之外,还包含一些附加信息。这些信息指导引导程序的具体执行过程。因此,可以说引导表是由程序代码和一些附加信息组成的一种数据结构。在这里,我们需要用启动程序构建引导表,并将引导表也写入Flash中。

在此系统中,Flash存储器映射为DSP的0x8000~0xffff数据空间。对Flash操作时,首先要选择页,每一页都对应为DSP的0x8000~0xffff地址的数据空间。需要注意:除了将引导表写入Flash外,还应将引导表的起始地址(对于DSP处理器而言的地址,如果在Flash中为0,则对DSP即为0x8000)写入Flash第一页的最后一个单元(0x7fff单元),即DSP存储空间的0xFFFFh单元。引导程序进入并行加载模式后,将查询数据空间的0xFFFFh单元,直到读入一个有效的地址数据。此数据为用户引导表的入口地址。这时,引导程序就跳转到Flash中的用户引导表开始执行。需要注意的是,对于不同型号和厂家的Flash,其引导表的格式和内容是不同的。下面就M29W800AB Flash引导表的格式及我们所配置的内容说明如下:

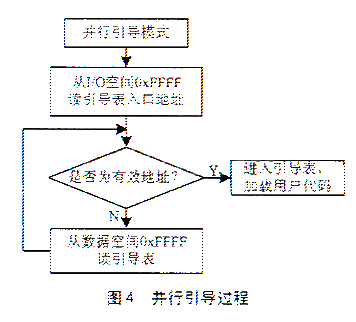

程序根据引导表的内容将用户代码下载到指定的程序空间中,并将指定的程序入口地址值赋给PC,使程序从此处开始执行,从而完成5410 DSP的引导启动。并行引导流程如图4所示。

在系统的实际调试过程中,通过HPI加载5416代码时,要注意5410和5416的时钟要匹配。一般来说,要求从片时钟为主片时钟的1.25倍以上。在此系统中,系统基准时钟为8MHz,5410启动时钟设为8MHz,5416设为10倍频80MHz。

本系统最大的优点是实现了一机多用,扩展了系统的功能,增强了系统的灵活性和通用性,在实际应用中已取得了良好的效果。

责任编辑:gt

-

求一种基于TMS320VC5410的会议电话解决方案2021-05-28 1376

-

TMS320VC5410_Fixed-Point_Digital_Signal_Processor2016-01-15 780

-

从TMS320VC549到TMS320VC5410的移植2014-09-23 3568

-

TMS320VC5410芯片电源及复位电路设计2011-08-05 1657

-

基于TMS320VC5410和SLE5542型IC卡的DES2010-12-13 2422

-

TMS320VC5410A DSP Silicon Errata2010-12-12 847

-

基于TMS320VC5409 DSP的闪烁存储器并行引导装载2009-11-02 1913

-

TMS320C5410烧写Flash实现并行自举引导2009-06-16 1550

-

TMS320VC5410的BOOT设计与实现?2009-05-14 1381

-

TMS320VC5410的McBSP串行接口技术与程序设计2009-05-13 697

-

基于TMS320VC5410的实时信号处理系统的设计2009-05-05 1146

-

TMS320VC5402 的Flash并行Bootloade2009-04-15 712

-

TMS320VC5410 pdf datasheet2008-08-07 602

全部0条评论

快来发表一下你的评论吧 !