基于DSP和ADC技术实现高速缓存和海量缓存的方案研究

描述

1、引言

高速数据采集系统目前已在雷达、声纳、软件无线电、瞬态信号测试等领域得到广泛应用。它的关键技术是高速ADC技术、数据存储与传输技术和抗干扰技术。本文在分析了高速多通道数据采集系统中存储子系统的性能要求和设计方案的基础上,提出了高速缓存和海量缓存方案,并将该方案成功地应用于DSP多通道超声信号采集与处理系统中。

对高速多通道采样数据存储的性能要求:一是高速性,现在高速数据采集中所用的ADC已达到几十甚至几百MSPS的水平,这就要求采样数据存储器的速度也要与之匹配,也就是采用高速缓存;二是大容量,其原因是多通道高速数据采集会产生巨大的数据流。一个4通道40MHz采样率16位精度数据采集板并行采样0.1s将产生32MB的数据量,所以,通常需要海量缓存来存储采样数据。

2、高速缓存的实现

通常构成高速缓存的方案有三种:

第一种是FIFO(先进先出)方式。FIFO存储器就象数据管道一样,数据从管道的一头流入、从另一头流出,先进入的数据先流出。FIFO具有两套数据线而无地址线,可在其一端写操作而在另一端读操作,数据在其中顺序移动,因而能够达到很高的传输速度和效率,且由于省去了地址线而有利于PCB板布线。缺点是只能顺序读写数据,因而显得比较呆板,而且大容量的高速FIFO非常昂贵;

第二种是双口RAM方式。双口RAM具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰,并可将采样数据从一个端口写入而由DSP从另一个端口读出。双口RAM也能达到很高的传输速度,并且具有随机存取的优点,缺点是大容量的高速双口RAM很难得且价格昂贵;

第三种是高速SRAM切换方式。高速SRAM只有一套数据、地址和控制总线,可通过三态缓冲门分别接到A/D转换器和DSP上。当A/D采样时,SRAM由三态门切换到A/D转换器一侧,以使采样数据写入其中。当A/D采样结束后,SRAM再由三态门切换到DSP一侧以便DSP进行读写。这种方式的优点是SRAM可随机存取,同时较大容量的高速SRAM容易得到且价格适中,缺点是切换控制电路比较复杂,且只能由A/D转换器和DSP分时读写。

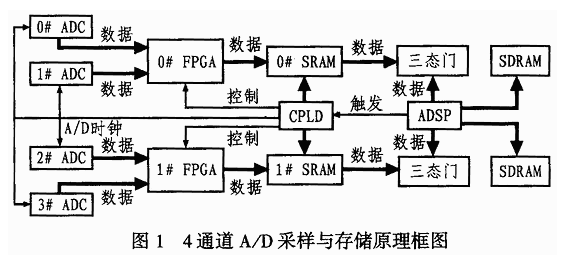

综合考虑以上三种高速缓存方案的性能、价格和实现方便性后,笔者选用第三种方案(即高速SRAM切换方式)来构成A/D采样高速缓存。系统的采样与存储部分的原理框图如图1所示。

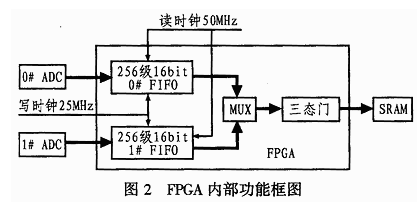

图1中,SRAM选用IS61LV25616-10T,容量为256k16bit,访问速度为10ns,使用两片即可构成256k32bit的高速缓存。当一轮采样开始时,DSP发出触发信号给CPLD,后者对50MHz晶振时钟二分频后得到25MHz采样时钟提供给4路A/D转换器AD9225,同时对4路超声信号进行25MHz、12bit的A/D转换。转换结果分成两个完全一样的数据通道进行处理,每个数据通道处理两路A/D转换结果,每个数据通道包含一片FPGA(现场可编程门阵列)、一片SRAM及其后的数据三态门等电路。FPGA可接收两路A/D转换结果并在其内部进行复用,以将其变成一路50MHz、12bit的数据流送入IS61LV25616缓存。FPGA完成数据通道复用的原理如图2所示。

FPGA选用EP1K50,它的逻辑门数为5万门,内含10个EAB(嵌入阵列块)。每个EAB实际上是4kbit的RAM,可以用来构造FIFO、双口RAM等。本系统应用两块EAB构成了两个25616bit的FIFO,因而可将两路A/D转换结果分别送入两个FIFO,然后在FPGA的输出端将两个FIFO中的数据交替地读出写入IS61LV25616,每个FIFO每次读出128个采样数据。A/D转换器的输出为12位数据,而FPGA的片内FIFO和片外IS61LV25616的数据字宽都为16位。在存储、传送时,将高4位补0即可。两路A/D采样速度都为25MHz,复用后输出的速率为50MHz,这个速度对于IS61LV25616和EP1K50都是完全可以达到的。FPGA的作用除了构造FIFO以实现数据通道复用外,还可以作为协处理器由板上DSP控制来进行一些简单高效的数据预处理(如插值、取平均、FIR滤波等)。同时可使用EDA工具MAX+PLUSⅡ10.0来对EP1K50的逻辑算法进行设计、编译并仿真,然后下载到EP1K50中实现预定功能。

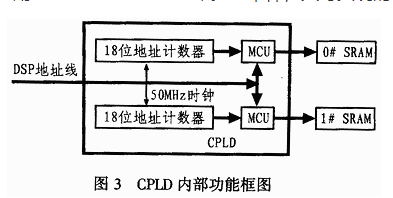

除了FPGA外,系统还采用了一片CPLD(复杂可编程逻辑器件)来控制采样。前者主要用于数据通道对A/D采样结果进行缓冲复用以及预处理,后者则负责产生A/D采样时钟以及作为地址计数器产生地址并提供给两片IS61LV25616以便存入A/D采样结果等。CPLD不象FPGA那样能完成较复杂的逻辑功能和信号处理算法,但是它具有更高的速度,且管脚到管脚具有固定一致的时延,因而在设计调试时容易获得简单可靠的定时关系,适于实现高速计数器、触发器、译码器等定时要求比较严格的场合。本系统使用MAX7128AE来控制采样,其可实现的功能如图3所示。

MAX7128AE可用于实现两个18位地址计数器,它具有地址总线开关切换功能,在A/D采样期间能以25 MHz的频率进行地址计数以作为高速缓存的地址线。当一轮A/D采样结束后,系统可将高速缓存的地址总线切换到DSP的地址总线,然后由DSP读取高速缓存中的A/D转换结果并进行处理。高速缓存IS61LV25616的数据总线一方面连到FPGA以便在采样期间接受复用的A/D转换结果;一方面则通过三态门连到DSP的数据总线以便在采样结束后由DSP读取采样数据。

3、海量缓存的设计实现

本系统使用了两片256k16bit容量的SRAM作为高速缓存,系统中的4个通道可同时存储每通道128k点采样数据。在25MHz的采样频率下,一次可采集存储5ms多的波形数据。对于超声信号的单次发射/接收来说,这种采样时间长度已经足够了,但是对于多批次采样数据的存储就比较困难了。若要通过PCI总线、USB接口等快速通讯方式将采样数据传到主机进行处理或存入硬盘,则应满足实时传输采样数据所需要的巨大总线带宽。以25MHz、12bit采样精度为例,4个通道同时采样将产生150MB/s的数据流,这对于任何总线来说都难以做到。解决的办法是在数据采集板上采用DSP对采集的数据进行预处理,以使处理后的数据量大大减少,然后再上传给主机以减轻总线传输压力和主机处理负担,从而避免数据通讯瓶颈。这种由板上DSP执行计算密集型任务并由上位主机进行调度管理的分布式处理机制可广泛用于许多高速数据采集与处理系统中。而为板上DSP配备大容量内存来作为它的程序和数据存储器是十分必要的。考虑到本系统所用DSP的结构特点和大容量采样数据的存储需要,笔者选用SDRAM作为板上海量内存。

系统中的DSP为Analog Devices公司的ADSP-21065L,这是一款性价比很高的32位浮点DSP。其峰值浮点运算速度为180M FLOPS,片内带有68kB的RAM,可用于程序或数据内存,片外数据总线为32位,片外地址总线为24位,具有4个片选信号输出,每个片选信号的寻址空间可达64MB,另外,它还具有多个高速同步串口以及强大的DMA功能。而最有特色的一点是其内部集成了一个SDRAM控制器,因此能够直接驱动外部SDRAM。通常SDRAM的控制是比较复杂的,需要按时序规定驱动它的行、列选通线并分时提供行、列地址,另外还要定时刷新。一般是由专门的SDRAM控制器对其操作,或采用FP-GA设计SDRAM控制器,但这都会增大系统的复杂度。而ADSP-21065L能直接驱动和控制片外SDRAM,使用时只要在程序中设置好相关的寄存器,然后用一条指令启动SDRAM的上电时序即可。此后程序对SDRAM的访问操作都是透明的,可象访问普通片外SRAM一样访问它,因此非常方便,故可使用大容量(可达64MB)高速廉价的SDRAM芯片作为ADSP-21065L的海量片外存储器。本系统使用两片4M16bit的SDRAM芯片HY57V641620来构成16MB的海量缓存(参见图1)。这样,16MB的存储容量如果都用来转存采样数据的话,可以存储4个通道同时采集的2M点数据,在25MHz的采样率下可达到0.08s的总记录时间,这对于本系统而言已经足够了。而且通过选用更大容量的SDRAM芯片还可方便地将海量缓存的容量扩充到32MB、64MB。

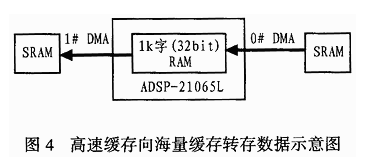

为了将多次A/D采样数据从高速缓存转送到海量缓存,如果让ADSP-21065L用指令的方式从片外高速缓存中读取采样数据,然后写入片外海量缓存,将会大量占用ADSP的运行时间,而且传输速度也较慢。为此,采用ADSP的DMA功能进行传送。ADSP-21065L具有多个DMA通道(其中包括两个外部口DMA通道),因而可进行高速数据传输。它的外部口DMA通道本来就可以完成外存与外设之间的DMA传输,但是若二者之一是SDRAM则不行。所以,实际使用时一般通过ADSP-21065L的片内RAM来中转,然后再完成高速缓存到海量缓存的数据传输,具体做法如图4所示。

ADSP内部开设有1k32bit的RAM块构成中转区,可利用外部口DMA通道0进行A/D高速缓存到片内RAM的DMA传输,同时利用外部口DMA通道1来进行片内RAM区到海量缓存SDRAM的DMA传输。在60MHz的ADSP主频下,前者的DMA传输速度可达120MB/s,后者的DMA传输速度可达240MB/s。当外部口DMA通道0完成一次传输后,系统将启动外部口DMA通道1的DMA传输;而当后者的DMA传输完成后?系统将再次启动前者的DMA传输。如此循环下去,直至A/D高速缓存中的1MB采样数据都倒入SDRAM海量缓存为止,该过程大约需要13.1ms。

4、结论与改进

通过对高速数据采集系统中几种A/D采样高速缓存的实现方案进行对比分析,结合本系统的结构特点和性能要求,采用SRAM作为A/D高速缓存所构成的采集系统具有速度高、容量大、控制方便、价格适中等优点。选用高速、大容量、低价格的SDRAM作为海量缓存则可通过其外部口DMA通道将高速缓存中的采样数据倒入海量缓存。这种设计使系统的A/D采样存储兼具高速和海量的优点,同时具有很高的性能价格比。而其尚存的不足之处是:ADSP和A/D转换器通过切换总线方式分时访问高速缓存在一定程度上影响了系统的实时性。作为改进措施可以引入双体存储交替访问的方案,即再增加两片IS61LV25616做成一组高速缓存以和已有的两片IS61LV25616构成双体存储区。由于该方式中的ADSP和A/D转换器以乒乓方式交替访问这两组缓存,因此,ADSP和A/D转换器能并行工作而无需互相等待,从而提高系统的实时性。

责任编辑:gt

-

TMS320C6000 DSP高速缓存用户指南2024-12-17 373

-

高速缓存Cache介绍2023-09-07 506

-

STM32F7技术--高速缓存2023-08-01 564

-

使用STM32高速缓存优化性能和能效2022-11-21 451

-

高速缓存(cache)的工作原理是什么?高速缓存可分为哪几类2021-12-23 2565

-

怎样去实现一种基于DSP和ADC技术高速缓存和海量缓存?2021-06-26 1889

-

怎么利用异步FIFO和PLL结构来实现高速缓存?2021-04-30 1610

-

高速缓存/海量缓存的设计实现2020-12-04 1610

-

MRAM高速缓存的组成2020-11-06 2232

-

基于BCH算法的高速缓存纠检错方案研究2017-01-07 602

-

高速缓存(Cache),高速缓存(Cache)原理是什么?2010-03-26 7124

-

磁盘阵列的高速缓存2010-01-09 2891

-

C64x+ DSP高速缓存一致性分析与维护2010-01-04 1685

-

高速数据采集系统中高速缓存与海量缓存的实现2009-04-23 791

全部0条评论

快来发表一下你的评论吧 !