深入解析NCP81560:8 + 1相输出控制器的卓越性能与应用

电子说

描述

深入解析NCP81560:8 + 1相输出控制器的卓越性能与应用

在计算机CPU应用领域,电源管理至关重要。onsemi的NCP81560作为一款专为Intel的IMVP9.1 CPU优化的8 + 1相输出控制器,凭借其出色的性能和丰富的功能,成为了众多工程师的首选。今天,我们就来深入了解一下这款控制器。

文件下载:onsemi NCP81560 8+1相输出控制器.pdf

一、产品概述

NCP81560是一款双轨、八加一相降压解决方案,采用双边缘脉冲宽度调制(PWM)结合DCR电流感应技术,能对动态负载事件做出超快速初始响应,同时降低系统成本。此外,它还具备超低失调电流监测放大器,可通过可编程失调补偿实现高精度电流监测。

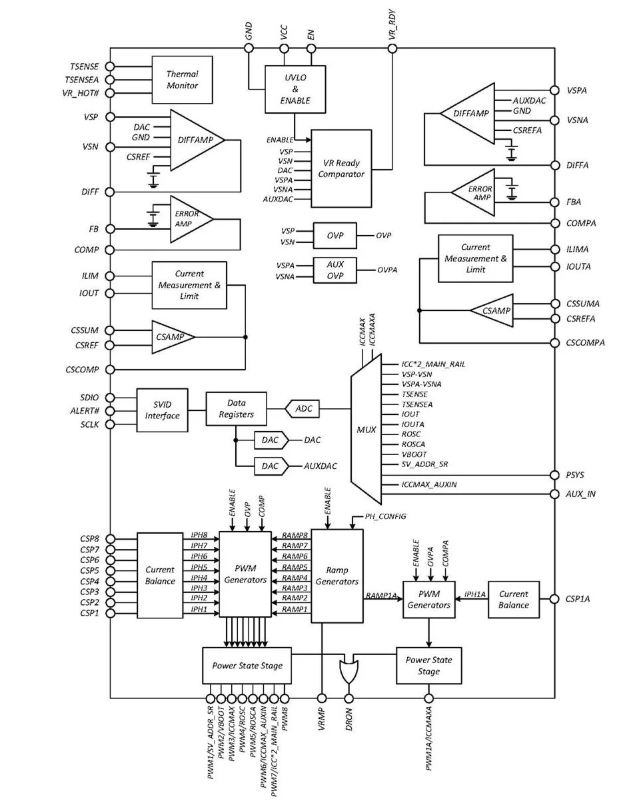

框图

二、关键特性

2.1 宽输入电压范围

Vin范围为4.5 V至21 V,能适应多种电源环境,为不同的应用场景提供了广泛的选择。

2.2 预充电负载启动

可在预充电负载下启动,避免误触发过压保护(OVP),确保系统的稳定性和可靠性。

2.3 数字软启动和可调Vboot

支持数字软启动斜坡和可调Vboot,可根据实际需求灵活调整启动过程,减少启动冲击。

2.4 高阻抗差分输出电压放大器

采用高阻抗差分输出电压放大器,能准确测量输出电压,提高系统的控制精度。

2.5 双VID表支持

支持双VID表,与IMVP9.1兼容,可满足不同CPU的供电需求。

2.6 大电流扩展能力

支持大电流扩展,能为高功率CPU提供稳定的电源供应。

2.7 动态参考注入和可编程输出电压斜率

具备动态参考注入和可编程输出电压斜率功能,可快速响应负载变化,提高系统的动态性能。

2.8 各相差分电流感应放大器

每相都配备差分电流感应放大器,可精确监测各相电流,实现电流平衡控制。

2.9 可编程自适应电压定位(AVP)

支持可编程自适应电压定位(AVP),可根据负载情况自动调整输出电压,提高系统效率。

2.10 可调开关频率范围

开关频率范围可调,可在180 kHz至1.17 MHz之间进行编程,满足不同应用的需求。

2.11 数字稳定开关频率和超声波操作

采用数字稳定开关频率技术,支持超声波操作,可有效降低声学噪声。

2.12 符合Intel的IMVP9.1规范

满足Intel的IMVP9.1规范,确保与Intel CPU的兼容性。

2.13 电流模式双边缘调制

采用电流模式双边缘调制技术,能对瞬态负载做出快速初始响应,提高系统的稳定性。

2.14 无铅封装

该器件采用无铅封装,符合环保要求。

三、典型应用

NCP81560主要应用于计算机领域,为CPU提供稳定、高效的电源供应。其典型应用电路如下:

四、引脚功能

| NCP81560采用QFN52 6x6, 0.4P封装,其引脚功能如下表所示: | Pin No. | Pin Name | Description |

|---|---|---|---|

| 1 | IOUT | 调节器1的总输出电流监测 | |

| 2 | EN | 使能。高电平使能两个轨 | |

| 3 | SDIO | 串行VID数据接口 | |

| 4 | ALERT# | 串行VID警报信号 | |

| 5 | SCLK | 串行VID时钟 | |

| 6 | VR RDY | 指示两个轨准备好接受SVID命令 | |

| 7 | VCC | 内部控制电路的电源。需连接去耦电容到地 | |

| 8 | PSYS | 系统电源信号输入。通过电阻接地来缩放该信号 | |

| 9 | VRMP | Vin的前馈输入,用于斜坡斜率补偿。流入该引脚的电流用于控制PWM斜率的斜坡 | |

| 10 | VR HOT# | 开漏输出。指示高VR温度或每通道过流保护(OCP) | |

| 11 | AUX IN | 0xODh SVID域的AUX IMON输入。通过电阻接地来缩放该信号 | |

| 12 | NC | 保留 | |

| 13 | IOUTA | 调节器2的总输出电流监测 | |

| 14 | VSNA | 调节器2的差分输出电压负端感应 | |

| 15 | VSPA | 调节器2的差分输出电压正端感应 | |

| 16 | DIFFA | 调节器2的差分远程感应放大器的输出 | |

| 17 | FBA | 调节器2的误差放大器电压反馈 | |

| 18 | COMPA | 误差放大器的输出和调节器2的PWM比较器的反相输入 | |

| 19 | CSCOMPA | 调节器2的总电流感应放大器的输出 | |

| 20 | ILIMA | 过流阈值设置 - 通过电阻连接到CSCOMPA来编程调节器2的过流阈值 | |

| 21 | CSSUMA | 调节器2的总电流感应放大器的反相输入 | |

| 22 | CSREFA | 调节器2的总电流感应放大器的参考电压输入 | |

| 23 | CSP1A | 调节器2的第1相电流平衡放大器的同相输入 | |

| 24 | TSENSEA | 调节器2的温度感应输入 | |

| 25 | PWM1A/ICCMAXA | 调节器2的PWM1输出。下拉该引脚可在启动时编程调节器2的ICCMAX | |

| 26 | DRON | 外部FET驱动器使能,用于离散驱动器或onsemi DrMOS | |

| 27 | PWM8 | 调节器1的PWM8输出 | |

| 28 | PWM7/ ICC*2_MAIN_RAIL | 调节器1的PWM7输出。下拉该引脚可将主轨的ICCMAX从255 A扩展到511 A | |

| 29 | PWM6/ ICCMAX AUXIN | PWM6 output for regulator 1/Pulldown resistor on this pin programs ICCMAX for the AUX_IN monitoring rail | |

| 30 | PWM5/ROSCA | 调节器1的PWM5输出。下拉该引脚可编程调节器2的RoscA值 | |

| 31 | PWM4/ROSC | 调节器1的PWM4输出。下拉该引脚可编程调节器1的Rosc值 | |

| 32 | PWM3/ICCMAX | 调节器1的PWM3输出。下拉该引脚可在启动时编程调节器1的ICCMAX | |

| 33 | PWM2/VBOOT | 调节器1的PWM2输出。该引脚可用于编程八相和一相的Vboot | |

| 34 | PWM1/ SV ADDR SR | 调节器1的PWM1输出。下拉该引脚可配置SVID地址、斜率和Intel专有电流保护功能 | |

| 35 | TSENSE | 调节器1的温度感应输入 | |

| 36 | CSP1 | 调节器1的第1相差分电流感应正端 | |

| 37 | CSP2 | 调节器1的第2相差分电流感应正端 | |

| 38 | CSP3 | 调节器1的第3相差分电流感应正端 | |

| 39 | CSP4 | 调节器1的第4相差分电流感应正端 | |

| 40 | CSP5 | 调节器1的第5相差分电流感应正端 | |

| 41 | CSP6 | 调节器1的第6相差分电流感应正端 | |

| 42 | CSP7 | 调节器1的第7相差分电流感应正端 | |

| 43 | CSP8 | 调节器1的第8相差分电流感应正端 | |

| 44 | CSREF | 调节器1的总电流感应放大器的参考电压输入 | |

| 45 | CSSUM | 调节器1的总电流感应放大器的反相输入 | |

| 46 | ILIM | 过流阈值设置 - 通过电阻连接到CSCOMP来编程调节器1的过流阈值 | |

| 47 | CSCOMP | 调节器1的总电流感应放大器的输出 | |

| 48 | COMP | 误差放大器的输出和调节器1的PWM比较器的反相输入 | |

| 49 | FB | 调节器1的误差放大器电压反馈 | |

| 50 | DIFF | 调节器1的差分远程感应放大器的输出 | |

| 51 | VSP | 调节器1的差分输出电压正端感应 | |

| 52 | VSN | 调节器1的差分输出电压负端感应 | |

| Flag | GND |

五、最大额定值和电气特性

5.1 最大额定值

| 为确保器件的安全和可靠运行,各引脚的最大额定值如下表所示: | Pin Symbol | VMAX | VMIN | IsOURCE | ISINK |

|---|---|---|---|---|---|

| COMP, COMPA | VCC+0.3V | -0.3V | 2mA | 2mA | |

| CSCOMP,CSCOMPA | VCC+0.3V | -0.3V | 2 mA | 2mA | |

| PWMX | VCC+0.3V | -0.3V | 1mA | ||

| VSN. VSNA | GND+0.3V | GND-0.3V | 1 mA | 2mA | |

| DIFF,DIFFA | VCC+0.3V | -0.3V | 2 mA | 2mA | |

| VR RDY | VCC+0.3V | -0.3V | 2mA | ||

| VCC | 6.0V | -0.3V | |||

| VRMP | VCC+0.3V | -0.3V | |||

| SCLK,SDIO | 3.6V | -0.3V | |||

| All Other Pins | VCC+0.3V | -0.3V |

5.2 电气特性

| 在特定的测试条件下(-40°C < TA < 100°C,4.75 V < VCC < 5.25 V,CVCC = 0.1 μF),器件的电气特性如下表所示: | Parameter | Test Conditions | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| BIAS SUPPLY | ||||||

| VCC Voltage Range | 4.75 | 5.25 | V | |||

| Quiescent Current (PS0, 1) | PS0 | 29 | mA | |||

| PS1 | 25 | mA | ||||

| PS2 | 21 | mA | ||||

| PS3 | 14 | mA | ||||

| PS4 | 79 | μA | ||||

| Enable low | 64 | μA | ||||

| UVLO Threshold | VCC Rising | 4.5 | V | |||

| VCC Falling | 4.1 | V | ||||

| VCC UVLO Hysteresis | 100 | mV | ||||

| VRMP | ||||||

| VIN Supply Range | VRMP range prior to external voltage divider resistor network with 1/12 ratio | 4.5 | 21 | V | ||

| UVLO Threshold | VRMP Rising | 0.355 | V | |||

| VRMP Falling | 0.250 | V | ||||

| UVLO Hysteresis | 100 | mV | ||||

| ENABLE INPUT | ||||||

| Upper Threshold Activation Level | 0.8 | V | ||||

| Lower Threshold Deactivation Level | 0.3 | V | ||||

| PHASE DETECTION | ||||||

| CSP Pin Threshold Voltage | VCC - 0.4 | V | ||||

| Phase Detect Timer | 1.5 | ms | ||||

| IMVP9.1 DAC (Protocol 0Eh) | ||||||

| System Voltage Accuracy | 0.25 < DAC < 0.495 V (at 25°C only) | -10 | 10 | mV | ||

| 0.5 < DAC < 0.745 V (at 25°C only) | -8 | 8 | mV | |||

| 0.75 < DAC < 1.52 V (at 25°C only) | -0.5 | 0.5 | % | |||

| DAC SLEW RATE | ||||||

| Soft Start Slew Rate | 1/4 fast | mV/s | ||||

| Slew Rate Slow | 1/4 fast | mV/s | ||||

| Slew Rate Fast | Resistor Selectable (See Table 9) | >10 | mV/s | |||

| DRON | ||||||

| Output High Voltage Sourcing | 500 μA | 3 | V | |||

| Output Low Voltage Sinking | 500 μA | 0.1 | V | |||

| TSENSE | ||||||

| TSENSE Bias Current | 115.5 | 120 | 124.5 | μA | ||

| Alert# Assert Threshold | 556 | mV | ||||

| De-Assert Threshold | 595 | mV | ||||

| VR_HOT Assert Threshold | 517 | mV | ||||

| De-Assert Threshold | 556 | mV | ||||

| VR_RDY OUTPUT | ||||||

| Output Low Saturation Voltage | IVR_RDY = -4 mA | 0.1 | 0.3 | V | ||

| VR_RDY Rise Time | 1 k pull-up to 3.3 V, CTOT = 45 pF | 110 | 150 | ns | ||

| VR_RDY Fall Time | 20 | 150 | ns | |||

| VR_RDY Output Voltage High | 0.8 | 3.3 | V | |||

| SVID (SDIO and SCLK) | ||||||

| SVID Voltage Low Level | VIL, (VCC = 5 V, TA = 25°C) | 0.45 | V | |||

| SVID Voltage High Level | VIH, (VCC = 5 V, TA = 25°C) | 0.65 | V | |||

| SDIO Output Low Voltage | VOL | 0.3 | V | |||

| SVID Clock to Data Delay (Note 7) | TCO | 12 | ns | |||

| SVID Setup Time (Note 7) | 7 | ns | ||||

| SVID Hold Time (Note 7) | 14 | ns | ||||

| SVID Pull Down Resistance | 4 | kΩ | ||||

| Pad and Pin Capacitance | VCC = 5 V, TA = 25°C | 5 | pF | |||

| ALERT# | ||||||

| VOL (Output Low) | 0.3 | V | ||||

| OVP AND UVP | ||||||

| Absolute Over Voltage Threshold | 10 mV DAC step During Soft Start - CSREF Rising | 3.3 | 3.44 | 3.6 | V | |

| 5 mV DAC step During Soft Start - CSREF Rising | 2.4 | 2.5 | 2.65 | V | ||

| Over Voltage Threshold Above DAC | VSP-VSN-VID Rising | 350 | 400 | 475 | mV | |

| Over Voltage Delay | VSP-VSN Rising to PWM Low | 50 |

-

深入解析 LM3017:高效低侧控制器的卓越性能与应用2026-04-19 541

-

深入解析LM3150:高效同步降压控制器的卓越性能与应用2026-04-18 175

-

深入解析ISL8107:单相PWM控制器的卓越性能与应用指南2026-04-13 318

-

深入剖析NCP5424:多功能双同步降压控制器的卓越性能与设计应用2026-04-12 356

-

深入解析NCP3155A/B:3A同步降压调节器的卓越性能与应用设计2026-04-11 146

-

深入解析LTC3862 - 1:多相电流模式升压DC/DC控制器的卓越性能与应用2026-03-12 238

-

深入解析LTC3875:高效双相同步控制器的卓越性能与应用2026-03-09 184

-

深入解析ISL6539:双PWM控制器的卓越性能与应用设计2026-03-05 550

-

深入解析UC19432-SP:高精度模拟控制器的卓越性能与应用2026-03-02 187

-

深入解析ISL81807:80V双同步升压控制器的卓越性能与应用2025-12-29 406

-

深入解析NCP81565:6 + 2相输出控制器的卓越性能与应用2025-12-03 618

全部0条评论

快来发表一下你的评论吧 !