深入剖析ADC12V170:高性能A/D转换器的卓越之选

电子说

1.4w人已加入

描述

在电子工程领域,模拟 - 数字转换器(ADC)是连接现实世界模拟信号与数字系统的关键桥梁。今天,我们将深入探讨德州仪器(TI)的ADC12V170,一款具有高性能和广泛应用前景的12位、170 MSPS A/D转换器。

文件下载:adc12v170.pdf

产品概述

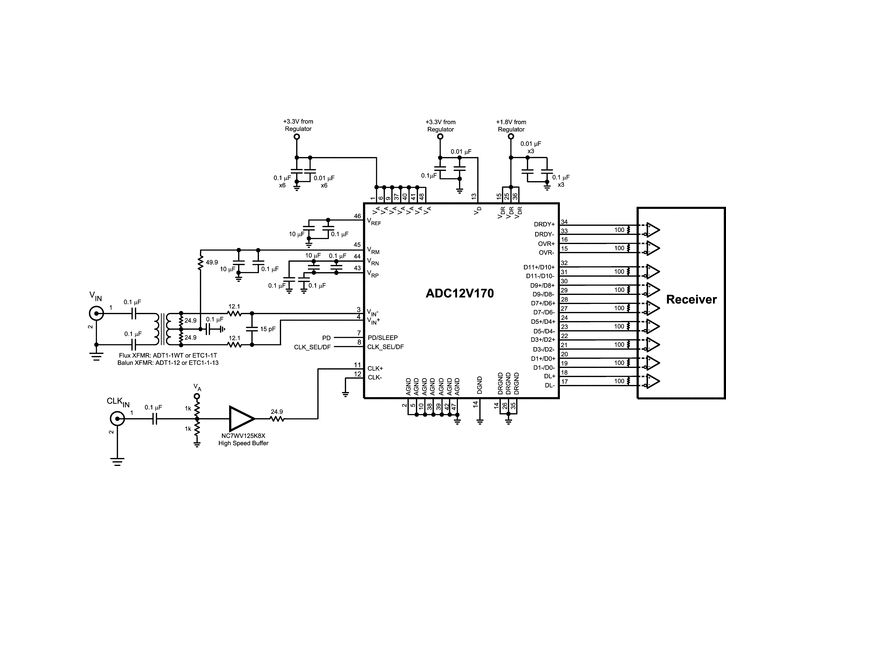

ADC12V170是一款采用LVDS输出的高性能CMOS A/D转换器,能够以高达170 MSPS的速率将模拟输入信号转换为12位数字字。它采用差分流水线架构,结合数字误差校正和片上采样保持电路,在降低功耗和外部元件数量的同时,提供出色的动态性能。其独特的采样保持级实现了1.1 GHz的全功率带宽,为高频信号处理提供了有力支持。

关键特性

高性能指标

- 分辨率与转换速率:具备12位分辨率,转换速率高达170 MSPS,能够满足高速数据采集的需求。

- 出色的动态性能:在70 MHz输入频率下,典型SNR为67.2 dBFS,SFDR为85.8 dBFS,ENOB为10.9位,确保了高精度的信号转换。

- 宽频带响应:全功率带宽达到1.1 GHz,可处理高频信号。

灵活的工作模式

- 时钟模式选择:支持单端或差分时钟模式,通过CLK_SEL/DF引脚可灵活配置。

- 输出数据格式:提供偏移二进制或2的补码输出数据格式,满足不同应用的需求。

低功耗设计

- 双电源供电:采用+3.3V和+1.8V双电源供电,降低功耗的同时减少噪声干扰。

- 电源管理模式:具备掉电和睡眠模式,掉电模式下功耗可降至15 mW,睡眠模式下为50 mW,且睡眠模式唤醒时间更快。

内部参考与采样保持

- 内部精密参考:提供稳定的1.0V内部参考电压,也可使用外部参考。

- 片上采样保持电路:确保信号的准确采样和转换。

引脚功能详解

模拟输入引脚

- VIN+和VIN -:差分模拟输入引脚,差分满量程输入信号电平为参考电压的两倍。

- VRP、VRM和VRN:参考旁路引脚,需进行适当的电容旁路,以确保参考电压的稳定。

- VREF:可作为内部1.0V参考电压输出或外部参考电压输入。

时钟与控制引脚

- CLK_SEL/DF:四态引脚,控制输入时钟模式和输出数据格式。

- PD/Sleep:三态输入引脚,控制掉电和睡眠模式。

- CLK+和CLK -:时钟输入引脚,可配置为单端或差分时钟输入。

数字输出引脚

- D0 - D11:LVDS数字数据输出引脚,构成12位转换结果。

- DRDY+和DRDY -:数据就绪选通信号,用于时钟输出数据。

- OVR+和OVR -:过范围指示输出,当输入幅度超出12位转换范围时置高。

电源引脚

- VA:正模拟电源引脚,需连接到稳定的+3.3V电源,并进行电容旁路。

- VD:正数字电源引脚,连接到+3.3V电源。

- VDR:输出驱动器正电源引脚,连接到+1.8V电源。

- AGND、DGND和DRGND:分别为模拟、数字和输出驱动器的接地引脚。

应用场景

ADC12V170的高性能和灵活性使其适用于多种应用场景,包括:

- 高IF采样接收器:处理高频中频信号,实现高精度的信号采集。

- 无线基站接收器:提高基站的信号接收性能。

- 功率放大器线性化:优化功率放大器的性能。

- 多载波、多模式接收器:支持多种通信模式。

- 测试与测量设备:确保测试数据的准确性。

- 通信仪器:用于通信系统的信号处理。

- 雷达系统:处理雷达回波信号。

设计注意事项

电源管理

- 电源引脚需进行适当的电容旁路,以减少电源噪声的影响。

- 确保|VA - VD| ≤ 100 mV,以保证转换器的准确性。

时钟信号

- 时钟信号应具有稳定的频率和低抖动,可通过高速缓冲门驱动时钟输入。

- 时钟线路应尽量短,避免与其他信号交叉,以减少干扰。

模拟输入

- 模拟输入应使用低源阻抗的驱动源,以提高性能。

- 输入信号的共模电压应在1.4V - 1.6V范围内,推荐使用VRM作为共模电压。

数字输出

- 数字输出负载电流应尽量小,以减少噪声。

- 输出电容应控制在规定范围内,避免影响动态性能。

布局与接地

- 保持模拟和数字电路区域的分离,以减少干扰。

- 时钟线路应与其他信号隔离,避免引入抖动。

- 所有接地连接应具有低电感路径,确保接地良好。

总结

ADC12V170以其高性能、低功耗和灵活的工作模式,成为电子工程师在高速数据采集和信号处理应用中的理想选择。通过合理的设计和布局,能够充分发挥其优势,实现高精度的信号转换。在实际应用中,我们需要根据具体需求,综合考虑各项性能指标和设计注意事项,以确保系统的稳定性和可靠性。

你是否在使用类似的A/D转换器时遇到过挑战?或者对ADC12V170的应用有独特的见解?欢迎在评论区分享你的经验和想法。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析ADS574:高性能CMOS模数转换器的卓越之选2026-04-18 130

-

深入剖析AD9762:高性能12位D/A转换器的卓越之选2026-04-14 1138

-

深入剖析ICL7109:12位A/D转换器的卓越之选2026-04-10 147

-

深入剖析LTC2220/LTC2221:高性能12位ADC的卓越之选2026-04-03 142

-

深度剖析MAX170:12位A/D转换器的卓越之选2026-04-02 166

-

深度剖析AD9434:高性能12位模数转换器的卓越之选2026-03-31 230

-

深入剖析ADC12081:高性能12位A/D转换器的技术解析2025-12-10 818

-

深入剖析ADC124S101:高性能12位A/D转换器的卓越之选2025-12-02 656

-

深入剖析ADC12C170:高性能12位A/D转换器的技术解析2025-11-28 695

-

深入剖析ADC12DS105:高性能12位A/D转换器的卓越之选2025-11-26 616

-

ADC12V170高性能CMOS模数转换器数据表2024-07-19 399

全部0条评论

快来发表一下你的评论吧 !