ADC08B200:高速8位A/D转换器的全方位解析

电子说

描述

在电子工程领域,A/D转换器是连接模拟世界和数字世界的桥梁,其性能直接影响到整个系统的精度和稳定性。今天,我们就来深入了解一款高性能的8位、200 MSPS A/D转换器——ADC08B200。

文件下载:adc08b200.pdf

一、产品概述

ADC08B200是德州仪器(TI)推出的一款高速模拟 - 数字转换器,集成了捕获缓冲器,其8位、200 MSPS的A/D核心基于成熟的ADC08200,具备跟踪和保持功能,并针对低功耗进行了优化。该器件拥有可选择大小的捕获缓冲器,最大可达1,024字节,允许以较慢的读出速率快速捕获输入信号。此外,片上时钟PLL电路可对时钟速率进行倍频,以提供高速采样时钟。

二、关键特性

2.1 高性能指标

- 分辨率:8位,能够满足大多数中等精度的应用需求。

- 最大采样频率:200 MSPS(最小值),可实现高速信号的采样。

- DNL:±0.4 LSB(典型值),保证了良好的线性度。

- ENOB:在 $f_{IN}=49 MHz$ 时为7.2位(典型值),有效位数较高。

- THD:在 $f_{IN}=49 MHz$ 时为−53 dBc(典型值),总谐波失真低。

2.2 低功耗设计

该器件的功耗与采样率呈线性关系,在不同的工作模式下,功耗表现出色。例如,在50 MHz输入时,工作功耗为2 mW / Msps(典型值),掉电模式下功耗仅为2.15 mW(典型值)。

2.3 丰富的功能特性

- PLL时钟倍频:可通过PLL对输入时钟进行2、4或8倍频,灵活满足不同的采样率需求。

- 可选择捕获缓冲器大小:支持256、512或1024字节的缓冲器配置,方便不同应用场景的数据存储。

- FPGA训练模式:提供测试模式,可输出特定的测试图案,用于训练接收设备。

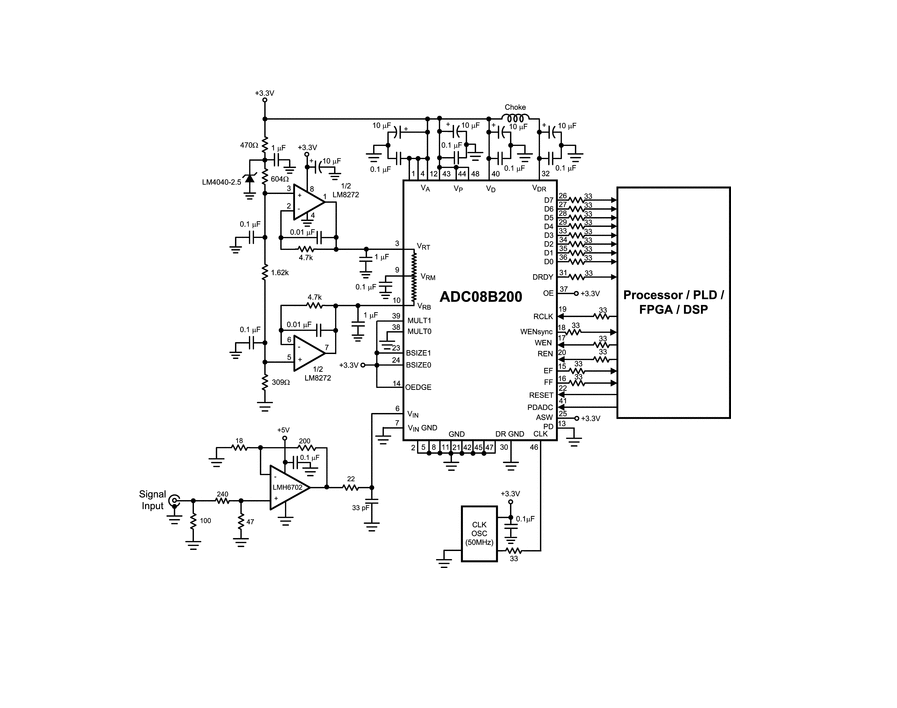

三、引脚配置与功能

3.1 引脚配置

ADC08B200采用48引脚塑料封装(TQFP),引脚分布合理,方便进行PCB布局。其引脚涵盖了模拟输入、参考输入、数字输入、时钟输入、缓冲器控制等多种功能。

3.2 主要引脚功能

- 模拟输入引脚(VIN):用于输入待转换的模拟信号,转换范围由参考电压VRT和VRB确定。

- 参考输入引脚(VRT、VRB、VRM):VRT和VRB分别为参考梯形的顶部和底部电压,VRM为参考梯形的中点电压,这些引脚的正确设置对转换精度至关重要。

- 数字输入引脚:包括PD(芯片掉电)、PDADC(ADC掉电)、CLK(时钟输入)、RCLK(缓冲器读取时钟)、WEN(写使能)、REN(读使能)等,用于控制芯片的工作模式和数据读写操作。

- 数字输出引脚:包含DO - D7(数字数据输出)、DRDY(数据准备好)、WENSYNC(同步写使能)、EF(缓冲器空标志)、FF(缓冲器满标志)等,用于输出转换后的数据和状态信息。

四、电气特性

4.1 直流精度

- INL(积分非线性):最大值为±1.3 LSB,确保了转换结果的整体线性度。

- DNL(差分非线性):最大值为±0.9 LSB,保证了每个量化台阶的一致性。

- 缺失码:为0(最大值),避免了转换过程中的码缺失问题。

4.2 模拟输入和参考特性

- 输入电压范围:VIN在VRB和VRT之间,可根据实际需求设置参考电压来调整输入范围。

- 输入电容:时钟低电平时为3 pF,时钟高电平时为4 pF,在设计驱动电路时需要考虑该电容的影响。

- 模拟输入电阻:大于1 MΩ,对驱动电路的负载要求较低。

4.3 数字输入特性

- 逻辑高输入电压(VIH):不同引脚的VIH要求不同,如OEDGE/TEN引脚为2.2 - 2.7 V(最小值),其他引脚为1.6 - 2.1 V(最小值)。

- 逻辑低输入电压(VIL):同样,不同引脚的VIL要求也有所差异,如OEDGE/TEN引脚为0.9 - 0.5 V(最大值),其他引脚为1.3 - 0.7 V(最大值)。

4.4 电源特性

- 模拟电源电流(IA):在不同输入条件下,电流值有所变化,如DC输入时为72.5 mA,50 MHz输入时为76.8 - 88.3 mA(最大值)。

- 数字核心电源电流(ID):根据不同的工作模式和输入条件,ID也会相应改变。

- PLL电源电流(IP):PLL不同倍频模式下,电流值不同,如PLL x2时为8.8 - 10.1 mA(最大值)。

- 输出驱动电源电流(IDR):受输入信号频率的影响,在DC输入时为7 mA,50 MHz输入时为41 - 57 mA(最大值)。

五、时钟选项

ADC08B200内置PLL,可通过MULT引脚选择CLK频率倍增器或旁路PLL。当有稳定的所需采样率时钟源时,建议旁路PLL以减少相位噪声的影响;若没有合适的时钟源,可使用内部PLL将输入时钟频率乘以2、4或8来获得所需的采样率。

| MULT1 | MULTO | CLK频率倍增器 | CLK频率范围(MHz) |

|---|---|---|---|

| 0 | 0 | 1 | 1 - 210 |

| 0 | 1 | 2 | 15 - 105 |

| 1 | 0 | 4 | 15 - 50 |

| 1 | 1 | 8 | 15 - 25 |

六、数据缓冲器的使用

6.1 缓冲器配置

通过BSIZE引脚可选择缓冲器的大小或旁路缓冲器。用户可根据实际应用需求,灵活配置缓冲器为256、512或1024字节,或者直接绕过缓冲器,使数据直接以采样时钟速率输出。

| BSIZE1 | BSIZEO | 缓冲器大小 |

|---|---|---|

| 0 | 0 | 缓冲器旁路 |

| 0 | 1 | 256字节 |

| 1 | 0 | 512字节 |

| 1 | 1 | 1024字节 |

6.2 数据读写操作

- 写入操作:当WEN输入为高电平时,每个采样时钟上升沿将数据写入缓冲器。

- 读取操作:当REN输入为高电平时,通过RCLK信号从缓冲器中读取数据。需要注意的是,不能同时进行写入和读取操作,且WEN和REN输入不能同时为高电平。

6.3 状态标志

- EF(缓冲器空标志):当缓冲器为空时,EF输出为高电平,此时DRDY和数据输出停止切换。

- FF(缓冲器满标志):当缓冲器满时,FF输出为高电平,若WEN输入保持高电平,且ASW输入不为高电平,则下一个采样时钟上升沿将覆盖旧数据。

七、应用信息

7.1 参考输入

参考输入VRT和VRB分别为参考梯形的顶部和底部,输入信号在这两个电压之间将被数字化为8位。为了获得更准确的参考电压,建议使用低阻抗源驱动参考引脚。

7.2 模拟输入

ADC08B200的模拟输入为开关后接积分器,输入电容随时钟电平变化。为了减少输入电流尖峰对驱动放大器的影响,可在放大器和ADC输入之间使用单极点RC滤波器。

7.3 电源供应

A/D转换器需要良好的电源旁路,每个电源引脚应配备10 µF钽或铝电解电容和0.1 µF陶瓷芯片电容。同时,要注意隔离不同电源引脚,避免数字噪声耦合到模拟部分。

7.4 布局和接地

正确的接地和信号布线对确保准确转换至关重要。应使用单一的统一接地平面,避免分割接地平面,同时将模拟和数字电路分开,时钟线应与其他线路隔离。

八、常见应用误区及解决方法

8.1 输入电压超出范围

所有输入电压不应超过电源引脚300 mV或低于地引脚300 mV,否则可能导致故障或不稳定。可在数字输入串联47Ω电阻来解决过冲问题。

8.2 驱动高电容数字数据总线

输出驱动电容过大将导致动态性能下降,可对数字数据输出进行缓冲,或在每个数字输出添加12Ω - 27Ω串联电阻。

8.3 使用不适当的放大器驱动模拟输入

模拟输入的电压尖峰可能导致放大器不稳定,应选择能够快速响应的放大器,并使用单极点RC滤波器来确保放大器稳定性。

8.4 时钟源抖动过大

时钟源抖动会导致采样间隔变化,降低SNR性能,应使用低抖动的时钟源,并尽量缩短时钟信号走线长度。

九、总结

ADC08B200以其高速采样、低功耗、丰富的功能和良好的性能指标,成为许多8位ADC应用的理想选择。在实际设计中,电子工程师需要充分了解其特性、引脚功能、电气特性和应用注意事项,避免常见的应用误区,以确保系统的稳定运行和高性能表现。希望通过本文的介绍,能帮助大家更好地掌握和应用这款优秀的A/D转换器。

-

ADC0820-N:高性能8位A/D转换器的深度解析2025-12-10 717

-

ADC12040:高性能12位A/D转换器的全方位解析2025-12-08 1037

-

深入剖析ADC08L060:高性能8位A/D转换器的设计与应用2025-12-05 984

-

ADC08D1000:高性能低功耗8位A/D转换器的设计与应用2025-12-02 905

-

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器2025-12-01 956

-

深入解析ADC08D1520:高性能8位ADC的卓越之选2025-11-28 681

-

ADC08D1020:高性能8位A/D转换器的深度解析2025-11-27 764

-

深入解析ADC08B3000:高性能8位3GSPS A/D转换器的技术奥秘2025-11-26 1112

-

ADC08B200的故障率是多少?2024-12-27 408

-

8位模数转换器LS08D1000替换ADC08200在示波器中的应用2024-10-23 1534

-

ADCO8B200高速模数转换器(ADC)数据表2024-07-29 465

-

DAC08:8位高速乘法D/A转换器(通用数字逻辑接口)数据表2021-05-08 1284

-

快捷式8位高速A-D转换器2010-05-07 1307

-

ADC08B200/ADC08B200Q,pdf datas2009-10-10 1028

全部0条评论

快来发表一下你的评论吧 !