阻抗匹配电路的作用,阻抗匹配的理想模型

电子说

描述

一、 阻抗匹配电路的作用

阻抗控制在硬件设计中是一个比较重要的环节,IC厂商针对其应用一般会向终端产商提供PCB板材质、PCB叠层、PCB板厚等一些相关参考设计建议(这些都是跟PCB阻抗控制设计息息相关的),终端厂商在拿到这些资料后,会结合实际情况据此进行本地化的设计调整,然后将相关设计资料及要求提供给PCB的生产厂家进行PCB生产。

针对不同信号系统有不同的特征阻抗值,比如75ohm、100ohm、90ohm、50ohm等,而对频率较高的RF信号来讲,最常见的是50ohm的阻抗控制。

在实际的PCB设计中,RF传输线通常都会采用微带线和带状线的走线方式, 且需要选取参考层来进行阻抗控制。考虑到芯片的RF特性、实际PCB生产工艺、及元器件用料的因素,除了需进行PCB RF传输线的阻抗控制外,在硬件设计上通常还需添加一些匹配网络电路用作RF的调试,一般说来,其作用大概为以下几种:

1、谐振频率以及带宽的调整

2、功率、EVM、ACLR、PA电流、传导杂散和辐射杂散等指标的调试等

图1 某IC厂商建议的4-layer层叠方式

二、 阻抗匹配的理想模型

射频工程师大都遇到过匹配阻抗的问题,通俗的讲,阻抗匹配的目的是确保能实现信号或能量从“信号源”到“负载”的有效传送,其最最理想模型当然是希望Source端的输出阻抗为50欧姆,传输线的阻抗为50欧姆,Load端的输入阻抗也是50欧姆,一路50欧姆下去,这是最理想的。

图2 理想阻抗传输

然而实际情况是:源端阻抗不会是50ohm,负载端阻抗也不会是50ohm,这个时候就需要若干个阻抗匹配电路,而匹配电路就是由电感和电容所构成,这个时候我们就需要使用电容和电感来进行阻抗匹配电路调试,以达到RF性能最优。

三、 电感电容的高频特性

要用电感电容解决高频的性能问题,那我们就需要先了解下电容和电感这些器件在高频的特性。

翻一翻以前的物理课本,对电容器,是用平板表面积与平板间距的比值来定义其容量:

(A代表平板表面积,d代表平板间距,理想情况下在平板间没有电流流动)

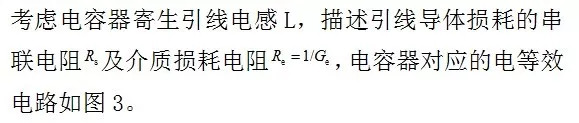

但在高频信号通过时,电容器平板间的实际电介质存在损耗(也就是板间有传导电流流动),所以,电容器的阻抗需要表示成电导和电纳的并联组合:

图3 高频电容等效电路

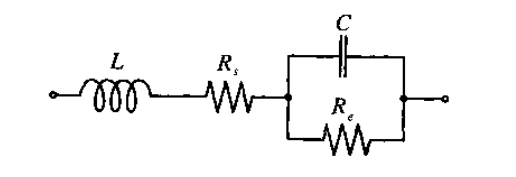

而对电感而言,在射频电路中经常使用的电感为线圈结构,其线圈是用导线在圆柱体上绕制而成,线圈除了具有与频率无关的电阻之外,它还存在一个“电感”,而临近的绕圈间存在着分离的移动电荷,所以它还存在一个寄生旁路“电容”。

图4 高频电感等效电路

在高频时,电容器中的电介质产生了损耗,所以电容器在谐振点前,呈现的阻抗特性与频率成反比;而对电感器而言,当频率接近谐振点时,高频电感的阻抗迅速提高,当频率继续提高时,寄生电容C的影响成为主要的,线圈阻抗逐渐降低。

所以,一个实际电感或者电容并不能简单用电感量或电容量来衡量,而应该将其当成寄生旁路电容C、串联电阻R、寄生电感L的综合效应,这个时候通过一个等效网络去模拟要更为合理,当然,具体使用时,有时还需考虑集总参数和分布参数电路模型。

图5 高频电容阻抗频率曲线

图6 高频电感阻抗频率曲线

四、 Smith圆图在RF匹配电路调试中的应用

说完电感、电容的高频特性,接着我们来看看Smith圆图。

Smith圆图上可以反映出如下信息: 阻抗参数Z,导纳参数Y,品质因子Q,反射系数,驻波系数,噪声系数,增益,稳定因子,功率,效率,频率信息等抗等参数。

图5 Simth圆图

是不是一脸懵,我们还是来看阻抗圆图吧:

图6 阻抗圆图

阻抗圆图的构图原理是利用输入阻抗与电压反射系数之间的一一对应关系,将归一化输入阻抗表示在反射系数极坐标系中,其特点归纳如下:

1.上半圆阻抗为感抗,下半圆阻抗为容抗;

2.实轴为纯电阻,单位圆为纯电抗;

3.实轴的右半轴皆为电压波腹点(除开路点),左半轴皆为电压波节点(除短路点);

4.匹配点(1,0),开路点(∞,∞)和短路点(0,0);

5.两个特殊圆:最大的为纯电抗圆,与虚轴相切的为匹配圆;

6.两个旋转方向:逆时针转为向负载移动,顺时针转为向波源移动。

导纳圆图与阻抗圆图互为中心对称,同一张圆图,即可以当作阻抗圆图来用,也可以当作导纳圆图来用,但是在进行每一次操作时,若作为阻抗圆图用则不能作为导纳圆图。

Smith圆图中,能表示出一些很有意思的特征:

在负载之前串联或并联一个可变电感/电容,电路图如图7左侧4个图所示,将得到Smith圆图上右侧的几条曲线。对应Smith阻抗圆及导纳圆,其运动轨迹如下:

1、使用Smith阻抗圆时,串联电感顺时针转,串联电容逆时针转;

2、使用Smith导纳圆时,并联电感,逆时针转,并联电容顺时针转。

图7 联接集中元件,Smith轨迹变化规律

五、 匹配电路调试的注意事项

以上串并联元件对应的smith图上的运动轨迹可作为调试的参考及对结果的初步判断,而至于RF匹配电路实际调试过程中的注意事项,一般而言有五项:

1 .电感/电容值不要过小,原因是要维持匹配的稳定性,因为电感/电容值会有误差,以电容为例子,大概有±0.1pF的误差,如果是一个容值为 0.3pF的电容,则误差高达33%,其容值范围为0.2pF~0.4pF,这可能会导致每片PCB的Tx/Rx Performance不一致,进而影响工厂量产时的良率。

2. 落地电容值不要过大,是因为依照容抗公式:

电容值越大,容抗越小,因此落地电容值过大,则可能会让信号都流到地端。

3.电感/电容值不要过于冷门,原因是方便备料。若是常见的值,则所有厂家都会有,量产过程中,避免出现厂家缺料的情况。

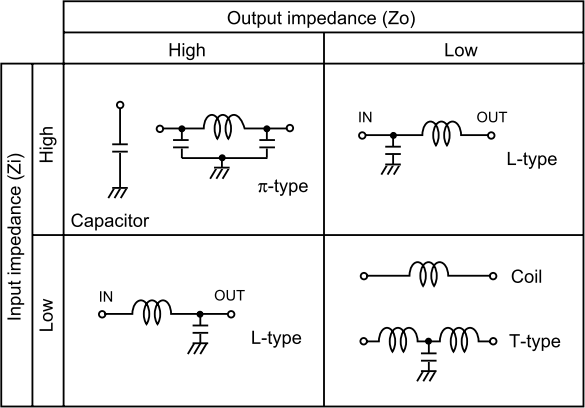

4.尽可能设计成Low Pass Filter,原因是这样可以抑制谐波。常用的 Low Pass Filter的组合如下:

图8 Low Pass Filter组合

5. 对一般消费电子产品而言,匹配电路整个频带的smith原图轨迹需落在VSWR=2的圆内,且其整个频带的阻抗轨迹尽可能收敛,这是最重要的原则,上述步骤,是以单一频率点来做匹配,但最后看整个频率范围内的Smith Chart轨迹,才能决定这一组匹配值可否采用。(如图9和图10)

图9 Smith Chart轨迹

图10 Smith Chart轨迹

六、 小结

对于靠近PA或者DUP等射频前端器件的匹配网络大家都会预留,但在一些物联网产品设计中,由于产品尺寸较小又需要设计PCB板载天线,有些工程师为了节省空间而省掉了靠近天线端的匹配网络,从而导致在RF性能的优化过程中或者认证要求的杂散测试中束手无策,造成产品开发周期加长或者硬件设计的改版,得不偿失。

因此,在实际的电路设计中,还是建议预留匹配电路,不管是射频前端还是后端的部分。

另外,还存在这样的一种可能,在将靠近天线端的匹配网络作为“天线”的一部分进行调试时,虽然驻波比得到了优化,但天线系统的效率反而会降低。所以,在整机环境较为恶劣的情况下,仅仅想依靠匹配网络的调整去提升整机的无线性能会有一定的难度,而且会存在杂散超标的风险。

调整匹配电路虽然能降低反射,但同样会引入损耗,为了优化性能多增加元器件,还有可能在生产制程上增加一些SMT issue的风险。

为解释一句情诗,写2900字注释。为做一项测试,终日与仪器为伴。没错,这就是班妹style。

班妹的愿望是大家在生产产品时,可以少走弯路少掉坑!产品研发阶段,有关技术方面的内容,可随时找我讨论,如果我知道的话,一定会尽力解答。另外,有测试需求的话,也可随时找我哟~

-

为什么要阻抗匹配?怎么进行阻抗匹配?2024-01-02 4259

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 3842

-

为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?2023-10-11 3453

-

窄带阻抗匹配电路设计2023-05-15 1607

-

阻抗匹配的原理及应用2022-08-22 4625

-

浅谈阻抗匹配的理想模型及方法2022-05-11 7326

-

阻抗匹配是什么意思_阻抗匹配原理详解2018-05-03 53223

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 44983

-

阻抗匹配电路的原理及其应用介绍2017-12-08 4166

-

什么是阻抗匹配以及为什么要阻抗匹配2015-10-28 1285

-

电路阻抗匹配设计2010-08-12 1219

-

分立元件组成的阻抗匹配电路2009-12-07 1638

-

怎样理解阻抗匹配?2009-11-30 1757

-

什么是阻抗匹配2006-09-25 4908

全部0条评论

快来发表一下你的评论吧 !