基于SV233A4W和模数转换器AD9822实现清分机图像采集系统的设计

描述

1、引言

随着ATM机普及,人们对流通货币质量要求越来越高,钞票清分工作对银行业来说就显得格外重要。清分机是一种高端金融机具产品,能够一次性完成钞票的清分工作,包括钞票点算、币种识别、真伪鉴别、面额清分、版本清分、新旧清分、方位识别(包括正反面、上下方向等共4种组合)等。按照不同的功能,清分机的工作速度可达到每分钟600张至1000张。

清分机的图像采集系统主要是南图像传感器对在传送带上高速传送的钞票进行采样、缓存,然后送至DSP图像处理模块。该系统是以CPLD完成钞票图像信息采集时序控制和数据缓存,采用接触式图像传感器(CIS)SV233A4W和模数转换器AD9822实现图像的采样和量化功能。另外,使用码盘和对管来实现传送带与采样的同步。

2、系统组成与原理

2.1系统组成

清分机的图像采集系统主要由码盘、对管、传感器、A/D转换器、CPLD等组成。CPLD是系统核心,控制各部分时序及数据采集。当无钞票时,系统处于等待状态;当有钞票经过对管时,将产生一个触发信号,CPLD接收到触发信号后,将控制接触式图像传感器对钞票进行采样,采样间隔由码盘信号分频控制。采集到的图像信息经A/D转换后,存储到内部RAM中,为图像处理单元DSP的后续处理、识别提供数据。该系统原理框图如图1所示。

2.1.1 CIS SV233A4W简介

CIS是一种基于CMOS技术的线阵传感器,它将光源、聚焦镜片及感应器固定于一个外罩内,具有体积小,成本低等特点。CIS适用于高速传输物体的表面图像采集。

SV233A4W是一款单色(G)线性CIS传感器,扫描宽度是216 mm,分辨率可达到200 dpi。该传感器共有1728个像元,有CP(移位时钟脉冲)和SP(启动脉冲)2个输入控制信号。如果在CP的上升沿检测到SP为高电平,则启动一行的扫描和串行移位输出工作。在每个CP的下降沿,Vout端口输出一个点的模拟电压值,这样经过1 728个CP时钟后,一行的数据,等待下一个SP启动信号。扫描一行的典型时间为0.5 ms。

2.1.2 A/D转换器AD9822简介

AD9822是号门对CCD/CIS模拟图像进行模/数转换的器件,输出动态范围是14位,可同时对3路RGB信号进行A/D转换。

AD9822具有3路RGB相互独立的采样和输出结构,每一路包括:相关双采样器(CCD)、偏移控制D/A转换器和数控增益放大器(PGA)。3路模拟信号经选择器依次输出,后经14位A/D转换器获得数字信号,这14位数字信号分两字节先后输出(D0~D7)。该器件工作时设有3个时钟,CDSCLK1是参考电平(OFFSEET)的采样时钟,CDSCLK2是输入数据电平的采样时钟,ADCCLK(是模数转换和控制数据输出的时钟。

AD9822共有4种工作模式,即3通道CDS模式、1通道CDS模式、3通道SHA模式和1通道SHA模式。在1通道模式中,只处理一路模拟信号,而3通道模式则同时处理3路信号。这里采用3通道SHA模式,在该模式下一个采样时钟CDSCLK2后需要3个输出时钟ADCCLK输出数据。

该器件内部各路偏移D/A转换器、PGA和模式的设置等都是由内部8个寄存器(地址为000~111)完成的,这些寄存器是由3个端口信号SCLK、SLOAD和SDATA控制。

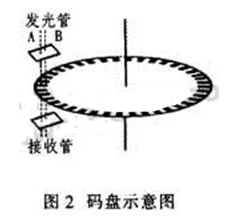

2.1.3码盘

码盘是一种常用的增量式角度传感器(图2),利用现代光刻技术在圆盘上均匀刻线,当圆盘旋转时,受刻线影响接收管接收到的光线出现亮暗变化,而输出电平则高低跳变。将码盘安装在电机上,电机旋转时,便有脉冲信号从码盘输出。输出的脉冲信号可与电机相连的传送带传送的距离进行换算,通过控制码盘输出脉冲的分频来控制钞票的采样间隔。

2.1.4对管

对管位于CIS传感器的上游,用于指示样品(钞票)的到来。当对管被物体遮挡时,对管输出高电平,否则维持低电平。在应用中对管输出高电平的脉宽与钞票全部通过的时长相等。因而可以利用对管输出信号(N2)控制每帧图像的采样使能。考虑到信号噪声的影响,需对管信号滤波;为保证每帧图像(包括整张钞票)具备一定余量,需要延时处理N2信号。

2.2采样原理

由于要从图像采样数据中提取出钞票的各种特征信息,所以图像采样数据要确保无失真地恢复钞票图像信息。因此,采样频率需满足二维取样定理。假设钞票图像的频谱在水平方向上的截止频率为fm,在垂直方向的截止频率为fm,则只要水平方向的空间取样频率F0满足F0≥2Fm,垂直方向的空间取样频率fm满足f0≥2fm条件,图像便可精确恢复。水平方向的采样频率由图像传感器的性能决定,而垂直方向的采样频率则由码盘信号的分频决定。

3、CPLD控制实现

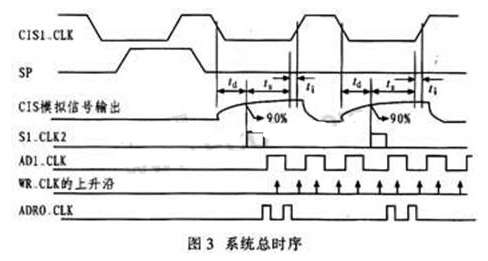

3.1系统总时序

该系统设计的关键在于图像传感器、A/D转换器以及数据存储器RAM之间的时序控制。系统的总时序关系为:对管信号N2是采样一张钞票的总使能,码盘信号MCLK的分频SP作为每一行采样的启动信号。在每一行的采样过程中,通过传感器移位时钟CIS1_CLK将每一点的数据移出。通过时钟S1_CLK2控制A/D转换器读取采样的模拟数据,并由输出时钟AD1_CLK控制A/D转换器输出量化的数字数据。然后,在地址时钟ADR0_CLK和写时钟WR_CLK的控制下写入RAM,系统总时序如图3所示。

3.2参数确定

根据CIS SV233A4W传感器特性可知,启动脉冲SP的脉宽应大于100 ns,而移位时钟CIS1_CLK最大频率为5MHz。脉宽大于50 ns,采样一行的典型时间是0.5 ms。若每张钞票需采样60行,则一张钞票最少需要30 ms,1分钟最多可采样1800张钞票。传感器的输出数据相对于移位时钟的延时为68ns,所以A/D转换器AD9822的读取时钟S1_CLK2与移位时钟CIS1_CU(需满足上述关系。由A/D转换器AD9822的特性可知,读取时钟S1_CLK2的脉宽大于10 ns,输出时钟AD1_CLK大于30 ns。S1_CLK2的频率与CIS1_CLK相同,AD1_CLK的频率应该是S1_CLK2的3倍频(3通道SHA模式),而相位应在S1_CLK2之后。

3.3设计实现

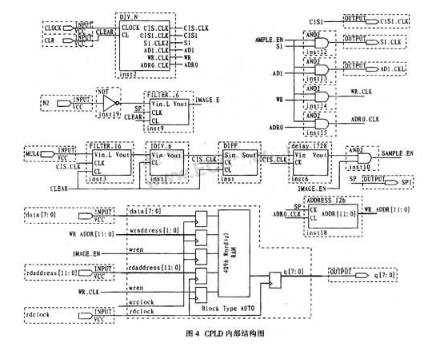

CPLD的内部结构如图4所示。CLOCK(50 MHz)为系统的基准时钟,通过分频器件DIV_N产生不同倍率的分频时钟。DIV_N输出的分频时钟(S1、AD1、WR、ADR0)作为系统中各时钟的基本信号,与行采样使能SAMPLE_EN逻辑与后,得到传感器移位时钟CIS1_CLK,A/D采样时钟S1_CLK2,A/D转换输出时钟AD1_CLK,RAM地址时钟ADR0_CLK和RAM写时钟WR_CLK信号,这些时钟信号只有在输入有效数据时使能,这样可避免读人干扰数据,还可降低系统功耗。在DIV_N中仅采用一个计数信号对CLOCK上升沿计数,计数状态下,根据所需波形输出特定向量,共用一个计数信号实现不同倍率分频,严格保证信号之间的相位关系。

对管信号N2和码盘输出脉冲信号MCLK,在电平跳变的前后产生的毛刺可采用数字可重触发器FILTER_16滤除。CLK为同步时钟;当输入信号Vin_L为低电平时,Vout为高电平,并对内部计数器同步置数15;当输入信号Vin_L为高电平时,计数器由计数值15对CLK上升沿递减计数,计数至0时,Vout在下一个CLK上升沿输出低电平;CL对Vout和内部计数器异步清零,初始化。Vout信号可用于滤除负脉冲Vin_L的毛刺,Vout的下降沿相对于Vin_L的上升沿有16个CLK时钟延时。

总使能信号IMAGE_EN是N2信号经滤波、延时后得到的,它和码盘分频信号SP拓宽后的信号SP_1728逻辑相与后得到行采样使能信号SAMPLE_EN,用于控制采样间隔。这里SP是将码盘输出信号MCLK经DIV_6六分频,再经单稳态电路DIFF得到的分频数可根据实际参数(码盘刻线精度、电机转速)修改。DIFF可以将前面的分频信号变为脉宽为1个时钟周期的脉冲信号,其内部标识状态为Q1Q0。当输入脉冲Sin为低电平时,Q1Q0=00,输出脉冲Sout=0;Sin为高电平时,Q1Q0=00,表明Sin的上升沿出现在前一个时钟周期,Sin=1,并Q1Q0=11;若Q1Q0≠00,则表明Sin的上升沿并非刚到达,Sout清零,Q1Q0=10。

信号SP_1728的脉宽为1 728个移位时钟周期,确保在每一行采样的过程中,全部且仅将1 728个点的图像信息输出。内部RAM的写地址端接人一个12位加法计数器ADDRESS_12b,对ADRO_CLK计数,输出RAM的12位写地址,清零端接CIS SV233A4W的启动信号SP。

4、仿真与结果分析

4.1时序控制仿真

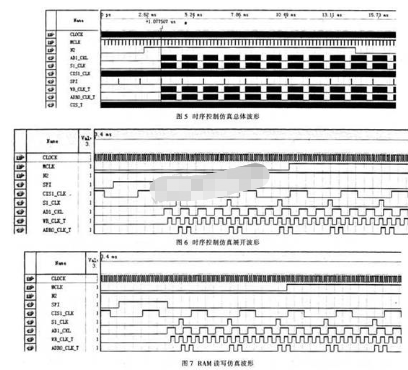

按照系统设计结构,该系统输入时钟CLOCK的频率为50 MHz,码盘信号频率为6 kHz,其仿真波形如图5和图6所示。由仿真波形可看出,满足系统要求中时序关系,由于A/D转换器只有一路输入,所以每3个输出数据有一组数据为有效地址。

4.2 RAM读写仿真

存储在CPLD内部RAM的采样数据要由后续DSP处理模块读取。在写时钟wrclock的作用下,从地址0开始向RAM依次写入0、1、2、3……,然后在RAM的读时钟端施加一个读时钟rdclock,在读地址rdaddress端施加从0递增的读地址,仿真RAM的读写,得到的仿真波形如图7所示。由仿真波形可以看出,RAM的读写正确,读取的数据相对于读时钟有一定延时。

5、结语

该高速图像采集装置已在钞票清分机中得到良好应用。该系统设计也可应用于连续、高速的图像采集系统,另外,还可采用接触式传感器,使其具有曝光时间短,感光速度和数据传输速度快,实现高效输入等特点,从而能够很好的满足清分机对采样图像质量的要求。

责任编辑:gt

-

模数转换器最高使用频段2025-12-16 778

-

数模和模数转换器2009-09-16 7937

-

SAR模数转换器AD7989-1和AD7989-52018-11-29 2428

-

AD9208BBPZRL-3000模数转换器2019-05-15 1070

-

TC7117A模数转换器实现单+ 5V电源的应用2019-07-24 1144

-

5962-9581501HXA高端AD模数转换器2020-07-15 2193

-

AD574ASE/883B高端AD模数转换器IC2020-08-14 1057

-

什么是光学模数转换器?原理是什么?有哪些技术指标?2021-04-20 2244

-

什么是模数转换器?2022-01-24 2310

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1811

-

基于CPLD的清分机纸币图像采集系统2010-12-22 647

-

提高模数转换器的精度和降低系统的成本2009-12-28 1464

-

嵌入式模数转换器的原理及应用2009-12-29 1406

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3655

-

逐次比较式模数转换器如何获取最佳采样频率2020-08-01 3599

全部0条评论

快来发表一下你的评论吧 !