利用电可擦除可编程逻辑器件实现DSP与SDRAM接口设计

描述

在多媒体应用中,多媒体信息绝大部分是视频数据和音频数据,而数字化的视频数据和音频数据的数据量是非常庞大的。为了能够及时完整地处理前端采集的数据,一般系统都采用高速DSP和大容量缓冲存储器,且缓冲存储器一般选用同步动态随机存储器(SDRAM)。由于DSP不能直接与SDRAM接口,而且SDRAM控制时序比较复杂,因此本文介绍如何利用电可擦除可编程逻辑器件实现TMS320C5402与SDRAM的接口。

1 、SDRAM结构和命令

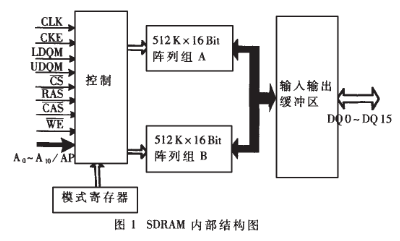

SDRAM是一种具有同步接口的高速动态随机存储器,本文选用的是Samsung公司512K×16Bit×2组的KM416S1120D。SDRAM的同步接口和内部流水线结构允许存储外部高速数据,其内部结构框图如图1所示。

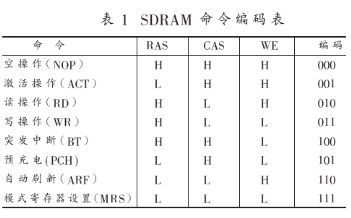

SDRAM的所有输入和输出都与系统时钟CLK上升沿同步,并且由输入信号RAS、CAS、WE组合产生SDRAM控制命令,其基本的控制命令如表1所示。

在具体操作SDRAM时,首先必须通过MRS命令设置模式寄存器,以便确定SDRAM的列地址延迟、突发类型、突发长度等工作模式;再通过ACT命令激活对应地址的组,同时输入行地址;然后通过RD或WR命令输入列地址,将相应数据读出或写入对应的地址;操作完成后用PCH命令或BT命令中止读或写操作。在没有操作的时候,每32ms必须用ARF命令刷新数据(2048行),防止数据丢失。

2、 FLEX10K系列EPLD特点

FLEX10K系列EPLD是工业界第一个嵌入式的可编程逻辑器件,主要由嵌入式阵列块(EAB)、逻辑阵列块(LAB)、快速布线通道(FastTrack)和I/O单元组成,具有如下特点:

(1)片上集成了实现宏函数的嵌入式阵列和实现普通函数的逻辑阵列;

(2)具有10000~250000个可用门;

(3)支持多电压I/O接口,遵守PCI总线规定,内带JTAG边界扫描测试电路;

(4)可快速预测连线延时的快速通道连续式布线结构;

(5)多达6个全局时钟信号和4个全局清除信号;

(6)增强功能的I/O引脚,每个引脚都有一个独立的三态输出使能控制,都有漏极开路选择。

3、 TMS320C5402和SDRAM接口设计

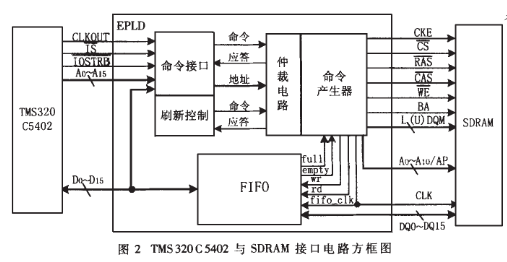

TMS320C5402和SDRAM接口电路方框图如图2所示。

命令接口主要对DSP送来的SDRAM的地址和操作命令进行解码(命令编码见表1);刷新控制主要对SDRAM数据刷新进行计时,确保32ms刷新2048行数据;仲裁电路主要对读写命令和刷新命令进行仲裁,杜绝同时操作,防止数据丢失;命令产生器主要用来产生控制SDRAM的各种时序,完成SDRAM的读、写和刷新,同时控制FIFO的读、写操作;FIFO是DSP与SDRAM之间的数据通道,深度为256,其作用是充分利用SDRAM的突发读写功能,提高系统速度,同时简化DSP软件设计。

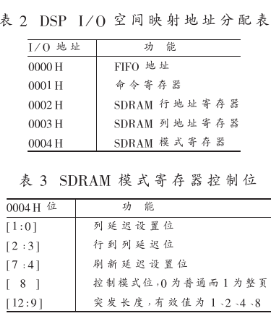

3.1 命令接口和刷新控制电路设计

命令接口电路主要由命令寄存器、命令译码器、SDRAM行列地址锁存器、模式寄存器组成。其中命令寄存器映射为DSP的I/O空间0001H,SDRAM行和列地址锁存器分别映射为DSP的I/O空间0002H和0003H,模式寄存器映射为DSP的I/O空间0004H,具体控制命令和I/O地址分配如表2、表3所示。

DSP每次进行读、写操作时,首先向其I/O空间0002H和0003H写入SDRAM行和列地址,然后向I/O空间0001H写入控制命令,命令译码器根据命令寄存器中命令,译码后向仲裁电路发出读写请求。

刷新控制电路主要由1562计数器构成。由于TMS320C5402时钟频率为100MHz,SDRAM要求在32ms之内刷新2048行数据,因此该计数器计数值应小于:

32ms/2048/0.01μs=1562.5。当计数器计满1562次时,刷新控制电路向仲裁电路发出刷新要求。

3.2 仲裁电路和命令产生器设计

仲裁电路接收命令接口模块解码的命令和刷新控制模块的刷新请求,产生适当的控制命令,其中刷新请求的优先级较高。当来自DSP的命令和来自刷新控制模块的刷新请求同时到达时,则首先执行刷新操作,然后执行来自DSP的命令。这样可以防止SDRAM的数据丢失。由此可知,仲裁电路实质上是一个优先级选择器。

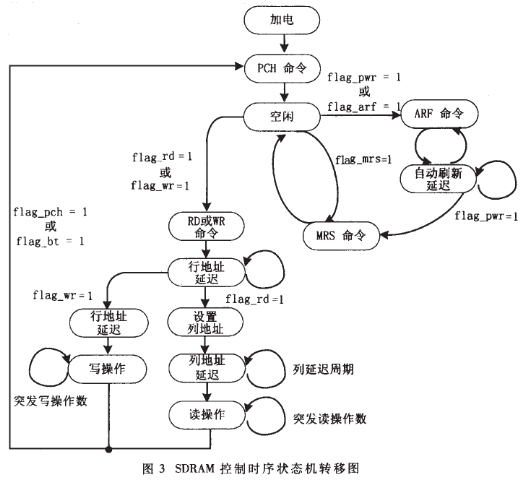

命令产生器主要产生SDRAM读、写和刷新的控制时序(具体时序可见参考文献1)以及FIFO的读写控制信号,用以对SDRAM进行各种操作,其实质上是一个Mealy型状态机,利用VHDL语言可以很方便地实现,其状态转移图如图3所示。

3.3 FIFO设计

FIFO电路是DSP与SDRAM进行数据交换的通道,通过FIFO电路可以很好地实现DSP对SDRAM的读写。FIFO电路被映射为DSP的I/O空间0000H(见表2),DSP对SDRAM的每次读或写,都对DSP的I/O空间0000H操作,简化了DSP软件设计。利用FLEX10K系列EPLD内部嵌入式阵列块(EAB)和参数化模块库(LPM),可以很快地构造出256×16的FIFO电路,FIFO的设计比较简单。VHDL描述具体如下(注意在程序开始处添加LPM库):

FIFO256 CSFIFO

GENERIC MAP LPM_WIDTH <= 16;LPM_NUM-

WORDS <= 256;

PORT MAP data <= LPM_WIDTH-1 DOWNTO 0;

wreq <= wr;rreq <= rd;

clock <= clk50;clockx2 <= clk100;

clr <= clr;sclr <= sclr;

empty <= empty;full <= full;

q<=qLPM_WIDTH-1 DOWNTO 0;

由于EPLD通用、高速及价廉的特点,因此具有很好的实际应用前景,尤其适用于需要大容量高速缓冲存储器的多媒体应用。

责任编辑:gt

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4615

-

可编程逻辑器件测试2023-06-06 1331

-

可编程逻辑器件的结构2023-03-24 2186

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2278

-

可编程逻辑器件(书皮)2022-07-10 809

-

PLD可编程逻辑器件2021-07-22 2335

-

可编程逻辑器件是如何发展的?2021-04-29 1885

-

如何利用EPLD实现TMS320C5402与SDRAM接口?2021-04-15 1373

-

可编程逻辑器件2014-04-15 3693

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1178

-

可编程逻辑器件基础及应用实验指导书2010-03-24 798

-

基于可编程逻辑器件的数字电路设计2009-11-16 1952

-

什么是PLD(可编程逻辑器件)2009-06-20 30094

-

可编程逻辑器件设计2006-03-25 1191

全部0条评论

快来发表一下你的评论吧 !