探索DAC122S085:12位微功耗双数模转换器的卓越性能与应用

电子说

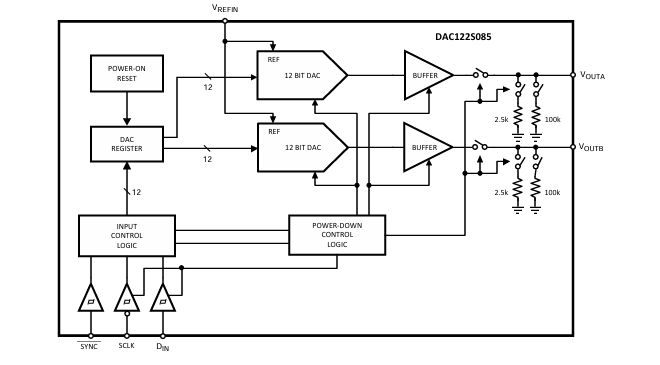

描述

在电子设计领域,数模转换器(DAC)是连接数字世界和模拟世界的关键桥梁。今天,我们将深入探讨德州仪器(TI)的DAC122S085,这是一款功能强大的12位微功耗双数模转换器,具有众多出色的特性和广泛的应用场景。

文件下载:dac122s085.pdf

产品概述

DAC122S085是一款全功能、通用的双12位电压输出数模转换器,能够在+2.7V至+5.5V的单电源下工作。在3V电源时功耗仅为0.6mW,5V电源时为1.6mW,具有低功耗的显著优势。它采用10引脚SON和VSSOP封装,其中10引脚SON封装使其成为同类产品中最小的双DAC。片上输出放大器支持轨到轨输出摆幅,三线串行接口在整个电源电压范围内的时钟速率最高可达40 MHz,相比竞品在2.7V至3.6V电源电压范围内仅25 MHz的时钟速率,具有明显优势。该串行接口还与标准SPI™、QSPI、MICROWIRE和DSP接口兼容,方便与各种设备进行连接。

产品特性与优势

特性亮点

- 确保单调性:输出不会随着输入代码的增加而降低,保证了转换的稳定性和可靠性。

- 低功耗运行:在不同电源电压下都能保持较低的功耗,适合电池供电的设备。

- 轨到轨电压输出:输出电压范围能够达到电源电压的上下限,提供了更宽的动态范围。

- 上电复位至0V:确保设备在上电时输出为0V,避免异常输出。

- 同步输出更新:可以同时更新两个通道的输出,提高了系统的响应速度。

- 宽电源电压范围:+2.7V至+5.5V的电源电压范围,增加了产品的适用性。

- 行业最小封装:小巧的封装尺寸,节省了电路板空间。

- 掉电模式:在不使用时可以进入低功耗模式,进一步降低功耗。

关键规格参数

| 参数 | 详情 |

|---|---|

| 分辨率 | 12位 |

| 积分非线性(INL) | ±8 LSB(最大) |

| 差分非线性(DNL) | +0.7 / -0.5 LSB |

| 建立时间 | 8.5 µs(最大) |

| 零码误差 | +15 mV(最大) |

| 满量程误差 | -0.75 %FS(最大) |

| 正常供电功率 | 0.6 mW(3V) / 1.6 mW(5V)(典型) |

| 掉电供电功率 | 0.3 µW(3V) / 0.8 µW(5V)(典型) |

这些参数表明DAC122S085在精度和速度方面都有出色的表现,能够满足大多数应用的需求。

功能描述

DAC部分

DAC122S085采用CMOS工艺制造,其架构由开关和电阻串组成,后面跟随一个输出缓冲器。参考电压通过VREFIN引脚外部施加,并且由所有四个DAC共享。输入编码为直二进制,理想输出电压由公式$V{OUTA,B }=V{REFIN } \times(D / 4096)$确定,其中D是加载到DAC寄存器的二进制代码的十进制等效值,这种配置确保了DAC的单调性。

输出放大器

输出放大器为轨到轨放大器,当参考电压为$V{A}$时,输出电压范围为0V至$V{A}$。不过,当输出接近电源轨时,所有放大器(包括轨到轨类型)都会出现线性度损失。因此,线性度是在小于DAC全输出范围的情况下指定的。如果参考电压小于$V{A}$,则仅在最低代码中会出现线性度损失。输出放大器能够驱动与1500 pF并联的2 kΩ负载到地或$V{A}$,具体的零码和满量程输出可参考电气特性表。

参考电压

DAC122S085使用一个由两个通道共享的外部参考电压。参考引脚VREFIN未缓冲,输入阻抗为60 kΩ,建议使用低输出阻抗的电压源驱动该引脚。参考电压范围为1.0V至$V_{A}$,可提供尽可能宽的输出动态范围。

串行接口

三线接口与SPI™、QSPI和MICROWIRE以及大多数DSP兼容,时钟速率最高可达40 MHz。写入序列从将SYNC线拉低开始,一旦SYNC为低,DIN线上的数据将在SCLK的下降沿时钟输入到16位串行输入寄存器。为避免数据误时钟到移位寄存器,关键是不要在SCLK的下降沿同时将SYNC拉低。在第16个下降时钟沿,最后一位数据被时钟输入,编程功能(如DAC通道地址、操作模式和/或寄存器内容的更改)将被执行。此时,SYNC线可以保持低电平或拉高。第16个下降时钟沿之后的任何数据和时钟脉冲都将被忽略。无论哪种情况,在通过SYNC的下降沿启动下一个写入序列之前,SYNC必须拉高到指定的最短时间。由于SYNC和DIN缓冲器在高电平时消耗更多电流,因此在写入序列之间应将它们闲置为低电平以最小化功耗。

输入移位寄存器

输入移位寄存器有16位。第一位必须设置为“0”,第二位是地址位,用于确定寄存器数据是针对DAC A还是DAC B。接下来的两位确定操作模式(如写入DAC寄存器而不更新两个DAC的输出、写入DAC寄存器并更新两个DAC的输出、写入两个DAC的寄存器并更新其输出或关闭两个输出)。移位寄存器的最后12位是数据位,数据格式为直二进制(MSB优先,LSB最后),所有0对应于0V输出,所有1对应于$V_{REFIN } - 1 LSB$的满量程输出。串行输入寄存器的内容在SCLK的第16个下降沿传输到DAC寄存器。

上电复位

上电复位电路在上电期间控制两个DAC的输出电压。上电时,DAC寄存器被填充为0,输出电压为0V,直到对设备进行有效的写入操作。

掉电模式

DAC122S085有四种掉电模式,其中两种相同。在掉电模式下,3V时电源电流降至20 µA,5V时降至30 µA。通过将OP1和OP0设置为11可将DAC122S085设置为掉电模式。由于此模式会关闭两个DAC,因此移位寄存器的前两位用于选择DAC输出的不同输出端接方式。将A1和A0设置为00或11会使输出处于高阻态(高阻抗状态),而将A1和A0设置为01或10会使输出分别通过2.5 kΩ或100 kΩ接地。在任何掉电模式下,偏置发生器、输出放大器、电阻串和其他线性电路都会关闭,但DAC寄存器的内容不受影响。在掉电模式下,通过将SYNC和DIN闲置为低电平并禁用SCLK可实现最低功耗。退出掉电模式的时间(唤醒时间)通常如交流和时序特性中所述为$twu$微秒。

应用信息

参考电源的使用

由于DAC122S085从参考输入(VREFIN)到VOUTs的路径基本上具有零电源抑制比(PSRR),因此必须为VREFIN提供无噪声的电源电压。为了充分利用DAC122S085的动态范围,电源引脚$(V_{A})$和VREFIN可以连接在一起并共享相同的电源电压。由于DAC122S085功耗极低,参考源可作为参考输入和/或电源电压。使用参考源相对于电压调节器的优点是精度和稳定性。以下是一些适合DAC122S085的参考和电源选项:

- LM4130:具有0.05%的温度精度,是DAC122S085参考源的不错选择。如果需要0至4.095V的输出范围,4.096V版本很有用。通过在LM4130的VIN引脚旁路一个0.1µF电容器,在VOUT引脚旁路一个2.2µF电容器,可以提高稳定性并降低输出噪声。它采用节省空间的5引脚SOT23封装。

- LM4050:精度为0.44%的并联参考,有4.096V和5V版本,采用节省空间的3引脚SOT23封装。在使用时,需要根据特定条件选择合适的电阻值,以确保LM4050的电流在额定范围内。

- LP3985:是一种低噪声、超低压差电压调节器,在温度范围内精度为3%。它有3.0V、3.3V和5V等版本,在低频下具有低至30 µV的噪声规格,对于某些对低频噪声敏感的应用很重要。它采用节省空间的5引脚SOT - 23和5凸块DSBGA封装。在使用时,输入需要一个1.0µF的电容,输出需要一个1.0µF且ESR在5mΩ至500mΩ之间的陶瓷电容。

- LP2980:是一种超低压差调节器,根据等级不同,在温度范围内的精度为0.5%或1.0%。有3.0V、3.3V和5V等版本。与任何低压差调节器一样,LP2980需要一个输出电容来实现环路稳定,输出电容至少应为1.0µF,2.2µF或更大的值将提供更好的性能,电容的ESR应在LP2980数据手册规定的范围内。表面贴装固体钽电容是一个不错的选择,而陶瓷电容的ESR值通常过低,铝电解电容的尺寸大且低温下ESR值可能过高,不太适合。

双极性操作

DAC122S085设计用于单电源操作,输出为单极性。但通过特定电路可以实现双极性输出,例如图35所示的电路可提供±5V的输出电压范围。如果放大器电源限制为±5V,则应使用轨到轨放大器。该电路的输出电压可通过公式$V{O}=\left(V{A} \times(D / 4096) \times((R 1+R 2) / R 1)-V{A} × R 2 / R 1\right)$计算,当$V{A}=5 ~V$且$R 1=R 2$时,$V_{O}=(10 × D / 4096)-5V$,其中D是十进制形式的输入代码。适合此应用的一些轨到轨放大器包括LMC7111、LM7301和LM8261。

与DSP/微处理器的接口

ADSP - 2101/ADSP2103接口

DAC122S085与ADSP - 2101/ADSP2103的串行接口如图36所示。DSP应设置为SPORT传输交替帧模式,通过SPORT控制寄存器进行编程,并配置为内部时钟操作、低电平有效帧和16位字长。在启用SPORT模式后,通过向Tx寄存器写入一个字来启动传输。

80C51/80L51接口

DAC122S085与80C51/80L51微控制器的串行接口如图37所示。SYNC信号来自微控制器的可编程引脚(例如P3.3),当向DAC122S085传输数据时,该线被拉低。由于80C51/80L51传输8位字节,在传输周期中只有8个下降时钟沿。为了将数据加载到DAC,在传输前8位后,P3.3线必须保持低电平,然后启动第二个写入周期传输第二个字节的数据,之后将P3.3线拉高。同时,80C51/80L51的传输例程必须注意其数据传输是LSB优先,而DAC122S085需要MSB优先的数据。

68HC11接口

DAC122S085与68HC11微控制器的串行接口如图38所示。DAC122S085的SYNC线由端口线(如图中的PC7)驱动,与80C51/80L51类似。68HC11应将其CPOL位配置为0,CPHA位配置为1,这样MOSI输出上的数据在SCLK的下降沿有效。PC7被拉低以向DAC传输数据,68HC11以8位字节传输数据,有8个下降时钟沿,数据以MSB优先传输。在传输前8位后,PC7必须保持低电平,然后启动第二个写入周期传输第二个字节的数据,之后将PC7拉高以结束写入序列。

Microwire接口

DAC122S085与Microwire兼容设备的接口如图39所示。数据在SK信号的上升沿时钟输出,因此Microwire设备的SK需要在驱动DAC122S085的SCLK之前进行反相。

布局、接地和旁路

为了获得最佳精度和最小噪声,包含DAC122S085的印刷电路板应具有单独的模拟和数字区域,这些区域由模拟和数字电源平面的位置定义,且两个平面应位于同一板层。应使用单个接地平面,如果数字返回电流不流经模拟接地区域,则首选单个接地平面。通常,单个接地平面设计会采用“围栏”技术来防止模拟和数字接地电流混合。只有在“围栏”技术不足时才使用单独的接地平面,且单独的接地平面必须在一个地方连接,最好靠近DAC122S085。特别要注意确保具有快速边沿速率的数字信号不会越过分割的接地平面,它们必须始终在其走线下方有连续的返回路径。DAC122S085的电源应使用10µF和0.1µF的电容进行旁路,0.1µF电容应靠近设备的电源引脚。10µF电容应为钽类型,0.1µF电容应为低ESL、低ESR类型。DAC122S085的电源仅应用于模拟电路。此外,应避免模拟和数字信号交叉,时钟和数据线应位于电路板的元件侧,并具有受控的阻抗。

总结

DAC122S085凭借其低功耗、高精度、轨到轨输出、高速串行接口等众多优点,成为电池供电仪器、数字增益和失调调整、可编程电压和电流源、可编程衰减器等应用的理想选择。在实际设计中,我们需要根据具体的应用需求,合理选择参考电源、进行接口设计以及优化电路板布局,以充分发挥DAC122S085的性能优势。希望本文能为电子工程师们在使用DAC122S085进行设计时提供有价值的参考。大家在使用过程中有任何问题或者经验,欢迎在评论区分享交流。

-

探索MAXIM MX7541:12位CMOS乘法数模转换器的卓越性能与应用2026-04-22 162

-

探索DAC1282:低失真数模转换器的卓越性能与应用2026-04-18 488

-

探索DAC101S101:10位微功耗数模转换器的卓越性能与应用2025-12-01 1172

-

DAC084S085 8位微功耗四通道数模转换器产品文档2025-11-29 1271

-

深入剖析DAC128S085:高性能12位八通道数模转换器2025-11-27 815

-

探索DAC101C08xx:10位微功耗数模转换器的卓越性能与应用2025-11-26 1142

-

DAC122S085通用双通道12位电压输出数模转换器(DAC)数据表2024-07-26 737

-

具有轨对轨输出的微功耗数模转换器评估板的资料概述2018-05-14 1278

-

DAC128S085,12位10位8位八进制微功耗数模转换器评估板的详细资料概述2018-05-10 2196

全部0条评论

快来发表一下你的评论吧 !