深入剖析ADS5546:高性能14位ADC的卓越之选

电子说

描述

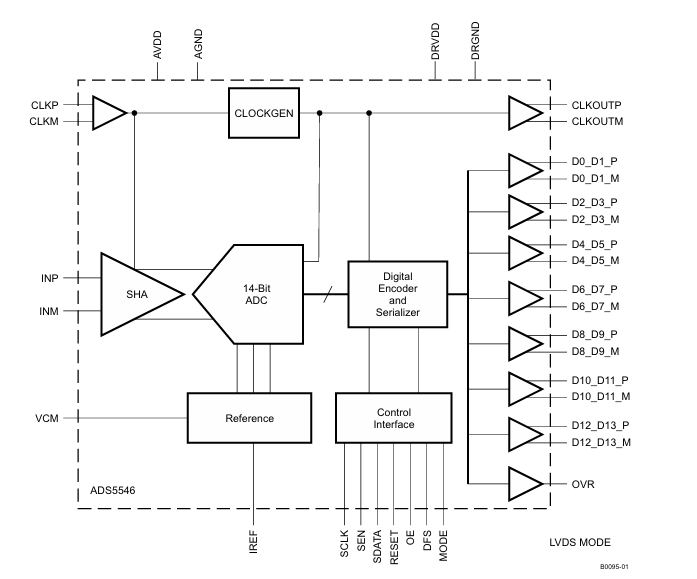

在当今的电子设计领域,模数转换器(ADC)的性能直接影响着整个系统的精度和效率。ADS5546作为一款高性能的14位、190 MSPS ADC,凭借其出色的特性和广泛的应用场景,成为了众多工程师的首选。今天,我们就来深入剖析这款ADC,了解它的技术细节和应用要点。

文件下载:ads5546.pdf

核心特性,铸就卓越性能

高采样率与高精度

ADS5546具备高达190 MSPS的最大采样率,能够快速准确地采集信号。同时,它拥有14位的分辨率,且无丢失码,确保了数据的高精度。在70 - MHz IF条件下,其SNR可达73.2 - dBFS,SFDR可达87 - dBc(0 dB增益),为信号处理提供了出色的动态范围。

灵活的输出选项

该ADC提供了双数据速率(DDR)LVDS和并行CMOS输出选项,可根据不同的应用需求进行灵活选择。此外,它还支持可编程增益,最高可达6 dB,能够在高IF条件下实现SNR/SFDR的权衡。

低功耗设计

ADS5546在功耗方面表现出色,总功耗仅为1.1 W。同时,它还具备在较低采样率下的低功耗模式,进一步降低了系统的能耗。

其他特性

ADS5546还具有内部采样和保持功能、时钟占空比稳定器、无需外部参考去耦、支持内部和外部参考、可编程输出时钟位置等特性,为设计带来了极大的便利。

应用广泛,满足多样需求

ADS5546的应用场景十分广泛,涵盖了无线通信基础设施、软件定义无线电、功率放大器线性化、802.16d/e测试和测量仪器、高清视频、医学成像、雷达系统等多个领域。其高性能和灵活性使其能够适应不同的应用需求,为系统的稳定运行提供了有力保障。

技术细节,彰显专业品质

电气特性

ADS5546的电气特性表现优异。在模拟输入方面,其差分输入电压范围为2 Vpp,输入带宽可达500 MHz(- 3 dB,源阻抗50 Ω)。在参考电压方面,内部参考误差较小,VCM输出电流能力较强。此外,它的直流精度高,无丢失码,DNL和INL指标优秀。

数字特性

在数字特性方面,ADS5546的LVDS和CMOS输出规格经过了详细的表征。在CMOS模式下,高电平输出电压为3.3 V,低电平输出电压为0 V;在LVDS模式下,高电平输出电压为1375 mV,低电平输出电压为1025 mV。

时序特性

ADS5546的时序特性也非常重要。在LVDS和CMOS模式下,它的孔径延迟、孔径抖动、数据建立时间、数据保持时间等参数都有明确的规定,确保了数据的准确传输。

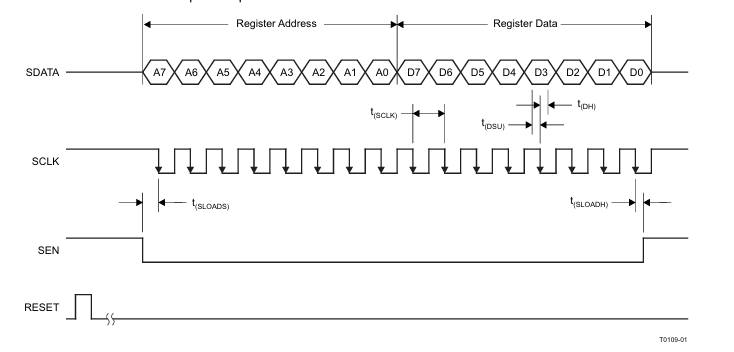

编程模式,实现灵活配置

ADS5546提供了多种可编程特性,可通过并行接口控制、串行接口编程或两者结合的方式进行配置。在并行接口控制模式下,可直接通过连接并行引脚到正确的电压电平来控制ADC的某些模式;在串行接口编程模式下,需先将内部寄存器复位到默认值,再通过SEN、SDATA和SCLK引脚访问内部寄存器。

应用信息,指导设计实践

模拟输入

ADS5546的模拟输入采用了基于开关电容的差分采样和保持架构,具有良好的AC性能。在驱动电路设计方面,建议在每个输入引脚串联一个5 - Ω电阻,以抑制封装寄生效应引起的振铃,并为共模开关电流提供低阻抗路径。

参考

该ADC具有内置的内部参考,无需外部组件。在外部参考模式下,可通过VCM引脚设置参考电压,生成REFP和REFM电压。

时钟输入

ADS5546的时钟输入可采用差分或单端驱动方式,建议采用差分驱动以降低对共模噪声的敏感性。同时,为了获得最佳性能,应使用低抖动的时钟源,并可对时钟源进行带通滤波。

可编程增益

ADS5546支持0 dB到6 dB的可编程增益,可根据实际需求进行调整,以实现SNR/SFDR的优化。

电源管理

ADS5546具有三种电源管理模式,包括全局STANDBY、输出缓冲器禁用和输入时钟停止,可有效降低系统功耗。

设计考虑,确保系统稳定

接地

在电路板设计中,采用单一接地平面,并对模拟、数字和时钟部分进行清晰分区,可获得良好的性能。

电源去耦

由于ADS5546内部已包含去耦功能,可使用最少的外部去耦电容。建议将去耦电容放置在靠近转换器电源引脚的位置,并为模拟和数字电源引脚使用单独的电源,以隔离数字开关噪声。

输出电阻

在每个输出线上放置50到100 Ω的串联电阻,可有效隔离输出与大负载电容,减少开关噪声。

散热设计

将封装底部的暴露焊盘焊接到接地平面,可获得最佳的散热性能。

总结

ADS5546作为一款高性能的14位ADC,凭借其出色的特性、广泛的应用场景和灵活的配置方式,为电子工程师提供了一个优秀的选择。在实际设计中,我们需要充分了解其技术细节和应用要点,合理进行电路设计和参数配置,以确保系统的稳定运行和高性能表现。你在使用ADS5546或其他ADC时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

深入剖析ADS574:高性能CMOS模数转换器的卓越之选2026-04-18 117

-

深入剖析LTC1744:高性能14位50Msps ADC的卓越之选2026-04-08 133

-

深入剖析LTC2246H:高性能14位ADC的卓越之选2026-04-07 334

-

AD7942:高性能14位ADC的卓越之选2026-04-03 153

-

深入剖析 LTC2378 - 20:高性能 20 位 SAR ADC 的卓越之选2026-03-31 364

-

深入剖析LTC2270:高性能16位双路ADC的卓越之选2026-03-30 141

-

深入剖析ADS5421:高性能14位ADC的卓越之选2025-12-05 1414

-

ADS5546高性能14位、190 MSPS A/D转换器数据表2024-07-27 445

-

具有DDR LVDS CMOS输出14位190MSPS的模数转换器ADS5546的详细概述2018-05-15 924

-

ADS5546,pdf (14-Bits 190 MSPS ADC With DDR LVDS/CMOS Outputs2010-06-04 1146

全部0条评论

快来发表一下你的评论吧 !