德州仪器ADS5232:高性能12位ADC的深度剖析

电子说

描述

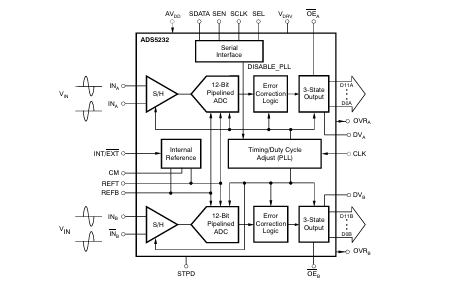

在当今的电子设计领域,模拟到数字的转换是许多系统中的关键环节。德州仪器(TI)的ADS5232作为一款双路、高速、高动态范围的12位流水线式模数转换器(ADC),在通信、测试设备、医疗成像等多个领域都有着广泛的应用。今天,我们就来深入了解一下这款ADC的特性、性能以及应用中的注意事项。

文件下载:ads5232.pdf

1. 关键特性

1.1 电源与功耗

ADS5232采用单一+3.3V电源供电,具有低功耗的特点。内部参考模式下总功耗为371mW,外部参考模式下为335mW。这种低功耗设计使得它在对功耗敏感的应用中表现出色。

1.2 高信噪比

在输入频率$f_{IN}=5MHz$时,SNR可达70.7dBFS,能够有效抑制噪声,保证信号的高质量转换。

1.3 低DNL与灵活输入范围

DNL低至±0.3LSB,确保了转换的线性度。输入范围灵活,可在$1.5V{PP}$到$2V{PP}$之间设置,适应不同的信号源。

1.4 内部或外部参考

支持内部和外部参考模式,用户可以根据实际需求进行选择。在多通道系统中,禁用内部参考,使用外部参考可以提高跟踪性能。

2. 性能指标

2.1 直流精度

- DNL和INL:在$f_{IN}=5MHz$时,DNL为 -0.9 到 +0.3LSB,INL为 -2.5 到 ±0.4LSB,保证了转换的准确性。

- 偏移误差和增益误差:偏移误差在 -0.75%FS 到 +0.75%FS 之间,增益误差在 -3.5%FS 到 +3.5%FS 之间。

2.2 交流性能

- SFDR:在不同输入频率下,SFDR表现优异,如$f{IN}=5MHz$时为75dBc,$f{IN}=32.5MHz$时为85dBc。

- SNR和SINAD:在$f_{IN}=5MHz$时,SNR为70.7dBFS,SINAD为70.3dBFS,能够有效区分信号和噪声。

2.3 时序特性

数据延迟为6个时钟周期,不同采样率和PLL状态下,数据建立时间、保持时间等时序参数有所不同。例如,在65MSPS且PLL开启时,数据建立时间为2 - 3.2ns,保持时间为6.3 - 8.5ns。

3. 应用电路设计

3.1 输入配置

- 差分采样架构:采用差分采样保持架构,输入有低通RC滤波器,可滤除噪声。采样电路使用两个4pF电容,有效减少干扰。

-

输入驱动配置:

- 变压器耦合接口:适用于单端信号源转换为差分信号驱动ADC,可选择有中心抽头的RF变压器,通过中心抽头施加共模DC电压,实现信号转换。

- DC耦合输入与差分放大器:如使用THS4503差分放大器,可实现单端到差分的转换,降低成本。同时,将$V_{OCM}$引脚连接到ADC的共模引脚,设置必要的偏置电压。

3.2 参考电路

- 内部参考:通过ISET引脚的外部电阻设置偏置电流,使用56.2kΩ电阻可产生约20µA的内部参考电流。内部参考可提供共模电压输出,典型值为+1.5V。

- 外部参考:在INT/EXT引脚置低时,可使用外部参考电压。外部参考电压范围为$REF{T}$在 +1.875V 到 +2.0V之间,$REF{B}$在 +1.0V 到 +1.125V之间,可设置满量程输入范围在$1.5V{PP}$到$2V{PP}$之间。

3.3 时钟输入

ADS5232需要单端时钟源,时钟抖动对SNR影响较大。随着输入频率增加,建议使用低抖动的时钟源,以保持良好的信噪比。转换器本身的时钟输入为CMOS兼容逻辑输入,输入阻抗约为5pF。

4. 注意事项

4.1 电源与布局

- 模拟和数字电源都应使用低噪声电源,避免数字电源的开关噪声耦合到转换器中。

- 所有接地引脚应直接连接到模拟地,$AV_{DD}$和VDRV引脚应使用陶瓷电容进行旁路,以减少高频噪声。

- 布局时应保持模拟信号迹线与数字线分离,差分输入应采用对称布局,减少相位偏移。

4.2 输出负载

数据输出线的电容负载应尽量保持在15pF以下,过高的电容负载会导致动态电流增大,影响器件性能。必要时可使用外部缓冲器或锁存器来减少电容负载。

4.3 功率管理

ADS5232有多种功率管理模式,如时钟速度低于2MSPS或STPD引脚置高时,会进入掉电模式。掉电模式下功耗低于90mW,恢复时间与外部电容值有关。

5. 总结

ADS5232凭借其高性能、低功耗和灵活的配置,为电子工程师提供了一个优秀的模数转换解决方案。在实际应用中,我们需要根据具体需求合理选择参考模式、输入驱动方式和时钟源,同时注意电源布局和输出负载等问题,以充分发挥其性能优势。你在使用类似ADC时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

AD9625:高性能12位ADC的深度剖析与应用指南2026-03-30 188

-

德州仪器ADS7841:12位4通道串行输出采样ADC的技术解析2025-12-10 783

-

德州仪器ADS825:高性能10位ADC的深度解析2025-12-09 789

-

德州仪器ADS1605/6:高性能16位ADC的设计与应用解析2025-12-04 848

-

深度剖析ADS5521:高性能12位ADC的卓越之选2025-12-01 668

-

深度剖析ADS5273:一款高性能8通道12位ADC2025-11-30 1115

-

探索ADS61B23:高性能12位ADC的卓越之旅2025-11-26 836

-

ADS5232在单端输入的情况下,输入范围是多少?2025-01-10 416

-

ADS5232高动态范围、12位流水线式模数转换器(ADC)数据表2024-07-29 412

-

德州仪器推出同步采样ADC ADS8556、ADS8557以2009-11-04 1984

全部0条评论

快来发表一下你的评论吧 !