深入剖析ADS5272:8通道12位65MSPS ADC的卓越性能与应用指南

电子说

描述

在当今高速数据采集和处理的时代,高性能模数转换器(ADC)的需求日益增长。ADS5272作为一款由德州仪器(TI)推出的8通道、12位、65MSPS ADC,凭借其出色的性能和丰富的特性,在众多领域得到了广泛应用。本文将对ADS5272进行全面深入的剖析,为电子工程师们提供一份详尽的设计指南。

文件下载:ads5272.pdf

一、ADS5272的特性亮点

1. 集成PLL与LVDS接口

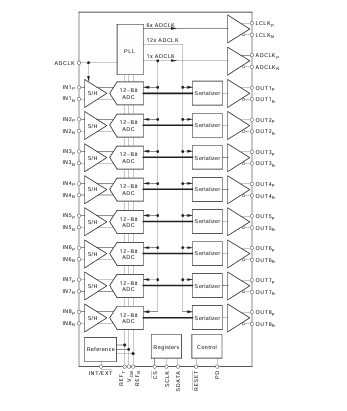

ADS5272集成了锁相环(PLL),可将输入的ADC采样时钟乘以12倍,生成的高频LVDS时钟用于数据序列化和传输。每个内部ADC的字输出被序列化后,可选择先传输最高有效位(MSB)或最低有效位(LSB)。除了8个数据输出外,还会传输位时钟和字时钟,位时钟速度是采样时钟的6倍,字时钟速度与采样时钟相同。这种设计大大简化了数据传输过程,提高了数据传输效率。

2. 高性能指标

- 采样率与分辨率:最大采样率可达65MSPS,12位分辨率确保了高精度的数据采集,且无缺失码,保证了数据的完整性。

- 低功耗:内部参考模式下总功耗为983mW,外部参考模式下为917mW,采用CMOS技术,同时具备同时采样保持功能,有效降低了功耗。

- 高信噪比:在5MHz中频时,信噪比(SNR)可达71.1dBFS,为信号处理提供了良好的基础。

3. 灵活的参考模式

ADS5272既提供内部参考,也可选择外部参考驱动。内部参考模式能实现最佳性能,满足不同应用场景的需求。

4. 其他特性

- 3.3V数字/模拟电源,适应常见的电源系统。

- 序列化LVDS输出,减少了接口线数量和封装尺寸。

- 集成帧和位模式,可选择双倍LVDS时钟输出电流,提供四种LVDS电流模式,增强了系统的灵活性和可配置性。

二、应用领域广泛

ADS5272的高性能使其在多个领域都有出色的表现,主要应用包括:

- 便携式超声系统:高精度的数据采集和低功耗特性,满足了便携式设备对性能和功耗的双重要求。

- 磁带驱动器:高速采样率和高分辨率确保了数据的准确读取和写入。

- 测试设备:为测试设备提供了可靠的信号采集和处理能力。

- 光网络:在光网络中,可用于信号的监测和处理,保证网络的稳定运行。

三、关键参数与性能指标

1. 电气特性

- 直流精度:无缺失码,差分非线性(DNL)和积分非线性(INL)控制在较小范围内,确保了转换的准确性。

- 功率要求:不同参考模式下的功率消耗明确,方便工程师进行功耗设计。

- 参考电压:内部和外部参考电压的范围和精度都有详细规定,为参考电路设计提供了依据。

2. 交流特性

- 动态特性:包括无杂散动态范围(SFDR)、谐波失真(HD2、HD3)、信噪比(SNR)、信噪失真比(SINAD)和有效位数(ENOB)等指标,在不同输入频率下都有良好的表现,反映了ADC在动态信号处理方面的能力。

3. LVDS数字数据和时钟输出

详细规定了LVDS输出的直流和交流特性,如输出电压、输出阻抗、时钟占空比、数据建立和保持时间等,确保了LVDS接口的稳定可靠运行。

四、工作原理与设计要点

1. 整体架构

ADS5272由高性能采样保持电路和12位ADC组成,输入的12位数据被序列化后以LVDS格式输出。8个通道共用一个ADCLK输入,通过时钟树网络生成各通道的采样时钟,保证了各通道的一致性。

2. 模拟输入驱动

模拟输入采用内部偏置,推荐在每个输入引脚串联一个大于20Ω的电阻。输入采样电容为4pF,外部交流耦合电容的选择取决于最低工作频率下的衰减要求。

3. 参考电路设计

参考电路设计对于保证各通道增益匹配至关重要。通过内部参考电压缓冲器和生产时的参考电压微调,确保了同一芯片内和不同芯片间的参考电压匹配。同时,可通过外部电阻设置内部偏置电流,控制设备的工作功率。

4. 时钟设计

使用时钟树网络确保各通道的孔径延迟和抖动一致,内部PLL生成内部时钟,保证了50%的占空比,并生成12倍时钟用于数据序列化。输入时钟需自由运行,最低采样率约为20MSPS。

5. LVDS缓冲器

LVDS缓冲器有四种电流设置,默认电流为3.5mA。数据以LSB先输出,可通过寄存器设置改为MSB先输出。支持去斜模式、同步模式和自定义模式,在掉电模式下LVDS输出被三态化。

6. 噪声耦合问题

为减少高速混合信号中的噪声耦合,芯片明确划分了模拟和数字域,采用不同的电源和地引脚,并推荐使用单独的电源和地平面,以降低噪声干扰。

7. 掉电与复位

ADS5272具有掉电功能,可通过PD引脚或监测时钟状态进入掉电模式,恢复时间与外部电容有关。复位操作可使内部寄存器恢复到默认值,确保设备正常工作。

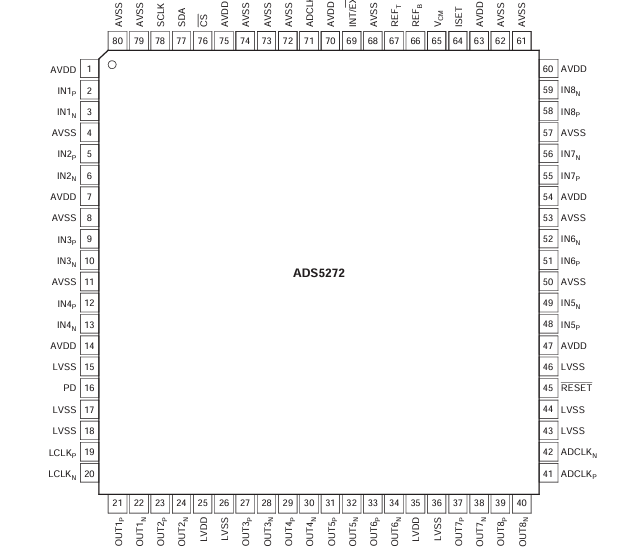

五、PCB布局与封装考虑

ADS5272采用80引脚PowerPAD热增强封装,在PCB设计时需充分考虑其热效率。可参考TI的相关技术文档,如SLMA004和SLMA002,以优化PCB布局,提高散热性能。

六、总结与展望

ADS5272作为一款高性能的8通道ADC,凭借其丰富的特性、出色的性能指标和灵活的设计,为电子工程师们提供了一个强大的工具。在实际应用中,工程师们需根据具体需求,合理设计参考电路、时钟电路和PCB布局,以充分发挥ADS5272的优势。随着技术的不断发展,相信ADS5272将在更多领域展现其卓越的性能,为高速数据采集和处理带来更多的可能性。

电子工程师们在使用ADS5272进行设计时,不妨多尝试不同的配置和参数设置,结合实际应用场景进行优化,以实现最佳的系统性能。同时,关注TI的最新技术和应用案例,不断学习和借鉴,提升自己的设计水平。你在使用ADS5272或其他类似ADC时遇到过哪些问题?又是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

MAX19505:高性能双通道8位65Msps ADC的深度剖析2026-04-08 113

-

深入剖析LTC2489:16位2/4通道ΔΣ ADC的卓越性能与应用2026-04-07 157

-

AD9229:高性能四通道12位ADC的技术剖析与应用指南2026-04-03 166

-

深入剖析AD7328:8通道12位带符号ADC的卓越性能与应用2026-04-02 263

-

深入解析AD9637:八通道12位高速ADC的卓越性能与应用2026-03-31 196

-

ADS5242:高性能4通道12位65MSPS ADC的深度剖析2025-11-30 897

-

深入解析ADS8471:16位、1-MSPS采样ADC的卓越性能与应用2025-11-26 713

-

ADS5242高性能、65MSPS、4通道模数转换器(ADC)数据表2024-07-29 458

-

ADS42xx双通道、14位/12位、160MSPS/125MSPS/65MSPS、超低功耗ADC数据表2024-07-17 898

-

8通道12位带串行LVDS接口的ADS52722020-09-23 1909

-

8通道12位65MSPS模数转换器ADS5222的详细资料免费下载2018-05-24 1059

全部0条评论

快来发表一下你的评论吧 !