在QuartusII开发平台上实现基于FPGA的音乐演奏电路的设计

描述

1 系统的设计要求

应用VHDL硬件描述语言,设计一个乐曲硬件演奏电路,它能将一首预先设置存储好的乐曲自动播放出来,除此之外,也能够通过按键的方式输入音符,使其具备简易电子琴的功能。通过此项研究,能够深切的体会利用EDA工具开发的优越性,在此基础上,对乐曲硬件演奏电路功能进行丰富,具有一定的社会实用性。

根据硬件演奏电路的功能进行全局分析,采用自上至下的设计方法,从系统总体要求出发,逐步将设计内容细化,最后完成系统结构的整体设计。将功能分为以下几个部分,1)实现预先设置乐曲的播放功能;2)实现预置乐曲的暂停和继续播放实时控制功能;3)实现预置多首乐曲间的切换功能。

预置乐曲,本文选取了《梁祝》的一段作预置,作预置时,需要将乐曲音符转换成相应的代码,通过计算逐一将音符转换成代码,通过EDA开发平台quartusii6.0进行乐曲定制。

为了提供乐曲发音所需要的发音频率,编写数控分频器程序,对单一输入高频,进行预置数分频,生成每个音符发音的相应频率。

为了给分频提供预置数,需要计算分频预置数。

对每部分结构单元逐一进行编译,生成相应的元器件符号,并对独立结构单元功能进行仿真。

2 系统的详细设计方案

2.1 顶层实体描述

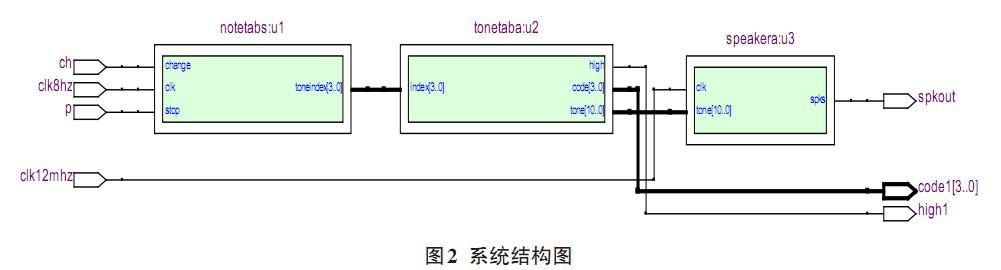

按照EDA开发流程,采用VHDL硬件描述语言开发,将乐曲硬件演奏电路设计进行模块化分解,层次化设计,分成几个单独的结构体,每个结构体实现部分功能,最后,经顶层文件将各单独结构体进行综合,实现乐曲硬件演奏。

有四个输入,三个输出端口。

四输入端口分别是:clk8hz端口,作为节拍脉冲信号输入端口;clk12mhzZ端口,作为发音频率初始信号输入端口;P输入端口,作为控制歌曲暂停和继续播放的输入端口。ch输入端口,作为控制歌曲之间切换播放的输入端口。

三输出端口分别是:code1输出端口,作为音符简码输出LED显示端口;high1输出端口,作为音符高8度指示端口;spkout输出端口,作为乐曲的声音输出端口。

2.2 模块划分

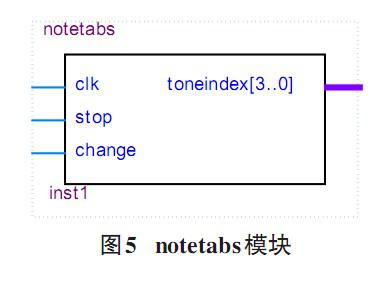

本系统主要由三个功能模块组成:notetabsvhd,tonetaba.vhd和speakera.vhd.第一部分notetabs,地址发生器,实现按节拍读乐谱的功能;第二部分tonetaba,查表电路,为speakera提供分频预置数,实现乐曲译码输出CODE[3:0];第三部分speakera,产生发音频率,实现乐曲播放。系统结构图如图2.

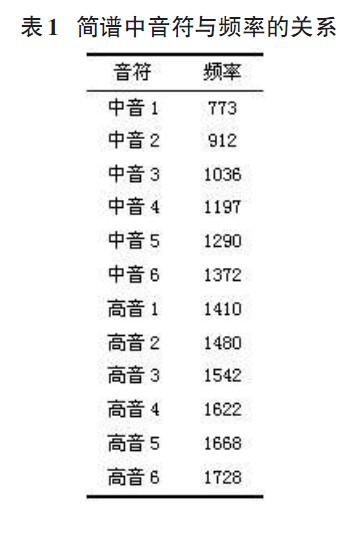

为了实现乐曲的播放,首先需要将曲谱定制到音符数据ROM里面,然后才能按照一定的节拍从ROM中读出曲谱。由于所选曲子中不含低音,转换关系如表1所示。

2.3 模块描述

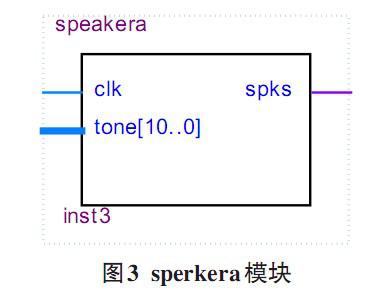

sperkera是一个数控分频器,由其clk端输入一个12mhz信号,通过speakera分频后,由spkout,通过一d触发器,pinlv变为原来的二分之一,sperakera对clk的输入信号的分频比由11位tone[100]决定,spkout的输出频率为音符的音调。

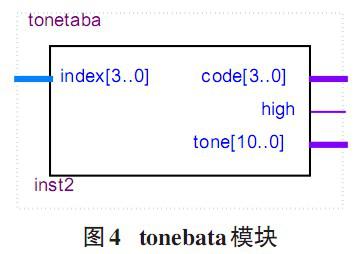

tonebata的功能首先是为speakera提供分频预置数,此数的停留时间即为音符的节拍值,此模块为歌曲简谱码提供对应的分频预置查表电路,音符停留时间由clk的输入频率决定,再次为4hz.

3 系统的方案实现

3.1 各模块仿真及描述

notetabs作为音符rom的地址发生器,此模块中设置了一个8位2进制计数器,频率为4hz,即为4个音符一秒时间四四拍的4分音符。notetabs计数器计数器按4hz时钟频率做加法计数,当stop为高电平时停止加法运算,而当change可设置rom中数据的跳转,rom通过toneindex[30]端口输向tonetaba模块。乐曲就演奏起来了。

由图6 sperkera仿真波形可以看出,当clk输入时钟频率为12mhz时,输出端信号clk输出的频率,随tong信号的不同,输出不同频率的声音信号。

由图7tonetaba信号的仿真波形,可以看出,当输入信号index[30]输入不同信号值,code输出端输出音符的显示,high为音符高位信号,tone大于7时high为高电平。

图8为notetabs仿真波形,当clk输入时钟信号,toneindex[30]端从rom中读入音符数据,当输入端口stop为“1”时,暂停从rom中读入数据,stop为“0”继续读取音符信号,change为高低电平时,模块分别读取rom不同位置的数据。

3.2 顶层电路仿真及描述

clk8hz端输入8hz时钟信号,另一个clk12mhz输入12mhz时钟信号,系统将自动从music.mif中读取音符信号,以频率不同输出到spkout,同时输出到显示端口,和高音端口,code1[30],high1.p端口可以是音符暂停输出(高电平时),ch端口控制歌曲间的切换。

4 硬件测试及说明

选择实验电路模式1,将引脚锁定时clk12mhz于clock9连接,短路帽clock接12mhz.clk8hz与clock2连接。发音输出spkout接speaker.简谱码输出code1由数码管5显示,high高8度指示由发光管d5指示,p与按键d16连接,ch与的15连接。最后向目标芯片下载适配后的sof逻辑设计文件。

5 结论

本次设计在EDA开发工具QuartusII平台上,应用语言层次化和模块化的设计方法,通过音符编码的设计思想,预先定制乐曲,在此基础上设计了一个乐曲硬件演奏电路,经过对整体进行模块化分析、编程、综合、仿真及最终下载,完整实现简易音乐器的播放功能。

-

谁能用stm32f103ze帮我做个双字节音乐演奏的程序,感激不尽...2014-12-10 2549

-

结合闹钟与电子音乐演奏的综合项目适合初学者的项目。2015-12-14 6946

-

如何去实现一种基于51单片机的音乐盒设计2021-11-19 1522

-

如何利用Arduino与蜂鸣器实现音乐的演奏呢2022-02-14 1276

-

单片机音乐程序教程2010-06-03 931

-

定时循环音乐演奏电路图2009-05-08 537

-

SK--111声控音乐演奏器电路图2009-06-08 1286

-

音乐演奏器设计2009-08-02 1997

-

eda音乐演奏程序2016-12-09 938

-

在FPGA平台上实现对DPA攻击的电路级防护技术2017-11-24 3224

-

基于Proteus的单片机演奏音乐的实现[图]2018-01-18 4136

-

基于Proteus单片机的音乐演奏实现系统2018-04-08 6405

-

采用FPGA DIY开发板控制自动演奏音乐2018-06-20 2767

-

使用PLD器件和VHDL语言实现数字系统的电子密码锁设计2019-04-28 4295

-

在FPGA多媒体开发平台DE2上实现音乐流水灯控制系统的设计2018-10-07 4612

全部0条评论

快来发表一下你的评论吧 !