在FPGA上实现单精度浮点加法运算器算法的设计

描述

图像处理通常采用软件或者数字信号处理器(DSP)实现。如果利用软件实现,运行时会耗费较多的PC资源,而且算法越复杂时耗费的资源就越多,对于需要高速处理的情况不适用;而如果采用DSP实现,提高并行性的同时指令执行速度必然会提高,较高的指令速度可能导致系统设计复杂化,并增加功耗和成本。新一代的低功耗现场可编程门阵列(FPGA)凭借其强大的高速并行能力,日益成为高速实时图像处理的主流器件。单精度浮点加法运算是数字图像处理的最基础的数据运算方式,在此介绍一种在FPGA上实现单精度浮点加法运算的方法。

1 IEEE 754单精度浮点数存储格式分析

1.1 实数的IEEE 754表示形式

在计算机系统的发展过程中,曾经提出过多种方法表示实数,但是到目前为止使用最广泛的是浮点数表示法。相对定点数而言,浮点数利用指数,使小数点的位置可以根据需要而上下浮动,从而可以灵活地表达更大范围的实数。电子电气工程师协会(Institute of Electricaland Electronics Engineers,IEEE)在1985年制定的IEEE754(IEEE Standard fOr Binary Floating-Point Arithme-tic,ANSI/IEEE Std 754-1985)二进制浮点运算规范,是浮点运算部件事实上的工业标准。一个实数V在IEEE754标准中可以用V=(-1)S×M×2E表示,说明如下:

(1)符号S决定实数是正数(S=0)还是负数(S=1),对于数值0的符号位特殊处理。

(2)有效数字M是二进制小数,M的取值范围在1≤M《2或0≤M《1。

(3)指数E是2的幂,它的作用是对浮点数加权。

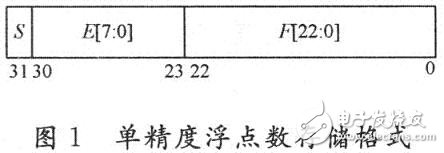

1.2 IEEE单精度浮点格式

浮点格式是一种数据结构,它规定了构成浮点数的各个字段。IEEE 754浮点数的数据位被划分为3个字段,对3个字段参数进行编码:

(1)一个单独的符号位S直接编码符号S。

(2)K位的偏置指数E编码指数E,移码表示。

(3)N位的小数.f编码有效数字M,原码表示。

IEEE单精度浮点格式共32位,包括3个构成字段:23位小数F,8为偏置指数E,1位符号S。将这些字段连续存放在一个32位字里,并对其进行编码。其中O~22包含23位的小数F;23~30包含8位指数E;第31位包含符号S。如图1所示。

2 单精度浮点加法器的设计与实现

2.1 单精度浮点加法器的算法设计

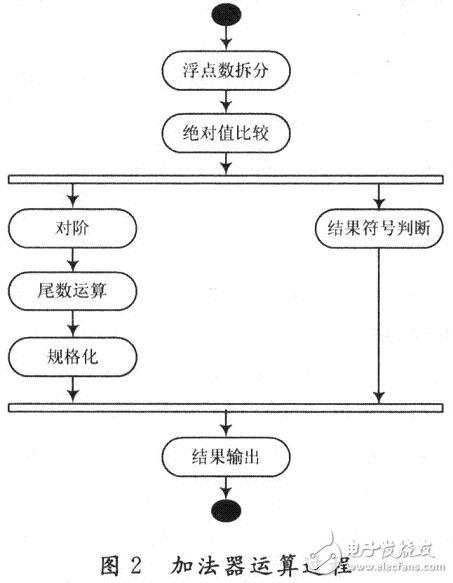

浮点加法器首先对浮点数拆分,得到符号、阶码、尾数。对拆分结果进行绝对值比较,得到大的阶码、阶差和比较结果输出。然后进行对阶,通过移位小的尾数,得到相同大阶。对尾数进行尾数加减运算,得到的结果进行规格化,最后结合规格化结果运算结果符号输出,得到结果输出。加法器运算过程如图2所示。

2.2 单精度浮点加法器的实现

2.2.1 总体设计

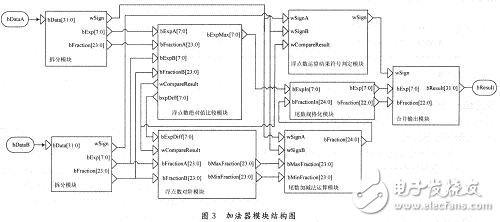

浮点加法器包括两个浮点数拆分模块、绝对值比较模块、浮点数运算结果判定模块、对阶模块、尾数加减运算模块、尾数规格化模块、合并输出模块。其中对阶模块包括尾数交换,尾数移位两个子模块;尾数加减运算模块尾数运算符号判定,尾数加减两个子模块。两个浮点数拆分模块分别将两个浮点数拆分成符号、阶码、尾数3部分,绝对值比较模块通过对两个浮点数的绝对值大小的比较得到大阶,阶差和绝对值比较结果,大阶直接输出;对阶模块然后实现对小阶的尾数进行移位,将小阶与大阶对齐,并对尾数进行移位;尾数加减运算模块判定尾数运算符号后,进行尾数运算;尾数规格化模块对结果完成尾数规格化,同时调整阶码;最后结合浮点数运算结果判定模块的符号输出,经过合并输出模块,得到结果输出。总体设计框图如图3所示。

2.2.2 各模块设计实现说明

(1)拆分模块。该模块将输入的浮点数拆分成符号位、价码、尾数3部分。符号位信号wSign,指数位信号bExp[7:0],尾数位信号bFraction[23:0]。

(2)浮点数绝对值比较模块。该模块通过对输入浮点的阶码及尾数的比较,相应得出wCompareResult,bExpDiff,bExpMax三种信号输出。当bExpA≥bEx-pB时:wCompareResult=1,bExpDiff=bExpA-bEx-pB,bExpMax=bExp;当bExpA《bExpB时:wCom-pareResult=0,bExpDiff=bExpB-bExpA,bExpMax=bExpB。

(3)浮点数运算结果符号判定模块。浮点数符号运算结果判别模块通过操作数bDataA,bDataB符号位及wCompareResult信号的输入判定运算结果数的输出。

(4)浮点数对阶模块。对阶模块根据wCompare-Result的结果对输入的操作数尾数bFractionA和bFractionB进行操作。当wCompareResult=1时,对bFractionB进行右移位,移位量为bExpDiff,并且将移位后的结果作为bMinFraction输出,将bFractionA作为bMaxFraction直接输出;反之对bFractionA进行右移位,移位量为bExpDiff,并且将移位后的结果作为bMinFraction输出,将bFractionB作为bMaxFraction直接输出。

(5)浮点数对阶模块。此模块实现对阶后的尾数的加减运算,然后输出结果尾数的值。当wSignA,wSignB同号时,尾数bMaxFraction与bMinFraction相加的结果作为bFraction输出;当wSignA,wSignB异号时,尾数bMaxFraction与bMinFraction相减的结果作为bFraction输出。

(6)尾数规格化模块。尾数bFractionIn[24:0]通过判定从左边第一次不为0的位后,将此位数左移到第一位隐藏位,相应添加尾数补0,共计24位。同时,将阶码调整,再隐藏隐藏位,调整后的阶码和尾数以bExp,bFraction输出。

(7)合并输出模块。将浮点数运算结果符号判定模块的输出信号wSign与尾数规格化模块的输出信号bExp,bFraction合并,得到输出结果。

3 结 语

介绍一种在FPGA上实现的单精度浮点加法运算器,运算器算法的实现考虑了FPGA器件本身的特点,算法处理流程的拆分和模块的拆分,便于流水设计的实现。该加法器在参与设计的多款CPCI总线图形控制器图形加速子系统上得到实际的应用和检验,在处理速度方面表现出很强的适用性。

-

使用Simulink自动生成浮点运算HDL代码(Part 1)2025-10-22 257

-

verilog语音实现浮点运算2024-03-25 899

-

浮点LMS算法的FPGA实现2023-12-21 1983

-

单精度和双精度浮点数的区别2023-12-15 7666

-

求一种在FPGA上实现单精度浮点加法运算的方法2021-04-29 1343

-

为什么研究浮点加法运算,对FPGA实现方法很有必要?2019-07-05 4185

-

针对FPGA或ASIC部署的浮点算法2018-09-11 4785

-

浮点运算单元的FPGA实现2018-04-10 1595

-

一阶泰勒级数单精度倒数算法2017-11-20 1166

-

FPU加法器的设计与实现2012-07-06 1298

-

基于FPGA高精度浮点运算器的FFT设计与仿真2011-12-23 1056

-

浮点运算与浮点运算器2010-04-15 7455

-

基于FPGA的实时互相关运算器2009-09-19 8593

全部0条评论

快来发表一下你的评论吧 !