采用CPLD来替代微控制器的几种应用介绍

描述

引言

如果告诉便携式电子设计人员有一种低功耗数字器件能使他们利用软件程序来重新配置硬件工作,他们中的十个会有九个认为这是某种微控制器。这是可以理解的。丰富的特性和封装、大量的软件开发工具,以及庞大的应用代码库,无处不在的微控制器几乎能够用在所有便携式应用中。然而,随着低功耗CPLD的出现,设计人员有了新的选择来实现以前由微控制器完成的功能。

本白皮书讨论什么时候适合采用CPLD来替代微控制器,什么时候可以采用CPLD作为微控制器的辅助器件。根据其功能和复杂程度,本白皮书中的例子可以分成三类。第一类是I/O管理,主要针对引脚级应用。第二类是端口管理,重点是器件之间的各种接口。第三类是系统管理,面向使用引脚或者端口来控制系统级功能的应用。

第一次接触可编程逻辑的设计人员会发现CPLD设计在很多方面和传统的微控制器设计类似。下面简单说明CPLD设计流程:

1 利用软件开发工具,采用Verilog或者VHDL等高级语言编写设计。

2 对设计进行仿真,以验证功能是否正确。

3 验证是否满足资源占用和时序通路等物理要求,将设计“适配”到CPLD中。

4 对设计进行仿真,以验证时序是否正确。

5 设计被编程至物理器件中。

一个主要不同是复杂的在电路仿真器功能,以验证微控制器。然而,一旦理解了可编程技术的细微差别后,微控制器设计人员便能够很好地进行CPLD设计。

CPLD替代微控制器的实例

以下部分介绍了CPLD能够有效替代微控制器的某些应用。

I/O管理

当考虑是使用CPLD还是微控制器来进行I/O管理时,所需要的I/O数量和类型是两个关键因素。微控制器的好处是体积小而且价格低,当然还有大量的小型低成本微控制器供设计人员选择。然而,如果某一应用需要大量的通用I/O,那么CPLD在成本上通常可以和微控制器相竞争。小型低成本微控制器一般受限于串口,它最多有几个通用I/O引脚。

设计人员发现,I/O数量较多的微控制器体积也不小,而且价格也昂贵。而另一方面,CPLD趋于有较多的I/O;小外形封装CPLD有50多个I/O是比较常见的。例如,5mm x 5mm封装的Altera? MAX? IIZ EPM240Z CPLD有80个I/O。除了I/O数量优势以外,一般情况下,CPLD要比微控制器更加灵活。除了某些例外,大部分CPLD I/O都能够用于任意目的。

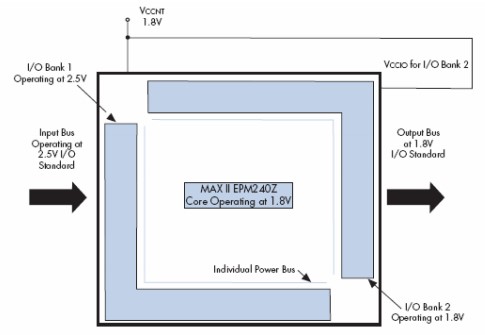

可编程电平转换

很多产品都需要使用电压不同的各种逻辑器件。为支持多电压应用,设计人员要经常连接不同电平的器件。而采用微控制器几乎不可能实现这一切,因为微控制器的I/O资源数量有限,一般采用一个电压源工作。而CPLD有大量的I/O,并分成多个块。相应的为每个I/O块分配一个电压源。因此,开发电平转换器只需要将一个块中一种电压的所有I/O分在一起,将相关的电压参考连接到这些I/O所需的电源上(图1)。使用CPLD不但能够很好地完成电平转换,它更大的优势在于和电平转换相结合的可编程功能。例如,如果某一应用需要LCD显示器,但主处理器并不支持这种显示器,而且电平不同,那么可以采用CPLD来实现主处理器和LCD显示器之间的电平转换时序控制功能。

图1. 使用MAX IIZ CPLD来进行电平转换

脉冲宽度调制

一般而言,设计人员针对某一功能选择一款微控制器,例如脉冲宽度调制(PWM),这些功能也可以采用CPLD来实现。在PWM中,方波的时间周期不变,而信号保持高电平的时间在变化或者受到调制。这样,信号的占空比(tON)是变化的。PWM为数字系统中的模拟电路控制提供了有效的方法。便携式应用中常用的一种方法是利用PWM来调节LED的亮度。

CPLD并没有专用PWM电路,但是实现PWM输出并不难。例如,MAX IIZ CPLD的内部振荡器可以用作频率源,计数器可以用于调制所产生的频率。

模数转换器

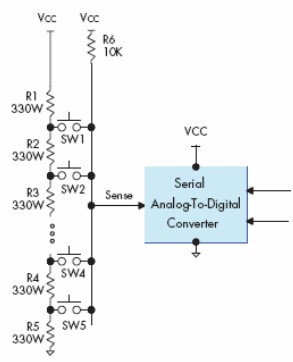

设计人员经常选择微控制器来实现模数转换器(ADC)。然而,在某些情况下,例如键盘解码,可能不需要ADC。

图2所示为一个基本开关阵列和ADC。在VCC和GND之间串联了一组电阻,每个电阻抽头和公共极上连接了一个开关。如果开关接通,电路产生一个和电阻堆中开关位置成比例的电压信号。要在数字系统中使用,模拟信号必须转换为数字值,通常选用含有内置ADC的微控制器来实现这一功能。

图2.模拟键盘阵列

然而,CPLD也是一种选择。加入一个简单的低成本外部电容后,MAX IIZ CPLD可以利用其内部振荡器、施密特触发器I/O以及高密度算法可编程逻辑架构来完成模数转换(1)。

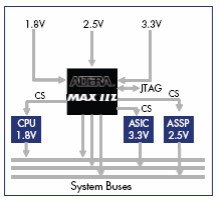

上电排序

MAX IIZ器件针对大量的系统管理功能进行了优化,例如多电压系统上电和系统复位上电排序功能,以及片选信号生成等。这两类应用一般集成在一个非易失、瞬时接通器件中。多电压系统上电排序功能需要采用瞬时接通器件,该器件能马上管理PCB上其他器件的上电顺序。因此,相对于在毫秒量级上电的微控制器,能够在几微秒内上电的CPLD是上电排序功能更好的选择。

图3所示为典型的MAX IIZ器件上电排序应用。随着电路板密度以及电路板电源层数的增加,上电排序变得越来越复杂。MAX IIZ CPLD能够轻松管理系统复杂程度不同的上电排序。多电源供电支持不同的器件,需要采用控制逻辑来管理每一器件的上电顺序。为确保在上电期间不会出现对总线信号的意外驱动,也需要MAX IIZ器件来控制关键总线信号,直至上电完成。JTAG端口监视上电顺序,存储上电时的错误和信息。它还可以用于在调试阶段设置上电排序断点。

图3. 利用CPLD实现上电排序

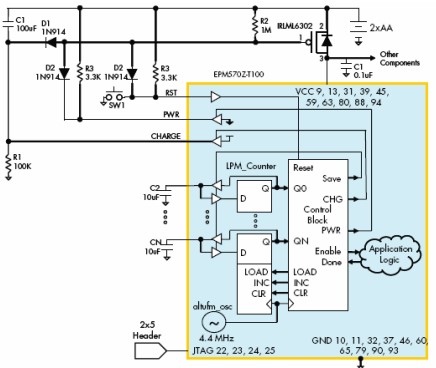

看门狗定时器

很多系统管理应用需要采用定时器。设计人员可能会吃惊地发现CPLD可以用于实现通常由微控制器完成的定时器功能。利用几个分立电容、电阻、二极管和金属氧化物半导体场效应晶体管(MOSFET),设计一个简单但是有效的电阻电容(RC)定时器电路,周期性的对CPLD上电。在图4的实例电路中,设置RC值来建立一个10秒定时器。可以利用三个外部电容(C1、C2和C3)来扩展这一基本定时器,三个电容被用于建立一个简单的非易失二进制计数器。这样,在MAX IIZ EPM240Z CPLD中利用19%的逻辑就可以完全实现从10秒到80秒的间隔周期(2)。

图4. 为MAX IIZ CPLD开发基于定时器的上电电路

CPLD和微控制器结合使用的实例

CPLD并不总是和微控制器相竞争。在以下几个例子中,CPLD是微控制器优异的辅助器件。

GPIO引脚扩展

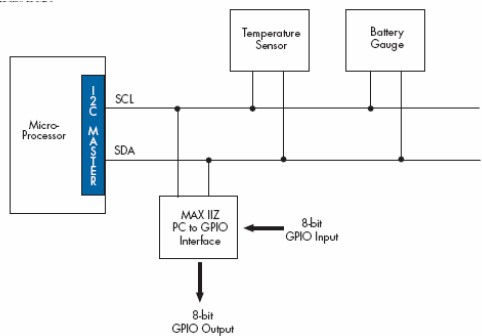

在常见的通用I/O(GPIO)引脚扩展应用中,设计人员把低成本小型微控制器的可编程功能和CPLD的通用IO资源结合起来使用。CPLD构建一组内部寄存器,微控制器通过I2C或者SPI等串口来访问这些寄存器(图5),使微控制器能够使用现有的I/O资源来扩展其I/O总数量。利用扩展I/O,设计人员还可以使用CPLD进行电平转换,从而提高了CPLD的实用性(3)。

图5. GPIO引脚扩展

端口管理

便携式应用设计人员经常需要连接具有不同I/O接口的器件。这一功能被称为桥接,因为采用CPLD来构成不同接口之间的“桥”。这一节介绍三个这样的例子:

串行至串行 - I2C至SPI

串行至并行 – SPI器件(串行)至主处理器(并行)

并行至并行 - 主处理器至CF+

在每一例子中,有几个原因表明为什么CPLD是优于微控制器的选择。一个原因是微控制器不能有效地提供需要的I/O数量。采用微控制器不一定能满足接口需要的性能。此外,在微控制器中实现这些功能要比在CPLD硬件中复杂得多。

串行至串行转换

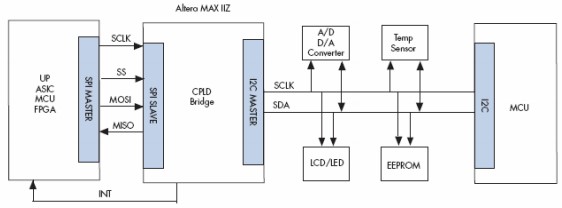

图6所示为采用CPLD来桥接两种不同的串口:I2C和SPI。这一设计可以在MAX IIZ EPM240Z CPLD中实现,使用了大约43%的逻辑和6个I/O引脚(4)。

图6. 利用MAX IIZ CPLD实现I2C至SPI接口

串行至并行转换

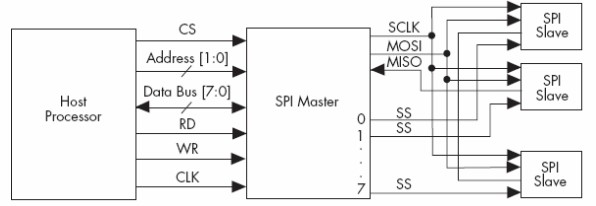

图7所示为主处理器和SPI主机的接口,使用CPLD来实现串并转换接口。这个例子建立一个主处理器总线接口和完整的SPI主机,可以在MAX IIZ EPM240Z CPLD中实现,占用了大约30%的逻辑和25个I/O引脚(5)。

图7. 利用MAX IIZ CPLD实现主处理器至SPI接口

并行至并行转换

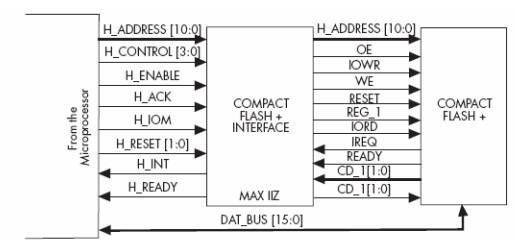

在图8中,CPLD被用于桥接两种不同的并口。这一实例实现了Compact FLASH+器件的主处理器总线接口,在MAX IIZEPM240Z CPLD中实现,使用了大约54%的逻辑,以及45个I/O引脚(6)。

图8. 利用MAX IIZ CPLD实现主处理器至CF+接口

传统上,某些微控制器一直是低功耗电子设计人员的唯一“可编程”逻辑选择。然而,随着低功耗CPLD的推出,设计人员在便携式应用上有了新的选择。本白皮书的多个实例介绍了怎样在便携式应用中使用低功耗CPLD来替代或者扩展以前在微控制器中实现的多种功能。结果,低功耗电子设计人员在便携式应用中拥有了另一套解决问题的工具,在设计创新产品时,能更好地选择最佳器件。

-

微控制器(MCU)架构介绍2016-06-29 3531

-

什么时候可以采用CPLD作为微控制器的辅助器件?2021-04-28 1706

-

如何利用MSP430FR2676TPTR和MAX32660等微控制器来促进可穿戴式设计?2021-07-28 1798

-

LPC2194微控制器替代品有哪些?2023-03-14 625

-

采用可定制微控制器来优化算法的设计2008-09-27 770

-

PLD和数据通路来释放微控制器中CPU资源2011-08-31 2003

-

利用CPLD来替代微控制器的设计2017-09-12 933

-

利用CPLD替代微控制器的6种方法2018-03-22 776

-

关于AVR微控制器采用单周期指令集原因的介绍2018-07-06 4122

-

微控制器接口有哪几种_微控制器特点2020-04-26 3205

-

微控制器到底是什么?微控制器有怎么样的应用2020-06-27 13490

-

什么是微控制器?如何编程微控制器?2020-08-21 12895

-

如何使用NYASM微控制器应用程序2022-06-15 1320

-

汽车微控制器的供电电压2023-07-19 2552

-

微控制器是否能替代PLC2024-06-13 2204

全部0条评论

快来发表一下你的评论吧 !