热载流子注入效应深度解析

描述

在半导体行业追求芯片性能与集成度的道路上,热载流子注入效应(HCI)如同隐形杀手,悄然侵蚀着芯片的可靠性与寿命。随着集成电路尺寸迈入纳米级,这一问题愈发凸显,成为制约芯片技术发展的关键瓶颈。

一、HCI:芯片中的 “能量入侵者”

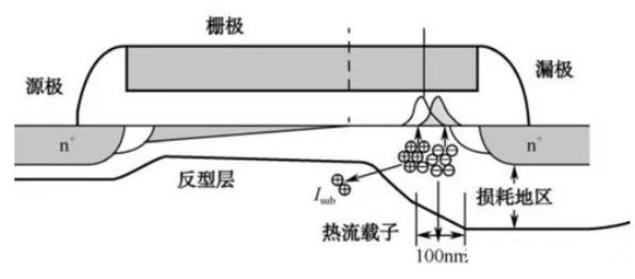

HCI 本质是半导体器件工作时,高能载流子突破材料势垒侵入绝缘层的物理现象。如图 1 所示,当芯片中的电子或空穴在电场加速下获得过高能量,会挣脱束缚撞击栅氧化层——这一晶体管栅极与沟道间的关键绝缘层,最终导致器件性能退化甚至失效。从手机处理器到服务器芯片,HCI 引发的寿命衰减可能造成设备卡顿、功能异常,极端情况下还会引发灾难性故障。

(图1)

二、HCI 的三大 “催生因子”

HCI 的产生并非偶然,而是多重物理机制共同作用的结果,其核心诱因可归纳为三点:

01高电场加速与能量积累

晶体管源极与漏极间的电压形成强电场,载流子(如电子)在电场中加速。当电场强度超过临界值(尤其短沟道器件),载流子动能可能突破晶格振动能级(约 3-4 eV),脱离常规输运路径,成为 “高能失控粒子”。

02碰撞电离与能量传递

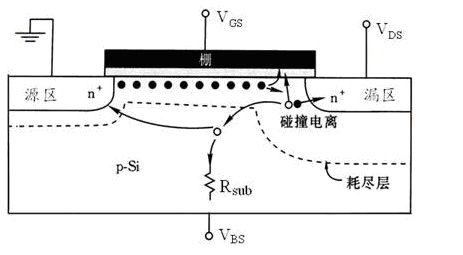

如图 2 所示,高能载流子与晶格原子或其他载流子碰撞时,会引发 “雪崩效应”—— 一次碰撞产生多个二次载流子,进一步加剧能量分布不均。部分载流子借由量子隧穿效应,直接穿透栅氧化层的势垒,完成 “注入” 过程。

03材料界面缺陷的放大作用

栅氧化层与硅衬底的界面并非绝对光滑,微观缺陷(如悬挂键、氧空位)会成为载流子的 “陷阱”。如图 3 所示,高能载流子撞击缺陷点时,会引发局部电荷积累,加速氧化层老化,最终形成永久性损伤路径。

(图2)

[图 2:HCI 碰撞电离过程示意图(标注源区、漏区、耗尽层及碰撞电离发生区域)](GS DS 源区 漏区 n 碰撞电离 p-Si 耗尽层 Rsub ὀ VBS)

(图3)

[图 3:栅氧化层缺陷与载流子陷阱示意图(展示缺陷点对载流子的捕获及电荷积累过程)](载流子如何注入?氧化层缺陷)

三、HCI 对芯片的三重 “致命打击”

HCI 对芯片的危害具有累积性与破坏性,具体体现在三个核心性能指标的退化:

01阈值电压漂移

热载流子注入栅氧化层后,会在界面处形成固定电荷,改变晶体管的阈值电压(开启电压)。这直接导致电路延迟增加、功耗上升 —— 实验数据显示,28nm 工艺芯片在 HCI 影响下,阈值电压偏移可达 50mV 以上,严重影响处理器主频稳定性。

02跨导退化与驱动能力下降

栅氧化层损伤会降低沟道载流子迁移率,表现为晶体管跨导(增益)下降。例如,40nm 工艺测试中,HCI 应力试验后 NMOS 跨导退化率达 15%,直接减慢逻辑门开关速度,严重时可能引发时序错误,导致芯片运算结果偏差。

03寿命指数级衰减

HCI 引发的失效时间(TTF)与电场强度呈指数关系。根据 Black 方程模型,电场强度每降低 10%,器件寿命可延长 10 倍。以 7nm FinFET 工艺为例,当工作电压从 0.7V 升至 0.75V,HCI 失效时间会从 10 年骤降至不足 2 年,凸显电压控制对芯片寿命的关键影响。

四、多维度防御:抵御 HCI 的 “三重屏障”

为应对 HCI 威胁,半导体行业已形成材料、结构、系统多维度的解决方案:

01材料创新:高 K 介质与应变硅

如图 4 所示,采用高介电常数(High-K)材料(如 HfO₂)替代传统 SiO₂,可在相同物理厚度下实现更高电容密度,降低工作电压;同时,应变硅技术通过拉伸或压缩晶格提升载流子迁移率,减少高电场需求。Intel 的 22nm Tri-Gate 技术即通过 3D 结构与材料优化,将 HCI 寿命提升 5 倍。

02结构优化:LDD 与 FinFET

轻掺杂漏极(LDD)通过在漏极附近形成梯度掺杂区,分散电场峰值,避免局部电场过强;而 FinFET 等三维结构通过增强栅极对沟道的控制力,将工作电压降至 0.5V 以下。台积电 5nm 工艺中,环栅(GAA)结构进一步优化电场分布,使 HCI 漏电流降低 40%。

03系统级防护:电压调节与寿命模型

动态电压频率调节(DVFS)可根据芯片负载实时降低电压,减少高电场工况;同时,EDA 工具(如 Synopsys 的 PrimeSim HSPICE)集成 HCI 寿命预测模型,在设计阶段通过仿真识别 HCI 高危节点,指导布线与电路优化,从源头降低 HCI 风险。

(图4)

[图 4:High-K 材料与应变硅结构对比图(左为传统 SiO₂结构,右为 High-K + 应变硅结构,标注栅极、氧化层、衬底等关键部分)](Metal Metal Gate SiGe Gate SiGe Oxide Oxide Silicon Sillicon Substrate Substrate High Speed (HP/SP) High Voltage (TG) and Low Power Logic (LP/ULP))

在芯片向更小制程、更高性能演进的过程中,HCI 的挑战仍将持续。唯有不断突破材料、结构与设计技术,才能有效抵御这一隐形杀手,为芯片的长期稳定运行保驾护航。

季丰电子

季丰电子成立于2008年,是一家聚焦半导体领域,深耕集成电路检测相关的软硬件研发及技术服务的赋能型平台科技公司。公司业务分为四大板块,分别为基础实验室、软硬件开发、测试封装和仪器设备,可为芯片设计、晶圆制造、封装测试、材料装备等半导体产业链和新能源领域公司提供一站式的检测分析解决方案。

季丰电子通过国家级专精特新“小巨人”、国家高新技术企业、上海市“科技小巨人”、上海市企业技术中心、研发机构、公共服务平台等企业资质认定,通过了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ISO45001、ANSI/ESD S20.20等认证。公司员工超1000人,总部位于上海,在浙江、北京、深圳、成都等地设有子公司。

-

MOSFET热载流子效应退化测试解析2026-03-14 4439

-

热载流子注入效应对芯片有什么危害2025-10-21 1568

-

功率放大器驱动:无载流子注入模式下一对多驱动研究的应用探索2025-09-01 778

-

晶圆切割中深度补偿 - 切削热耦合效应对 TTV 均匀性的影响及抑制2025-07-18 657

-

功率放大器在驱动非载流子注入micro-LED上的应用2024-08-28 1868

-

一文解析离子注入的沟道效应2024-02-21 6660

-

8月22日|泰克云上大讲堂—半导体可靠性热载流子效应测试详解2023-08-16 1512

-

功率二极管晶闸管载流子存储效应和开关特性2021-08-12 4848

-

光热电效应的创新研究2020-11-27 5119

-

应力诱导载流子存储效应被提出2020-11-11 3652

-

MOSFET开态热载流子效应可靠性2012-04-23 1016

-

载流子平衡的低压高效有机白光器件2010-04-22 2486

全部0条评论

快来发表一下你的评论吧 !