采用FPGA器件和MPC860架构实现网络应用硬件开发平台的设计

描述

引言

在进行网络应用的硬件设计时,开发者经常会面临将设计思想转化为具体的硬件电路时不得不从绘制电路图、PCB制板,元件焊接等步骤一步步来繁琐而漫长的过程,或者只能通过工具软件进行模拟仿真却无法及时进行实际测试的情况。另外,在计算机网络通信等课程的教学过程中,也存在着学生缺乏有效的实验手段,难以更深入了解网络设备实际的工作机理的问题。为此,我们设计开发了基于FPGA、MPC860架构的网络层应用硬件开发平台,较好地解决了上述问题。

通过开发平台,开发者可以实现数据包的分析、处理及转发,在开发平台之上可实现的主要功能包括以下几部分:

1. 协议识别和分类:根据数据包的协议类型、端口号、目的地址、以及其它特定于协议的信息对数据包进行识别。

2. 拆装和重组:数据包的拆分,处理,以及为转发而重组。

3. 排队和接入控制: 识别出数据包之后,将这些数据包送往相应的队列中以进行下一步处理,如优先处理,流量整形等。同时,可根据某些安全接入策略进行数据*滤,确定是继续转发,还是丢弃。

另外还包括流量整形和流量工程、 QoS(Quality of Service)和CoS(Class of Service)、修正数据包、差错检测等。

搭建这个硬件开发平台后,应用开发者只需关注于核心的硬件逻辑和算法设计,可以及时地验证算法,*估效果,使得设计能尽快转化为实际的电路,将在FPGA开发环境下的功能仿真、时序仿真更进一步至实际电路的测试,极大地方便应用开发。

通过这个硬件平台,学生也可方便地进行计算机网络实验,获取硬件开发经验,提升科研能力。

2 实现原理

1、网络设备的基本功能是实现网络通信业务流的控制和转发, 处于网络边缘的设备需要将来自不同物理链路的各种业务流复用到统一的传输链路上,传统的方法是在网络边缘设备上采用通用的处理器来完成协议栈处理、路由选择以及包头的剥离等功能。随着传输线速率的增加,通用处理器无法维持和传输速率一样的处理速度,于是用专用芯片完成包的处理成为一种趋势。利用专用集成电路(ASIC)来完成特定包的处理工作,性能得到很大的改善,但是ASIC缺乏灵活性给网络设备的升级和功能扩展改进带来很大麻烦。随着传输线速的高速增长和高层协议处理日益增加的复杂度,以及各种网络应用需求的灵活多变,高速和灵活地完成各种协议层上包处理显得更为迫切,而FPGA技术的进步则为这种要求提供了坚实的物理基础。FPGA和MPC860组成的系统架构,则同时具有通用处理器的灵活性和ASIC的高速处理的能力。

从概念上来看,以上所有的应用都是基于如下的处理流程:物理层把来自物理介质的光、电信号转换成一定格式的比特流帧,帧转交到网络处理模块。网络处理模块通过两条通道处理数据帧,快速通道,如数据通道或者转发通道,实现线速处理转发数据帧,这部分是由FPGA完成的;慢通道,如控制通道,完成小部分数据帧(如控制、信令、路由帧)的处理,则可由MPC860完成。

2、在这里需要讨论一下为什么选择FPGA而不是网络处理器(NPU)?

网络应用中可编程解决方案主要有两类:NPU和FPGA,两者都是可编程的。NPU可提供以处理器为中心(即以软件为中心)的可编程特性,而FPGA则提供以硬件为中心的可编程特性。一般而言,以软件为中心的方法的性能低于以硬件为中心的方法。FPGA优于NPU还体现在以下几个方面:

* 深度分组处理:与需要多个NPU进行深层分组处理的NPU解决方案不同,FPGA解决方案只需一块FPGA,这是因为FPGA中的硬件并行处理完全可以同NPU中基于RISC的处理方法相媲美。多个NPU不仅为硬件和软件分区带来新挑战并增加了软件的复杂度,而且还增大了系统延迟和功耗。

* 软件可升级性:NPU不具备代码复用,因为NPU的软件大多是不可移植的,即这些软件是专有的汇编代码或因定制程度过高而丧失移植性的C代码。相反, FPGA则具有较强的软件升级功能。

* 硬件可升级性:硬件的可升级特性确保了较长的产品寿命,因而成为可编程解决方案的一个关键特性。NPU只在处理器中提供可编程特性,其类似ASIC的定制硬件并不能直接进行编程,因此它在硬件升级上的劣势与ASIC非常相似。FPGA顾名思义就是现场可编程,是对数据进行高速并行处理的理想器件,具有极强的灵活性和扩展性,可轻松升级,以很好地满足需求变化。

3、MPC860是基于PowerPC结构的通信控制器。它不仅是集成的微处理器,而且将很多外设的功能也集成在一起。MPC860具有功能很强的存储控制器,可以支持各种存储器,包括各种新型的DRAM和Flash,并可以实现与存储器的无缝接口。使用嵌入式操作系统VxWorks和开发环境Tornado进行开发也非常方便。

之所以使用MPC860,是为了系统的灵活性考虑。利用它可以完成一些较复杂的算法功能,和FPGA相配合,充分发挥各自的长处,以适应不同的网络应用。

4、在开发平台的设计中,考虑到了系统的可扩展性和灵活性,尽管FPGA内部已有丰富的存储器资源,我们仍特别为FPGA配置了片外的SRAM,并在SRAM的容量上作了较大的冗余,可完成一般情况下的数据包存贮。同时考虑到FPGA处理速度的因素,SRAM的数据总线的宽度设计为64位,这样,由FPGA进行SRAM读取操作时不会产生阻塞现象。

3 具体实现

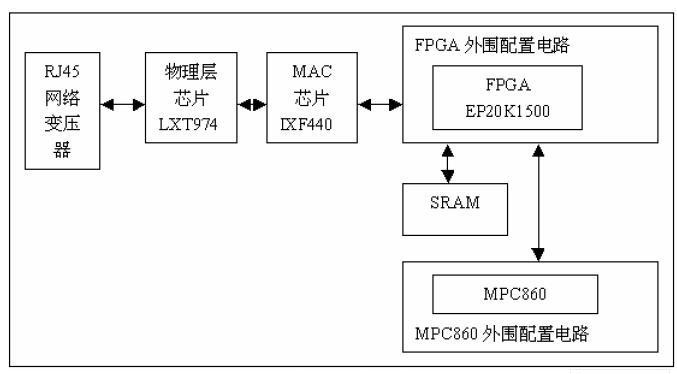

开发平台由以太网控制器(MAC),FPGA,SRAM,MPC860,物理层芯片,网络变压器等元器件组成,系统组成如图1所示。

图1 系统组成框图

本开发平台的硬件功能完全在一片FPGA中完成。从功能需求和可持续开发的角度出发,选择了ALTERA公司的APEX20KE1500。之所以选择APEX20KE1500,主要是因为此型号的规模大,逻辑门达到150万门,51840个逻辑单元(LEs)特别是其内部可定义的存储单元大,达到了442368位,可灵活地实现为RAM、ROM、CAM,可以满足缓存数据包的需求,又有利于设计复杂的存储、查找、比对等功能。

MAC选取了Intel的IXF440,它是一个8口10/100Mbits以太网控制器,用以接收和发送以太包。LXT974是4端口快速以太网物理层芯片,它支持IEEE802.3协议,支持10Mbps 和100Mbps应用,提供四个独立的MII接口。每个端口可支持双绞线接口和连接10/100BASE-TX 或 100BASE-FX 的PECL。在本开发平台上,使用了两片百兆PHY芯片LXT974,这样共可提供8个网络接入端口。

4 应用实例

利用此开发平台可以实现如8口以太网交换机,8口以太网路由器,网络防火墙等,在本文中将以总装备部课题DDoS的防御为例予以介绍。

随着网络技术的发展和Internet的普及,网络安全问题也日益突出。高速广泛连接的网络给大家带来了方便,也为分布式拒绝服务(DDoS)攻击创造了极为有利的条件。DDoS攻击已经成为网络上广泛传播的问题。我们在本开发平台的基础上,通过寻求一种高效、对各种DDoS攻击都行之有效的算法,采用软硬件相结合的方法,实现了实时检测、防御DDoS攻击的功能。

利用该开发平台,我们用MPC860实现非参数的CUSUM算法,在嵌入式实时操作系统VxWorks及其开发环境Tornado下对MPC860进行开发;用FPGA实现硬件功能,采用AHDL语言对FPGA进行开发,在MAX+PLUS II和Quartus II环境下对FPGA进行调试和仿真;

根据CUSUM算法计算出判决门限,检测出DDoS攻击,由硬件对攻击包进行实时处理,采取有效措施维护网络的正常运行,消除攻击的危害。

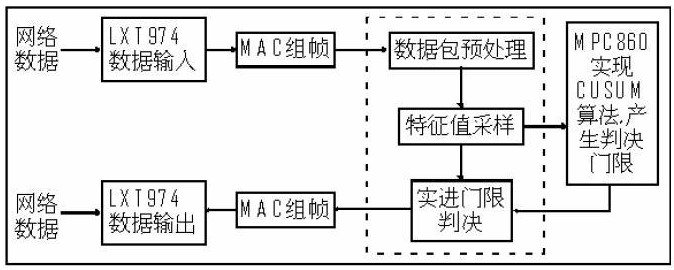

完整的DDoS防御系统置于网段入口,它包括了从数据接收、数据预处理、数据采集、数据运算和处理、实时判决到最终的数据输出这一整套步骤。数据流程见图2。

由FPGA完成了数据包的预处理功能,包括数据包类型的读取;源IP地址,目的IP地址的读取、比较;数据包协议类型的提取;IP数据包头的奇偶校验;TCP/UDP数据包端口提取,检测等。特征值的数据采样也由FPGA完成。MPC860根据FPGA提取的特征值进行计算产生判决门限和过滤规则,由FPGA根据MPC860得出的过滤规则实现实时的门限判决。

由于有了本开发平台,研究小组集中精力于HDL语言和检测算法,在较短的时间内完成了建模和仿真,并进行了实际的电路运行测试,根据测试中存在的问题及时调整了硬件逻辑和算法,最终比原计划提前半年完成了该课题的研究。

另外,该开发平台在网络课程教学中也得到了有效的应用。在讲授交换机原理,路由协议、排队算法等课程时,让学生对一些简单的算法进行硬件仿真设计,并下载至开发平台上进行实验,加深了学生对所学知识的理解,掌握了初步的硬件设计能力和设计思想,为学生的科研能力的提高打下了较好的基础。

-

如何在MPC860板的SCC2通道上实现HDLC的驱动程序?2021-06-03 1055

-

MPC860控制FPGA配置2017-11-23 3121

-

TMS320C6000扩展总线与MPC860的HPI接口设计2011-08-10 2686

-

MPC860寄存器配置2011-06-08 1199

-

基于MPC860与ST16C654的串行通信设计2010-07-21 1813

-

基于MPC860的SIMADYN D通信板的设计2010-07-14 754

-

基于MPC860和VxWorks的硬件防火墙设计及实现2010-07-06 943

-

基于FPGA的网络应用硬件开发平台的实现2010-03-02 1504

-

基于MPC860的HDLC通道驱动程序的设计与实现2010-01-14 1282

-

MPC860 Power QUICC及其在嵌入式系统中的应用2009-10-01 1305

-

VxWorks下MPC860的中断处理机制及其应用2009-06-10 596

-

MPC860 的中断处理技术研究2009-05-18 811

全部0条评论

快来发表一下你的评论吧 !