采用Stratix系列FPGA器件实现可访问三口RAM操作的SDRAM控制器设计

描述

引言

SDRAM 具有存储容量大、速度快、成本低的特点,因此广泛应用于雷达信号处理等需 要海量高速存储的场合,但是SDRAM 的操作相对复杂,需要有专门的控制器配合处理器 工作完成数据的存取操作。随着FPGA 技术的快速发展及其应用的普及,用FPGA 实现 SDRAM 控制器是目前最流行的技术手段。虽然现在FPGA 的生产商提供了一些通用的 SDRAM 控制器,但是在雷达信号处理等一些专用领域内这些通用的SDRAM 控制器难以满 足需要,需要开发适合的专用的SDRAM 控制器。

本文以一个典型的雷达信号存储与预处理系统为应用背景,用 Altera 公司的Stratix 系 列FPGA 实现了一个三端口非透明型的SDRAM 控制器,该控制器内部具有灵活准确的优 先级仲裁功能,在保证多个端口平均分配SDRAM 带宽的同时不影响数据传输的带宽,采 用乒乓的DMA 传输机制大大提高了数据传输的带宽和效率。

2 SDRAM 的特点及其基本操作

SDRAM 是在现有的标准动态存储器中加入同步控制逻辑(一个状态机),利用一个单一的系统时钟同步所有的地址数据和控制信号,它具有如下一些特点:

结构特点:存储容量大,受输出管脚数量限制,其存储单元设计成矩阵形存储结构,因此地址分为行地址和列地址,首先给出行地址选通一行(或一页),然后给出列地址选中要访问的地址单元;

采用电容存储信息,因此需要定时充电(刷新);

同步访问:所有信号都在时钟上升沿采样有效才认为有效;

基于猝发(Burst)方式访问:在发出一次读写命令之后,SDRAM 自动访问长度为猝发 长度的地址空间,非Burst 访问的效率很低;

速度快:只要 SDRAM 控制器合理设计时序,可以实现单周期访问一个地址单元。 SDRAM 的基本操作包括:初始化、激活、预充电、刷新等等。

初始化:SDRAM 上电之后必须按照确定的程式进行初始化之后才能正常工作,最主要 的操作是模式寄存器的设置;

激活:选中所要访问的行列地址单元;

刷新:SDRAM 存储单元载体为容量很小的电容并存在漏电流。需要定时读取回填各 个单元才能保证数据不丢。在片内有自动刷新控制器,记录了刷新行地址,每执行一次自 动刷新命令,刷新一行;

预充电:每次读写操作是通过传感放大器对存储单元电容的充放电过程,在读操作时对 选中整行单元的原始数据可能产生破坏。这就需要在每次读取操作后立即对该行原内容 与阈值比较再回写,并且对传感放大器参考阈值电压复位准备下一次做读写操作。所以 总是在执行换行读写或刷新之前执行预充电操作。

3 SDRAM 控制器的基本功能

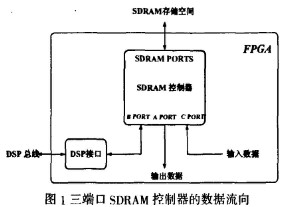

三端口非透明型 SDRAM 控制器是指控制器面向用户端有三个端口而不是通常情况下 的一个端口,三个端口的功能完全一致,依靠仲裁控制切换端口与SDRAM 之间交换数据, 数据交换采用DMA 的方式,流经SDRAM 的数据流如图1 所示。数据由C 端口输入,A 端 口输出,B 端口作为与DSP 的数传通道。

图 1 三端口SDRAM 控制器的数据流向

这里透明型是指外部设备访问 SDRAM 时,只需简单读写而不需要进行其它复杂的管 理操作,外部设备可以通过SDRAM 控制器将SDRAM 空间视为一个普通的同步三口RAM 操作。但是这种结构不能灵活的实现地址跳变的访问,随机访问的带宽很低,三个端口再次 平均分配SDRAM 的带宽会进一步降低吞吐性能。所以,系统设计中采用了非透明型的设 计,非透明的意思是指:外部设备为了访问SDRAM 的数据,不但要进行数据的读写操作,而且需要进行寄存器设置、控制信号调整等其它操作。非透明型设计的灵活性较差,但是可 以根据具体的使用环境对功能进行简化,并且将一部分控制操作转交给软件完成,所以实现 相对比较简单,而且更加稳定可靠。

4 SDRAM 控制器的基本结构及工作原理

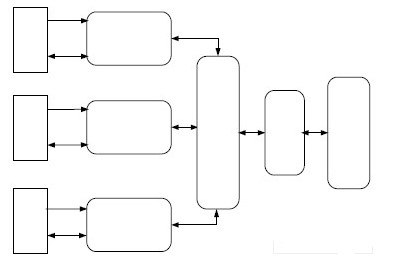

三端口非透明型 SDRAM 控制器的结构框图如图2 所示。A、B、C 三个端口的内部结 构完全相同,都包含一个双口RAM(作为数据乒乓缓存),一个DMA 控制器。外部设备可以 通过端口读写DPRAM 中的数据,也可以写DMA 控制寄存器。DMA 控制器的功能是根据 DMA 控制寄存器内的设置在DPRAM 和SDRAM 之间交换数据,当DSP 或者其它外部设备 设置了寄存器后,DMA 控制器向仲裁和数据分配器发出访问SDRAM 的请求,然后开始一 次DMA 操作。仲裁和数据分配器的功能是决定当前哪一个端口具有访问SDRAM 的权利。 SDRAM 时序控制器则负责产生操作SDRAM 必须的命令码,并且传递数据。

图 2 三端口非透明型SDRAM 控制器的结构

外部设备与 SDRAM 之间通过一个双口RAM(DPRAM)进行隔离。外部设备可以直 接读写DPRAM 的右侧端口,也可以通过设置DMA 寄存器来启动DPRAM 左侧端口与 SDRAM 之间的DMA 操作。SDRAM 控制器的基本工作原理如下:

(1)写操作:当外部设备需要向SDRAM 写数据时,首先将数据存入DPRAM,然后 启动一个从DPRAM 到SDRAM 的DMA。

(2)读操作:当外部设备需要读SDRAM 时,首先启动一个从SDRAM 到DPRAM 的 DMA,等DMA 结束以后再从DPRAM 读取数据。

(3)基于扇区的长度和地址控制:为了简化DMA 控制器以及其它的控制逻辑,DPRAM 和SDRAM 之间的DMA 传输不是任意长度任意地址的DMA 传输,而是以扇区为基本数传 单位。这里定义一个扇区的长度为SDRAM 中的一行(或者叫一个page)。每个DPRAM 则 顺序划分为2 个扇区。每次DMA 操作完成一个完整扇区数据的搬移。

(4)仲裁控制:当两个或是三个DMA 控制器同时请求访问SDRAM 时,由仲裁控制 器根据优先级规则进行控制。设计中采用了轮换优先级的方式,即:刚刚完成了一次DMA 操作的端口具有比较低的优先级,当前具有最高优先级的端口有权占用SDRAM 直至本次 DMA 结束,这样,就可以三个端口分时占用DMA 通道,保证三个端口之间平均的分配 SDRAM 的带宽。

5 仲裁器的设计

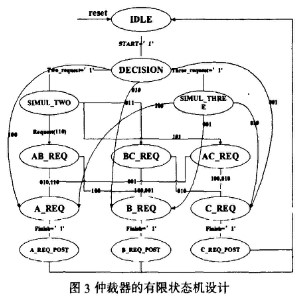

仲裁及数据分配器的设计的核心问题是轮换优先级的设计。必须保证三个端口分时占用 DMA 通道,保证平均分配带宽。采用有限状态机作为仲裁器的控制逻辑,这样既可以保证 优先级设计的稳定性,又可以确保仲裁器判决的实时性,有限状态机的设计如图3 所示。

图 3 仲裁器的有限状态机设计

设计中最复杂的情况是:一个通道访问SDRAM 的同时(如A 通道),另外两个通道同时 申请下一次访问SDRAM(如B、C 通道),这样就需要有一个标志位,用它来记录上一次访 问过SDRAM 的通道,在下一次仲裁时把它排除在外,直到再下一次仲裁时才予以考虑。

每次DMA 结束后,都自动返回到IDLE 的状态,通过request 标志位,上次DMA 通道记录 位来判断此次访问SDRAM 的通道。具体设计如下:

设初始状态下,默认A 端口具有最高优先级,然后A、B、C 三个端口具有轮换优先级;

设置一个标志位 old_request,表示上一次响应的端口,“100”A 端口响应,“010”B 端 口响应,“001”C 端口响应;

利用一个标志位 request[2:0]作为状态翻转的标志;

利用标志位 two_request,three_request 作为进入两个或三个端口同时请求状态的标志, two_request = ABC + ABC + ABC,three_request = ABC。

6 结论

本文利用 FPGA 设计并实现了一个相对专用的三端口非透明型SDRAM 控制器。本文 作者创新点在于:通过设计一个带轮换优先级设置的多端口SDRAM 控制器,采用乒乓的 DMA 传输机制,将复杂的SDRAM 访问虚拟成一个简单的三口RAM 的访问,具有访问简 单、控制灵活、传输带宽大等特点。已在某雷达信号存储与预处理系统中成功应用。

-

fpga双口ram的使用2024-03-15 2395

-

实时视频SDRAM控制器的FPGA设计与实现.zip2022-12-30 536

-

基于FPGA的DDR3SDRAM控制器设计及实现简介2021-07-30 976

-

如何使用Verilog实现基于FPGA的SDRAM控制器?2021-04-15 1853

-

如何使用FPGA设计SDRAM控制器2020-12-18 1043

-

基于FPGA器件实现对DDR SDRAM的控制2019-08-14 4678

-

SDRAM与双口RAM数据转移接口控制电路2019-06-10 2202

-

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文2018-12-25 1739

-

SDRAM控制器的设计2017-11-28 1495

-

采用FPGA与IP来实现DDR RAM控制和验证的方法2017-11-24 4819

-

基于FPGA的三端口非透明型SDRAM控制器2010-03-03 819

-

SDRAM控制器的设备与VHDL实现2009-06-20 1074

全部0条评论

快来发表一下你的评论吧 !