基于FPGA技术实现软件无线电的设计

描述

软件无线电技术给正在开发无线电架构的工程师带来力量。编程中频(IF)带宽、调制、编码模式和其他无线电功能的能力广泛引起注意的。除了提供所有这些灵活性外,软件无线电必须改善灵敏度,动态范围和邻信道抑制性能。软件无线电仍然是无线电,但它必须被比正在替代的通常无线电执行的更好。

现场可编程阵列(FPGA)技术先进之处在于紧凑的占位空间能够高速处理,同时也保持软件无线电技术的灵活性和可编程性。FPGA在高速、计算密集、可重新配置应用(FFT、FIR和其他乘法—累加运算)中是受欢迎的。从FPGA和板供应商可得到可重新配置核,在FPGA中能够实现调制器,解调器和CODEC功能。系统设计人员期待着带集成FPGA的前端采集/变换器产品来卸载基带处理和降低数据传输率。

尽管应用开发工具有巨大改进,但FPGA设计应考虑硬件开发,这需要不同于软件开发的技术。

FPGA设计意味着重新设计商用现成的前端数据采集/变换器模块上的核,这不是简单的软件开发执行。在任务计划阶段需要考虑降低延误。

FPGA在多任务软件无线电应用(如电子战、雷达、通信、RF测试)中是重要的。

FPGA或DSP

FPGA已从灵活的逻辑设计平台发展到信号处理引擎。现在FPGA是软件无线电的主要元件,这是由于FPGAR的灵活性和实时处理能力所致。系统设计人员正在把更多的信号处理集成在一起的灵活性推动设计人员用FPGA替代传统的DSP。FPGA 因有效的适合于高速并行乘法累加函数。现代FPGA可执行18×18乘法运算,速度超过200MHz。这使得FPGA成为FET、FIR,数字下复频器(DDC)、数字上变频器(DUC)、相关器和脉冲压缩(用于雷达处理)运算的理想平台。然而,这不意味着所有DSP功能可以在FPGA中实现。用FPGA实现浮点运算是困难的,这是由于器件需要大量的有效区域。另外,包括短阵反演(或除法)的处理更适合DSP/GPP平台。因此,FPGA和DSP将共存很长时间,一个灵活的平台将包括二者的混合。

FPGA设计

FPGA设计是特有的硬件设计,而不是简单DSP编码执行。EDA(电子设计自动化)工具的发展能保证更好和更精确的设计。传真软件在市场有售。FPGA供应商(Xilinx和Altera公司是两个最大的)也用仪器装备来促进工具开发。从而使FPGA设计变容易。

FPGA IP核

在普通的FPGA 中,已经增加了来自FPGA供应商和其他第3号核开发商的IP核。这些核提供各种DSP功能。然而,这需要集成到实际的硬件中。把这些核集成到商用现成模块中需要时间和硬件设计经验。ICS公司提供的FPGA核是完全测试和集成有高性能数据采集和变换器的商用现成模块。这些模块提供智能前端产品,因此,降低了系统设计和集成风险。

宽带数字下变频器

宽带数字下变频器(DDC)是任何软件无线电基系统的主要元件。DDC已基本上改变了通常的无线电设计。DDC能够简化RF前端设计,这包括LO和混频器设计,这是在数字域执行下变频过程。数字混频器后面的数字滤波器比传统模拟滤波器能提供更佳整形滤波。这些滤波器通常是分样,所以降低了输出数据率。流行的专用DDC提供可调频率。然而,它们通常应用目标是窄带应用。

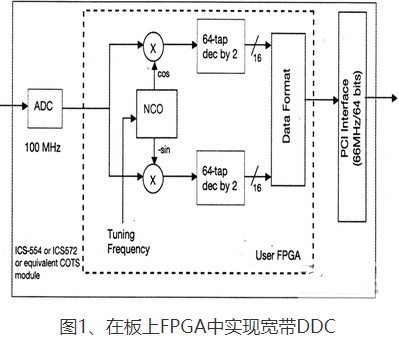

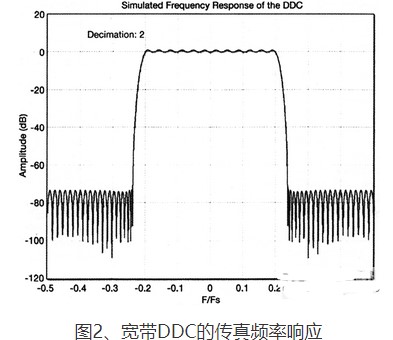

随着较宽带宽需求的增加,系统设计人员正在力图设计带宽高达40MHz的宽带系统。这包括雷达、GPS、遥测装置、宽带通信等。对于较宽带宽,在FPGA中实现DDC需要在FPGA之后有ADC。典型的分样DDC实现示于图1。此2分样DDC提供-0.2*FS~0.2*FS的最大平顶带宽(在100MHz ADC取样)。用100MHz取样时钟,这说明40MHz平顶带宽和每个信道200MBps数据率。DDC提供阻带抑制超过70dB(图2),为较宽带宽配置的滤波器可提供2X或4X过取样因数。

滤波器的可编程性是软件无线电实现的一个主要方面。ICS设计人员已实现平顶带宽-0.1*FS~+0.1*Fs的4分样DDC。对于100MHz取样率,可提供20MHz平顶带宽。

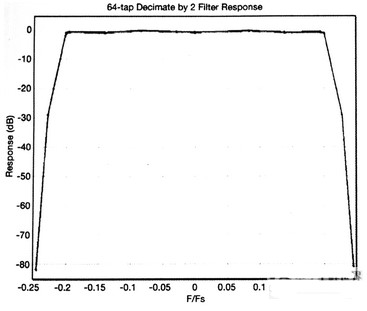

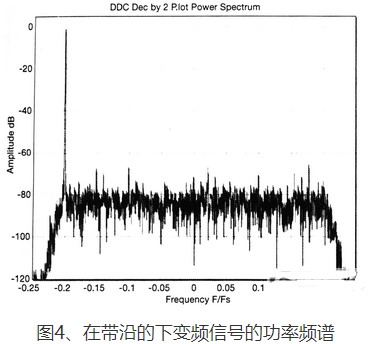

图3示出在ICS-554中实现的2分样宽带DDC的频率特性。这是实际测量的数据,可与传真电线对照。图4示出在带沿的下变频信号的频谱。

图3、用ICS-554实现的64抽头2分样DDC的系统内系统性能

1百万门的Virt ex II FPGA支持单个2分样64抽头DDC,因此,FPGA可容易地集成到ICS-554B中。

在集成这些高速DDC时,必须保证数据传输不被中断。对于多信道系统,这意味着需要用专门数据总线。行业标准PMC模块具有通过旁路PCI总线经Pn4PMC用户I/O连接器直接传输高速数据。

对于发送器,数字下变频器用数字上变频器(DUC)替代。DUC采用数字内插滤波器并具有同样的优点 。

实时频谱监控和监测

实时频谱监视和监测是方便采用FPGA和软件无线电技术的另一问题。不同于明显用于信号信息(SIGINT)和EW方案,此功能已泛用于RF测试和频谱分析应用。

带高速ADC和大用户FPGA的商用现成模块(如ICS-554)对于实时频监视和监测系统是一个理想的平台。大用户FPGA对于实现实时功率频谱估计值(FFT),幅度计算和频谱平均是理想的。限定范围和检测之后,可以用板上窄带数字调谐器做为降落接收器来调谐所关心的信道。集成IP核以保证这样复杂的系统可用于行业标准单PMC卡。

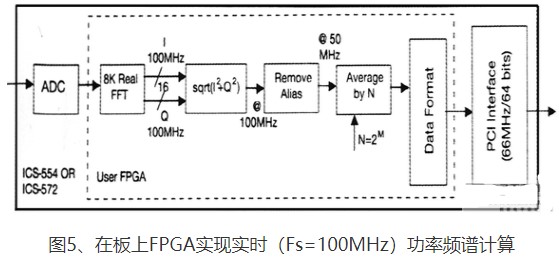

ICS已把8K实时FET引擎和功率检测及频谱平均集成在一起(图5)。

Virtex II FPGA很容易支持需功率检测和可编程平均的8K FET引擎。

用于改进C/I 的智能天线和相控阵雷达射束形成器

虽具有大量元件的相控阵雷达的C/I改进的智能天线正在成为下一代商用无线系统的共同关心的问题。这两方面的应用具有共同的原理。这些系统可以处理大量带宽并能来回传送数据。建造一个能在多DDC间同步和多模块间高速数据传输均同步系统。

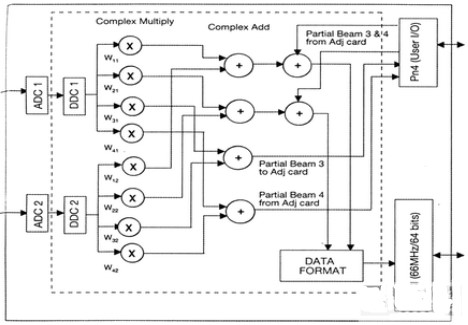

一个在40和20MHz带宽实现的2×2射束形成器示于图6。用两个ICS-554采集4路模拟信道。对于20MHz带宽,每个ICS-554产生4个单独的射束,其中两个射束送到其他数据采集板卡。每个板卡把内部产生的2个单独射束与以其他ICS-554接收的2个单独射束组合产生2个完整射束。对于低电压晶体管—晶体管逻辑(LVTTL)门400MBps。每个方向板之间的数据传输是200MBps。希望用低电压差分传输(LVDS)接口能显着地增加数据传输,增加带宽。

图6、用安装在单PCI载波器上的2个ICS-554C模块实现2×2射束形成器。

在Pn4PMC用户I/O上高速数据传输

在某些应用中,对于系统集成人员从商用现成PMC模块用用户定义的协议传输高速数据是更方便的,这使系统总线对于其他功能是空闲的。这样一种协议通常用在前面板数据口(FPDF)协议,这是一种ANSI/VITA(美国国家标准委员会/VME bus行业贸易协会)标准。为了确保高速数据传输,ICS在用户FPGA中已实现发送和接收核来支持PMC模块的Pn4用户I/0连接器的FPDA前面板数据口。因此,系统集成人员经FPDA在ICS PMC模块上有无缝传输数据的方法。其他标准和专利数据传输协议也能在用户FPGA中实现。

在Pn4用户 I/O连接器上用LVDS信号传输可在PMC模块间或从PMC模块到母板实现高速数据传输。

结语

FPGA 正在成为无线电设计的主要部分。要增加更多功能到FPGA。然而,FPGA和传统DSP及GPP正在共存,而灵活的平台将包括二者的混合。对待FPGA,设计像执行硬件设计,而不仅是一个软件问题,在任务计划阶段是需要考虑的因素。

-

软件无线电的主要原理及技术2023-09-22 1140

-

如何实现软件无线电的设计?2021-04-08 1757

-

采用射频天线实现软件无线电技术2019-07-11 2445

-

基于FPGA的软件定义无线电参考设计2019-07-04 1947

-

中频软件无线电的实现方案和基于FPGA的通用硬件平台2019-05-28 2008

-

通过利用FPGA技术实现软件无线电硬件平台设计2019-05-05 3938

-

软件无线电的原理及结构2018-10-09 3789

-

软件无线电、无线电的技术概述及应用2018-08-21 4371

-

真正实现软件定义无线电设计2015-08-14 3935

-

认知无线电技术实现和挑战2010-04-24 3051

-

软件无线电,软件无线电是什么意思2010-04-09 2214

-

实现软件定义无线电和认知无线电的自适应特性2010-03-05 559

-

FPGA在软件无线电接收机实现数字定时恢复2009-07-27 555

-

FPGA-CPLD在软件无线电中的工程应用2009-04-18 7015

全部0条评论

快来发表一下你的评论吧 !