采用FPGA芯片实现UART功能模块的设计

描述

引言

通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。一般UART由专用芯片如8250,16450来实现,但专用芯片引脚都较多,内含许多辅助功能,在实际使用时往往只需要用到UART的基本功能,使用专用芯片会造成资源浪费和成本提高。

一般而言UART和外界通信只需要两条信号线RXD和TXD,其中RXD是UART的接收端,TXD是UART的发送端,接收与发送是全双工形式。由于可编程逻辑器件技术的快速发展,FPGA的功能日益强大,其开发周期短、可重复编程的优点也越来越明显,在FPGA芯片上集成UART功能模块并和其他模块组合可以很方便地实现一个能与其他设备进行串行通信的片上系统。

1 UART功能设计

1.1 UART的工作原理

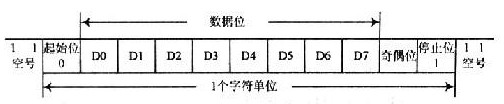

异步通信时,UART发送/接收数据的传输格式如图1所示,一个字符单位由开始位、数据位、停止位组成。

异步通信的一帧传输经历以下步骤:

(1)无传输。发送方连续发送信号,处于信息“1”状态。

(2)起始传输。发送方在任何时刻将传号变成空号,即“1”跳变到“O”,并持续1位时间表明发送方开始传输数据。而同时,接收方收到空号后,开始与发送方同步,并期望收到随后的数据。

(3)奇偶传输。数据传输之后是可供选择的奇偶位发送或接收。

(4)停止传输。最后是发送或接收的停止位,其状态恒为“1”。

发送或接收一个完整的字节信息,首先是一个作为起始位的逻辑“0”位,接着是8个数据位,然后是停止位逻辑“1”位,数据线空闲时为高或“1”状态。起始位和停止位的作用是使接收器能把局部时钟与每个新开始接收的字符再同步。异步通信没有可参照的时钟信号,发送器可以随时发送数据,任何时刻串行数据到来时,接收器必须准确地发现起始位下降沿的出现时间,从而正确采样数据。

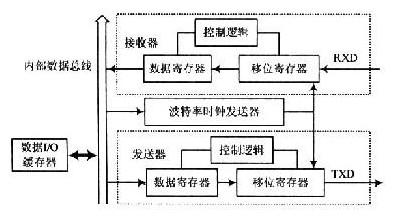

设计时可参考由专用芯片实现的UART的功能并进行一定精简,如可以用FPGA的片内RAM替代UART的FIFO,不用单独在UART模块中实现。设计的基本原则是保留最主要的功能,基于FPGA的UART系统由波特率时钟发生器、接收器和发送器3个子模块组成,如图2所示。

1.2 接收器设计

比较而言,UART发送器的设计相对容易,只要每隔一个发送周期并按照数据帧格式输出数据即可,本文将对接收器的设计和实现做详细说明,发送器的设计方法基本相同。

接收器的工作过程如下,在接收数据寄存器被读出一帧数据或系统开始工作以后,接收进程被启动。接收进程启动之后,检测起始位,检测到有效起始位后,以约定波特率的时钟开始接收数据,根据数据位数的约定,计数器统计接收位数。一帧数据接收完毕之后,如果使用了奇偶校验,则检测校验位,如无误则接收停止位。停止位接收完毕后,将接收数据转存到数据寄存器中。

为确保接收器可靠工作,在接收端开始接收数据位之前,处于搜索状态,这时接收端以16倍波特率的速率读取线路状态,检测线路上出现低电平的时刻。因为异步传输的特点是以起始位为基准同步的。然而,通信线上的噪音也极有可能使传号“1”跳变到空号“0”。所以接收器以16倍的波特率对这种跳变进行检测,直至在连续8个接收时钟以后采样值仍然是低电平,才认为是一个真正的起始位,而不是噪音引起的,其中若有一次采样得到的为高电平则认为起始信号无效,返回初始状态重新等待起始信号的到来。找到起始位以后,就开始接收数据,最可靠的接收应该是接收时钟的出现时刻正好对着数据位的中央。由于在起始位检测时,已使时钟对准了位中央,用16倍波特率的时钟作为接收时钟,就是为了确保在位宽的中心时间对接收的位序列进行可靠采样,当采样计数器计数结束后所有数据位都已经输入完成。最后对停止位的高电平进行检测,若正确检测到高电平,说明本帧的各位正确接收完毕,将数据转存到数据寄存器中,否则出错。

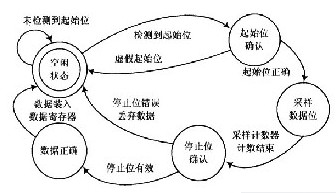

采用有限状态机模型可以更清晰明确地描述接收器的功能,便于代码实现。接收器的状态转换图如图3所示,为突出主要过程,图中省略了奇偶校验的情况。接收器状态机由5个工作状态组成,分别是空闲状态、起始位确认、采样数据位、停止位确认和数据正确,触发状态转换的事件和在各个状态执行的动作见图中的文字说明。

在状态机模型的基础上,使用VHDL来描述接收器功能,其主要代码如下:

实现用16倍波特率时钟确定起始位的具体方法是设计两个输入数据位寄存器rxd1和rxd2,使用语句“rxd1<=rxd;rxd2<=rxd1;”接收数据并进行判断。当检测到rxdl=O并且rxd2=1时可以确定下降沿发生,连续7个时钟rxd2=0即确定检测到起始位,之后为了确保在数据位中央接收数据,同样用16倍波特率时钟对数据位进行采样。接收数据的方法是设计一个寄存器rxd_buf(7 downto 0),用语句“rxd_buf(7)<=rxd2;rxd_buf(6 DOWNTO 0)<=rxd_buf(7 DOWNTO 1);”实现移位寄存器右移操作,执行8次后接收到一个完整数据。

1.3 波特率发生器设计

波特率发生器实质是设计一个分频器,用于产生和RS 232通信同步的时钟。在系统中用一个计数器来完成这个功能,分频系数N决定了波特率的数值。该计数器一般工作在一个频率较高的系统时钟下,当计数到N/2时将输出置为高电平,再计数到N/2的数值后将输出置为低电平,如此反复即可得到占空比50%的波特率时钟,具体的波特率依赖于所使用的系统时钟频率和N的大小。如系统时钟频率是40 MHz,要求波特率是9 600,则16倍波特率时钟的周期约等于260个系统时钟周期,则计数器取260/2=130时,当计数溢出时输出电平取反就可以得到16倍约定波特率的时钟。

使用VHDL来描述波特率发生器的完整代码如下:

2 数据传输测试

随着逻辑设计复杂性的不断增加,仅依赖于软件方式的仿真测试来了解系统的硬件功能有很多的局限性,应用QuartusⅡ集成开发环境中提供的SignalTapⅡ嵌入式逻辑分析仪,可以将测试信息随设计文件下载于目标芯片中,用以捕获目标芯片内部系统信号节点处的信息或总线上的数据流,而又不影响原硬件系统的正常工作。测试信息通过器件的JTAG端口传出,并送入计算机进行显示和分析,这是一种高效的硬件测试手段,并很好地结合了传统的系统测试方法。

本设计在Altera Cyclone系列的EPlC6Q240C8芯片上进行了验证,使用QuarltusⅡ软件将编译好的.pof格式文件以AS模式下载到配置芯片EPCS1中。在计算机端运行串口调试助手软件,将数据从计算机送出,并利用FPGA上的UART模块进行接收,将发送数据与SignalTapⅡ获取的波形进行对比,经多次测试表明收发数据完全相同。

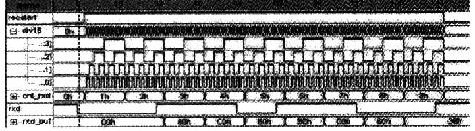

以其中一次的测试为例进行说明,从PC上输入ASCII码的“6”,设定波特率发生器时钟作为SignalTapⅡ的采样时钟,采样波形如图4所示,其中“recstart”表示开始接收数据帧标志;“divl6”表示16倍波特率时钟;“cnt_rxd”表示数据位采样计数器,一次完整的采样计数从Oh~9h共10次采样(1个起始位,8个数据位,1个停止位);“rxd”表示串口的接收端;“rxd_buf”表示移位寄存器,当数据停止位确认后,移位寄存器输出收到的数据“36h”,表明了该UART工作稳定可靠。

应特别注意的是当利用SignalTapⅡ进行测试工作结束后,在生成最终产品前,应将SignalTapⅡ从芯片中除去,以免占用额外的资源,然后再重新编译下载。全程编译后报告消耗逻辑单元142个,只占芯片总资源的2%,没有占用芯片的存储单元和PLL单元,对于一个中大规模的FPGA芯片而言这是非常少的资源消耗。

3 结语

基于FPGA设计和实现UART,可以用片上很少的逻辑单元实现UART的基本功能。与传统设计相比,能有效减少系统的PCB面积,降低系统的功耗,提高设计的稳定性和可靠性,并可方便地进行系统升级和移植。

本设计具有较大的灵活性,通过调整波特率发生器的分频参数,就可以使其工作在不同的频率。采用16倍波特率的采样时钟,可以实时有效探测数据的起始位,并可对数据位进行“对准”中央采样,保证了所采样数据的正确性。该模块可以作为一个完整的IP核移植进各种FPGA中,在实际应用时可嵌入到其他系统中,很容易实现和远端上位机的异步通信。

-

QueueForMcu 基于单片机实现的队列功能模块2021-12-31 609

-

基于FPGA的UART模块设计与实现简介2021-06-01 909

-

一种基于FPGA的UART电路的实现2021-04-27 930

-

以FPGA为基础的UART模块的详细设计方案2020-07-07 1074

-

将UART功能集成到FPGA内部实现多模块的设计2019-10-18 3373

-

如何采用EDA或FPGA实现IP保护?2019-09-03 2248

-

一种基于FPGA的UART实现方法设计2019-06-21 2363

-

基于FPGA 的嵌入式系统程序开发实现对ARM 接口通信控制模块、芯片驱动模块的程序设计2017-11-18 3194

-

用xilinx fpga实现一个非标准的SPI功能模块2017-10-24 3365

-

基于FPGA/CPLD的UART功能设计2017-01-23 1229

-

用FPGA/CPLD设计UART2012-05-23 3794

-

FPGA与CPLD实现UART2011-12-17 753

-

基于ASIC/SoC的UART核的设计2010-06-19 517

-

SIMULINK功能模块的处理2008-06-19 3735

全部0条评论

快来发表一下你的评论吧 !