基于FPGA音频交换混合矩阵的设计与仿真分析验证

描述

音频交换混合矩阵是各种会议、演播、指挥系统的核心设备,连接不同的音频输入、输出设备,实现音频的交换及混合功能,并实现音频信号的控制与调度。

传统的音频矩阵通常基于模拟开关电路设计,设计复杂,实现难度较大,不适合构建中大规模交换矩阵。而且,大多数矩阵不具备音量调节及信号混合功能,需要配合调音台、信号混合器设备使用。

本文提出一种基于FPGA ( Field ProgrammableGate Array)的音频交换混合矩阵的设计方案。该方案以交换技术原理为基础,采用数字音频信号采样及处理技术,构建交换混合矩阵,实现了16 ×16路音频信号的交换、混合;设计及实现难度小,且可根据系统需求裁减或增加系统交换容量、设置音频信号采样精度及采样速率;每路输入、输出信号的音量可以独立进行控制;还具有输入输出延时低、信道间隔离度高、音质好的特点。

1 音频交换混合矩阵的数学模型

1. 1 交换系统原理

交换技术源于电话通信,其基本任务就是在大规模网络中实现各用户之间信息的端到端的有效传递。交换技术的原理就是通过设置好的路径,将源端的数据可控地发往目的端。

对于音频系统,交换即指将音频信号从输入端经过一系列节点转发到输出端。

1. 2 交换混合矩阵数学模型

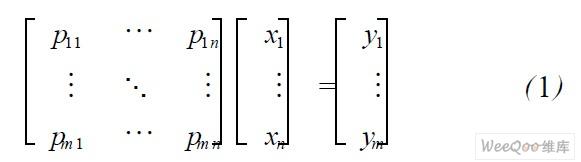

基于2. 1所述交换技术原理,可构建交换系统的一般数学模型。将多输入输出的交换系统抽象为一个矩阵P,其输入和输出信号抽象为两个向量( x,y) ,交换系统实现的功能就是将输入向量通过矩阵的运算转换为输出向量:

其中pij ∈[0, 1 ],代表输入与输出的对应关系。n和m 分别代表输入和输出信号个数。当n = 1时,该系统为单输入系统;当n > 1时,该系统为多输入系统。

当m = 1时,该系统为单输出系统;当m > 1时,该系统为多输出系统。

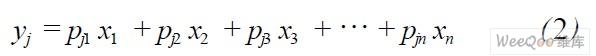

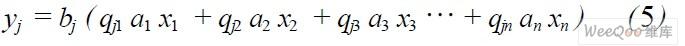

对于一个音频交换混合系统, pij即代表了某路输入与某路输出的对应关系,以及音量信息。最终,单独的某路输出信号yj 可以表示为:

本方案的核心技术,是将多路模拟音频输入信号转换为数字输入向量,并构建数字交换混合矩阵,通过对矩阵的运算得到数字输出向量, 并将输出向量转换为模拟音频输出信号,分配至各输出端口,最终实现音频交换混合矩阵。

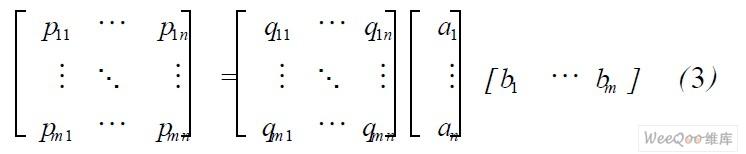

在此,设向量A、B 分别为输入和输出音量控制向量,矩阵Q 为控制矩阵,则交换矩阵P变换为:

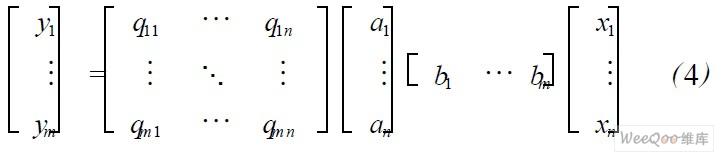

综上,构建起系统的最终数学模型为:

其中qji = 0, 1。

由式(4)可知,第j路输出的最终结果yj 为:

2 系统方案设计概述

2. 1 系统信号流程

根据式( 4)及式( 5) , 可构建出系统信号流程图,如图1所示。

图1 交换混合矩阵系统信号流程图。

ai 和bj 由音量控制芯片来实现,数/模及模/数转换分别由专用芯片来实现,矩阵Q 和多路加法器由FPGA来实现。

系统交换容量设定为16 ×16, 即n = 16, m =16。针对不同系统需求,可扩展或缩减交换容量。

2. 2 系统硬件设计

由系统信号流程图可知,系统总体的硬件模块由输入音量控制、数/模转换、交换混合矩阵、模/数转换、输出音量控制等组成。系统总体硬件模块框图如图2所示。

图2 交换混合矩阵总体硬件模块结构框图。

输入音量控制芯片选用PGA4311,其增益调节范围为31. 5 dB~ - 95. 5 dB。使用SPI总线对其进行控制。

输入模/数转换芯片选用PCM4204,该芯片采用IO接口控制工作模式和参数。具体设置方式见文献。

输出数/模转换及音量控制芯片选用PCM1681,工作于从机方式,使用I2C接口对其进行控制。具体设置及使用方法见文献。

通过对模/数及数/模转换芯片的设置,可以根据系统需求调整数字音频信号的采样精度及频率。

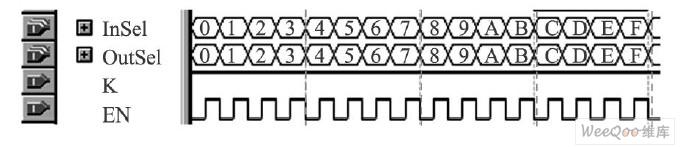

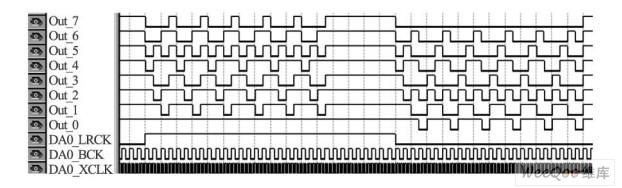

本文所述方案实例的采样频率为97. 7 kHz,采样精度为24 bit,采用左对齐PCM编码方式传输,其传输时序图如图3所示。

图3 PCM编码传送时序(左对齐)。

2. 3 FPGA及其程序设计

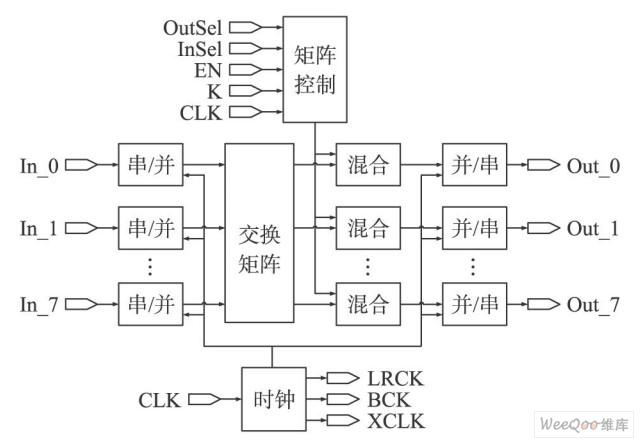

FPGA内部包含串/并转换、交换矩阵、混合、并/串转换、时钟模块和矩阵控制模块,其内部模块框图如图4 所示。FPGA 选用Altera的EP2C35 芯片,其具体参数见文献。

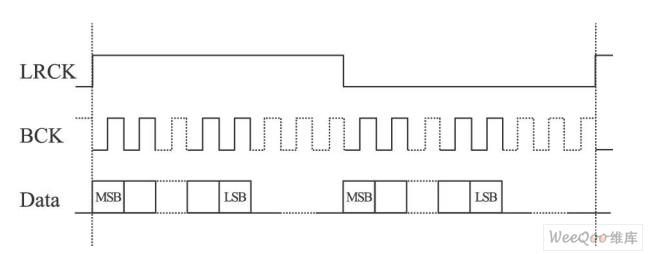

2. 3. 1 时钟模块

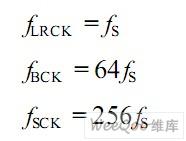

时钟模块的功能是为串/并、并/串转换模块提供统一的全局时钟。系统需要的时钟信号有三种,分别是:系统时钟( SCK) 、位时钟(BCK)和声道时钟(LRCK) ,各时钟频率由采样频率( fS )决定:

图4 FPGA内部模块框图。

本系统中,采样频率fS 为97. 7 kHz,通过一个50MHz的外部时钟信号分频产生上述各个时钟。

在模块内建立一个9 bit累加计数器Q,在时钟信号的上升沿完成一个递增计数, 当数值计到满值111111111时, 在下一个时钟周期将Q 置0。将XCLK、BCK、LRCK输出分别连接到计数输出的第0、第2和第8位,并将第3 - 第7位合并成另一个计数输出S_Count,用于控制串- 并和并- 串转换的位计数。所以,实际生成的fSCK为25 MHz, fBCK为6. 25MHz, fLRCK和fS 为97. 7 kHz。

2. 3. 2 输入串/并转换模块

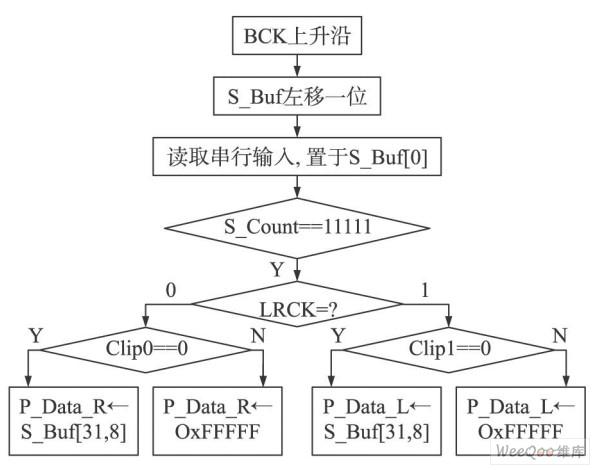

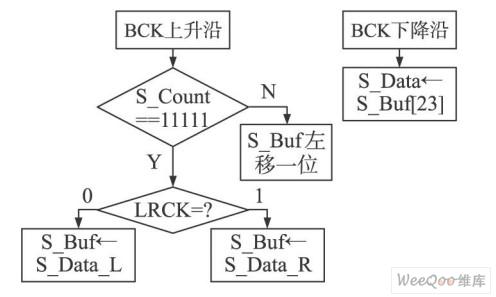

该模块负责将PCM4204输入的串行PCM编码转换为并行数据,送入交换矩阵模块进行处理。模块内部建立通过一个32 bit移位寄存器( S_Buf) ,用来存储串行数据,根据声道时钟(LRCK)的动作来控制并行输出。串/并转换流程如图5所示。

图5 串/并转换流程图。

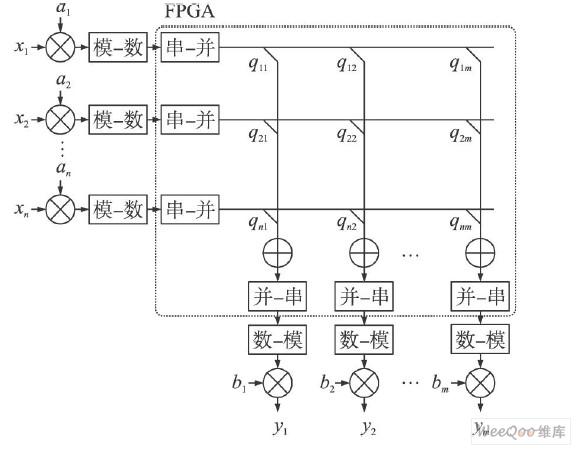

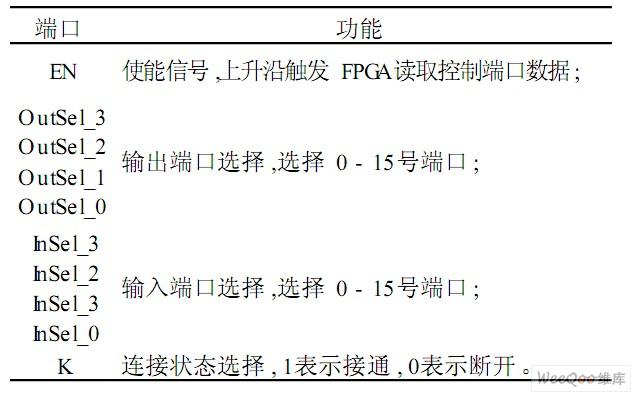

2. 3. 3 矩阵控制模块

该模块的功能为:接收外部控制单元的命令,控制矩阵实现转接操作。FPGA保留10个GP IO作为使能控制端口,定义为表1。

表1 矩阵控制端口定义

模块的输出是16组16 bit并行数据,形成一个矩阵表。其中,每组数据代表输出端口,该组中的每个bit代表对应的输入端口,表中的元素代表相应的输入与输出之间的连接关系, 0表示断开, 1表示连接。

使用时,先选择需要进行操作的输入和输出端口以及操作状态,然后向EN输入高电平,触发控制电路进行工作,将选择的输入与输出信号相连接或断开。

2. 3. 4 混合模块

该模块由数据缓冲寄存器(AdderBuf)和加法器(Adder)两部分组成。数据缓冲寄存器读取控制端口( Sel)的状态,然后判断各个输入是否有效,即是否送入到输出端口。若某输入端口有效,则将该端口数据直接送入加法器;若无效则送出数据0。

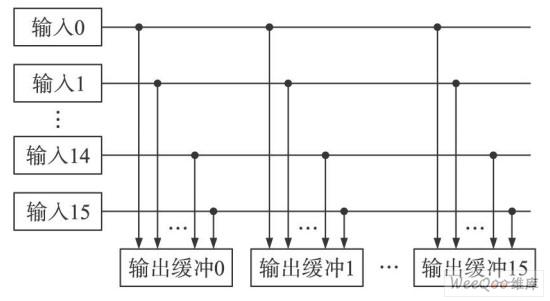

2. 3. 5 交换矩阵模块

交换矩阵的工作原理是一个16转256的分配器,将每一路输入分配为16路,分别送入每一路输出的混合模块中。其结构如图6所示。

图6 交换矩阵模块结构图。

2. 3. 6 输出并/串转换模块

该模块负责将混合模块输出的24 bit并并行数据转化为PCM1681能够接收的串行PCM编码。数据传输格式与PCM4204相同。模块内部建立一个24 bit移位寄存器,用来产生串行输出,根据声道时钟(LRCK)的动作判断读取并行输入。并/串转换流程如图7所示。

图7 并/串转换流程图。

3 系统仿真及实现

3. 1 系统仿真

FPGA总体端口及模块框图如图8所示。

图8 FPGA总体端口及模块框图。

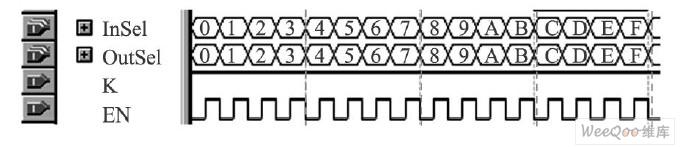

由时钟输入端(CLK)输入50 MHz时钟信号;在交换控制端口送入控制信号,使In_0与Out_0相连, In_1与Out_1相连, ……, In_7与Out_7相连,控制信号输入如图9所示。

图9 控制信号输入。

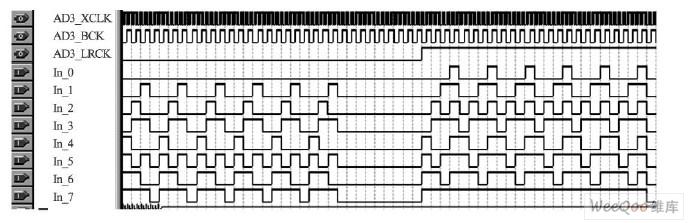

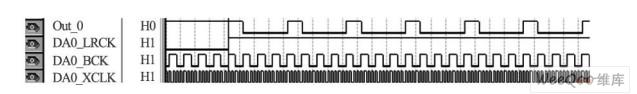

在第一路串行信号输入端( In_0)的左声道输入时序输入16进制串行数据000000,在右声道输入时序输入111111;同理,在In_1的左声道输入时序输入222222,在右声道输入时序输入333333; ?在In_7的左声道输入时序输入EEEEEE,在右声道输入时序输入FFFFFF。串行数据输入如图10所示。

图10 串行数据输入。

系统的串行输出端有相应数据输出, Out_0 端左声道输出数据为000000, 右声道输出数据为111111,与In_0输入数据一致;Out_1端左声道输出数据222222,右声道输出数据333333,与In_1输入数据一致; ?; Out_7 端左声道输出数据EEEEEE,右声道输出数据FFFFFF,与In _7 输入数据一致。

串行数据输出如图11所示。

图11 串行数据输出。

改变控制端口数据,使In_1的左声道输入(数据为222222 ) 与In _ 2 的右声道输入(数据为555555)与Out_0的左声道输出连接。由图3 - 5可见,Out_0串行数据输出变为777777。串行数据混合输出如图12所示。

由以上仿真结果可知, FPGA 整体设计能够实现串行数字音频信号的交换与混合,达到预期设计要求。

图12 串行数据混合输出。

3. 2 系统实现

交换混合矩阵实物照片如图13所示。

图13 交换混合矩阵实物照片

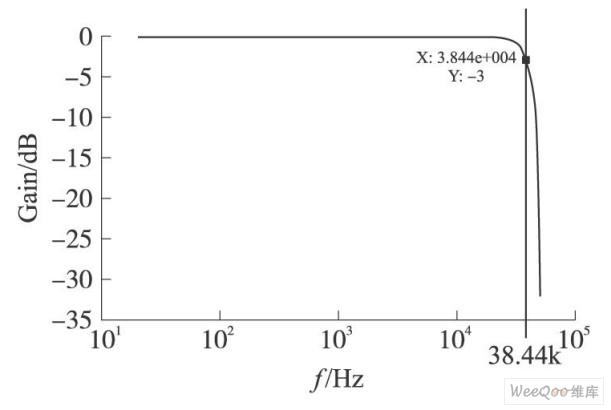

实物测试时,先将交换混合矩阵接入嵌入式控制系统,利用嵌入式控制系统对其进行控制。采用计算机、MP3、便携式CD 机、信号发生器等播放的音频信号作为输入源,扬声器及耳机、示波器等作为输出设备,测试交换、混合及音量调节功能。经*测试,输出音频信号无明显失真。在多路音频信号混合输出时,仍然可以保证较好的信号质量。输入输出延时的测量波形如图14所示,约为620μs。通过逐点测量得到幅频特性曲线如图15所示,通频带为20 Hz~38. 44 kHz。

图14 输入输出延迟测量波形。

图15 幅频特性曲线。

测试结果证明,交换混合矩阵能够正确接受控制系统的命令,完成音频信号的交换、混合及音量调节功能。

4 结论

本文针对音频交换系统应用需求,提出了一种基于FPGA音频交换混合矩阵的设计方案,并进行软硬件设计阐述及仿真,并完成了实物制作与测试。

本文所述方案采用FPGA作为交换混合矩阵的核心器件,因此具有较强的通用性,可根据实际需要裁减或增加交换容量、配置音频信号采样频率及采样精度等特点。

经仿真及实物测试,基于FPGA的音频交换混合矩阵能够实现音频信号的交换、混合及音量调节,同时具有延时低、隔离度高、音质好的特点,可适用于各种会议、指挥、通信等场合。

-

fpga原型验证平台与硬件仿真器的区别2024-03-15 2304

-

IP交换矩阵的关键参数 IP交换矩阵测试原理概述2023-12-04 4406

-

高清混合矩阵切换器解决方案在不同场景下的选择技巧分析2023-08-31 1085

-

混合信号FPGA的智能型验证流程是怎样的?2021-04-30 1107

-

FPGA开发Vivado的仿真设计案例分析2020-12-31 6202

-

FPGA设计的仿真验证概述2019-04-10 2707

-

FPGA交换矩阵的使用实现2019-01-26 2507

-

【小梅哥FPGA进阶教程】第一章 FPGA矩阵键盘驱动设计与验证2017-01-07 5598

-

FPGA论坛精华帖(验证仿真版)2015-11-30 644

-

FPGA验证技术简介2012-05-18 8815

-

基于FPGA的混合信号验证流程2011-09-15 1135

-

基于MT90系列与FPGA的交换矩阵设计2010-07-15 579

-

基于MT90系列与FPGA的交换矩阵设计平共处2009-05-05 1806

全部0条评论

快来发表一下你的评论吧 !