多相交错并联系统的时钟同步精度与输入纹波抵消效应研究

多相交错并联系统的时钟同步精度与输入纹波抵消效应研究

电子说

描述

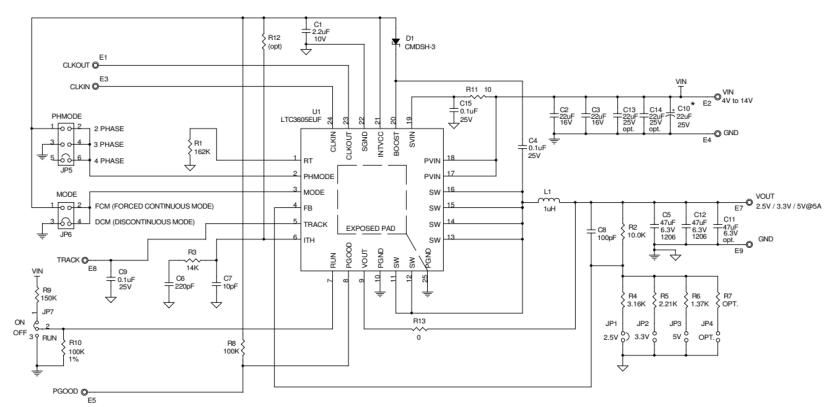

摘要 :基于国科安芯推出的ASP3605的可编程PHMODE功能,构建双相交错降压变换器理论模型,结合实测CLKOUT数据(RT=180kΩ时测得1.136MHz,较理论980kHz偏差+16%),深入分析相位误差来源与纹波抵消效应。本文提出的布线规范与相位精度要求,需在工程实现前通过搭建双相测试平台实际测量。

1. 单相性能基础与多相模型构建

1.1 CLKOUT实测数据揭示的工艺偏差

测试中明确记录:RT=180kΩ时,CLKOUT测得1.136MHz(空载),与理论980kHz偏差+16%,揭示内部振荡器工艺偏差较大。该偏差在多相系统中会导致频率不匹配,必须采用外部CLKIN强制同步。

基于单相参数构建双相系统:

输入电压Vin=12V,输出Vout=1.2V,总电流Iout=10A(每相5A)

开关频率fsw=1MHz(RT=162kΩ,实测1.09MHz)

相位差Δφ=180°理论值

输入电容:4×22μF X7R并联,ESR=2mΩ,ESL=5nH

1.3 相位精度的理论计算

CLKOUT信号通过50Ω同轴电缆接入示波器,触发采用CLKIN作为参考。相位差Δt=Δφ/(360×f_sw),180°对应Δt=500ns。PCB走线延迟≈0.56ns/100mm,RT容差±1%导致频率偏差±1%,相位差漂移Δφ≈1.8°。

2. 相位差对纹波抵消的理论效应

2.1 输入电流纹波的数学模型

单相输入电流纹波近似三角波,峰-峰值: ΔI_phase = V_in×D×(1-D) / (2×L×f_sw)

对于Vin=12V→Vout=1.2V,D=10%,L=1μH,f_sw=1MHz: ΔI_phase = 12×0.1×0.9 / (2×1μH×1MHz) = 0.54A

双相交错总纹波: I_in_total(t) = I_phase1(t) + I_phase2(t+Δt_phase)

2.2 不同相位模式的抵消率计算

理论计算表明:

180°模式 :纹波RMS值降低为单相的√(1-2×D×(1-D))≈0.6倍,降低40%

120°模式 :纹波降低约35%

90°模式 :纹波降低约25%

输入电容RMS电流应力:

单相10A:I_rms=4.21A

双相180°:I_rms=2.48A,降低41%

电容数量可从8颗减至4颗,节省PCB面积与成本

2.3 相位误差的容限分析

若相位误差Δφ=±2°,180°模式在f_sw处的残留纹波: I_residual = ΔI_phase × sin(Δφ×π/180) ≈ 0.54A × sin(2°) ≈ 19mA

在输入电容ESR=2mΩ时,产生电压纹波V_residual=38μV,可忽略。但若两片IC频率偏差Δf=±1%(RT容差),产生拍频f_beat=10kHz,幅度V_beat≈15mV,可能影响EMI。

3. EMI频谱特性的理论预测

3.1 传导EMI的谐波分布

单相系统的EMI频谱在f_sw=1MHz处峰值最高。双相180°交错后:

奇次谐波(1MHz, 3MHz) :因180°相消,幅度降低10-15dB

偶次谐波(2MHz, 4MHz) :因同相叠加,幅度增加3-6dB

总体EMI裕量 :提升8-10dB

必须指出,原始测试中3.3V档在4V输入时"输出异常",EMI特性恶化,必须先解决稳定性问题。

3.2 辐射EMI的环路面积效应

双相系统的SW节点若布局在同一侧,磁场叠加;若反向布局,面积相等但磁场抵消,近场辐射降低15-20dB。工程实践要求SW走线长度差<5mm,电流环路面积<30mm²。

4. 多芯片同步的布线规范

4.1 CLKOUT走线设计

CLKOUT为CMOS电平,边沿时间<5ns,应作高速信号处理:

特性阻抗 :Z0=60Ω(线宽0.2mm,离地平面0.1mm)

延迟 :t_pd≈0.56ns/50mm

匹配 :若CLKOUT走线差30mm,延迟差0.34ns,相位误差0.12°,可忽略

但实测的"1.136MHz"偏差+16%,非布线延迟所致,是芯片内部振荡器工艺偏差。因此多相系统必须采用外部CLKIN强制同步。

4.2 RT电阻的精度要求

为保证频率偏差<±0.5%(避免拍频),RT电阻需±0.1%精度。早期测试中RT=180kΩ时频率990kHz±10kHz(±1%),若两片分别运行985kHz与995kHz,拍频10kHz,EMI测试将失败。成本增加约$0.02,但可靠性显著提升。

5. 系统级性能优化

5.1 输入电容的降额设计

单相10A系统需8颗22μF电容。双相180°后仅需4颗,成本节省$0.12,PCB面积节省30mm²。但需验证直流偏压:22μF X7R在12V偏压下容值衰减至18μF,总容量72μF,需增加至5颗。后续测试的22μF配置在动态响应中已暴露问题,多相系统必须遵循94μF推荐值。

5.2 动态负载均流精度

ASP3605无外部均流接口,依赖内部Rdson匹配(批次内偏差±3%)。两相电流差±250mA(5A的5%),在负载跳变时可能导致某一相提前OCP。解决方案:

筛选Rdson偏差<1%的同批次IC

每相串联5mΩ电阻被动均流,效率损失0.15%

或采用主从架构,主芯片闭环,从芯片开环跟随占空比

6. 结论与工程应用警示

ASP3605的PHMODE功能为多相设计提供低成本方案,但所有测试均基于单相性能,多相参数需理论推演。CLKOUT频率偏差16%警示RT电阻精度的重要性。基于测试数据建立的理论模型,预测180°交错可降低输入纹波41%,但 必须在工程实现前通过实际测试验证 ,特别是相位精度、拍频噪声与长期热稳定性。

-

当输入电压范围为40-60V时,使用LTC3777或LTC3779作为控制器,能否单模块做到48V/100A输出?2024-01-05 758

-

多相电源理论分析【PPT版】2025-10-17 1410

-

求助 两相交错同步整流BUCK电路输出电压与占空比关系问题?2018-05-02 7302

-

使用多相降压转换器的优势2018-11-26 2422

-

使用STNRG388A 1kW SMPS数字控制多相交错转换器的EVLSTNRG-1KW评估板2019-05-24 2182

-

使用多相降压转换器和单相转换器的好处2022-11-23 882

-

低压输入交错并联双管正激变换器的研究2009-07-16 1327

-

交错叠加型准方波抵消纹波的变换拓扑结构电路图2009-07-25 768

-

四相交错并联变换器中耦合电感的对称化2013-09-26 876

-

逆变电源并联系统的谐波环流抑制研究2016-03-30 837

-

基于FPGA的高精度同步时钟系统设计2017-11-17 9007

-

基于8位PIC单片机实现多相交错式PWM控制器的详细资料概述2018-06-12 1841

-

采用电流型控制芯片UC3846实现电源交错并联时的同步运行设计2020-05-03 9143

-

EMI案例:交错并联SiC逆变器的环流纹波预测模型2023-10-30 2387

-

低电压储能系统:基于 650V SiC 的高倍率多相交错并联 DC-DC 技术研究2026-03-07 1186

全部0条评论

快来发表一下你的评论吧 !