通过采用FPGA器件和EZ-USB FX2芯片实现数据采集和传输系统设计

描述

引 言

随着社会的发展和技术的进步,各种计算机的外围接口不断的推陈出新。USB接口已渐渐成为现今个人计算机上最重要的接口之一,并以其传输速度快、使用方便和价格低廉等特点成为现今一般消费性电子产品和工业控制设备上不可缺少的接口。Cypress公司的EZ-USBFX2是一个USB2.0集成外围控制器,它具有通用串行总线(USB)的3种传输模式:1.5 Mb/s的低速模式,12 Mb/s的全速模式,480 Mb/s的高速模式。因此,本设计选用USB2.0芯片CY7C68012、Altera公司的FPGA和TLC5510组成一个通用的数据采集和传输系统。该系统结构简单,采集和数据传输可靠,能够满足现今高速设备的要求。

1 系统硬件设计

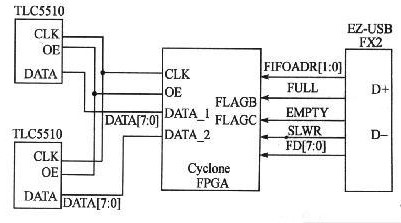

本系统主要分为两个部分,一部分是由2片TLC5510和FPGA构成的数据采集模块,另一部分是由FPGA和EZ—USB FX2构成的数据传输模块。系统的框图如图1所示。

(1)数据采集模块

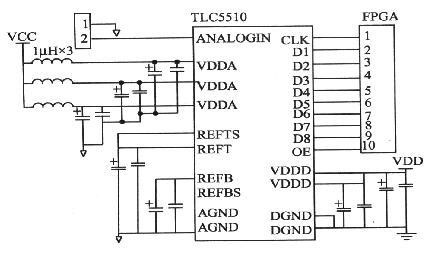

经过调理后的信号进入模数转换电路,选用的高速AD芯片是TI公司的TLC5510。TLC5510是CMOS、8位、20 Msps的模数转换电路。它采用半闪速结构,单电源5 V工作时,功耗只有100 mW,内含采样和保持电路,具有高阻抗方式的并行接口和内部基准电阻。与闪速转换器相比,半闪速结构减少了功率损耗和晶片尺寸。通过在两步过程中实现转换,可以大量地减少比较器的数目,转换数据的等待时间为2.5个时钟周期,且高速转换的同时能够保持较低的功耗。TLC5510与FPGA的接口电路如图2所示。

FPGA提供TLC5510 20 MHz的工作时钟和使能输出信号OE,低电平有效,同时接受TLC5510的采样数据。由于系统需要同步的两路采样,所以由FPGA输出的时钟和使能输出信号OE同时控制2个TLC5510。这样FPGA就可以同时收到两路同时采样的信号数据,将其存入两个独立的异步FIFO中。

值的注意的是,实验中将FPGA产生的工作时钟和使能输出信号先输入74HCT573,然后由74HCT573的输出去控制两路的TLC5510。这主要是完成将FPGA的CMOS电平转换成TTL电平的工作。在实验的初期,未经过电平转换的信号在控制TLC5510时,得不到稳定数据。后来经过改善后,TLC5510能够稳定、准确地完成采样和数据输出。

(2)数据传输模块

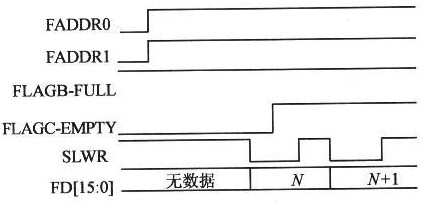

在数据传输模块中,为了保证较高的传输速度,使用不经过CPU的SLAVEFIFO控制工作模式。模块的基本工作过程为:当A/D采样数据存储满FPGA中的FIFO后,FPGA根据SLAVEFIFO的控制时序产生相应的控制信号,将在FIFO中的数据传输给EZ-IJSB FX2的内部端点FIFO,而当内部端点存储满后,FX2自动将数据传输到上位机。外部控制器FPGA对FX2的控制进程如下:

①IDLE,当写事件发生时,转向状态1。

②状态1,指向EZ-LJSB FX2的内部端点IN FIFO,激活FIFOADR[1:0],转向状态2。

③状态2,如果内部端点FIF0满标志为“假”(FIFO不满),则转向状态3;否则停留在状态2。

④状态3,传送总线驱动数据。产生一个SLWR跳变,转向状态4。

⑤状态4,如果有更多的数据要写,则转向状态2;否则,转向IDLE。

EZ-JSB FX2内部端点FIFO异步写的时序如图3所示。

2 FPGA的模块设计

在系统中,FPGA构成了数据采集系统和数据传输系统的“桥梁”,完成对TLC25510的控制和数据的存储,同时也完成对EZ-USB FX2单片机的控制。利用FPGA强大的功能,使电路的结构得到了简化,不需要利用分立器件来完成对数据的存储。因此,在FPGA中需要构成4个模块:2片FIFO数据存储模块、数据通道选择模块、控制模块和输出20 MHz时钟的PLL模块。

(1)2片FIFO数据存储模块

FIFO数据存储模块主要完成对A/D转换数据的存储。由于需要两路同时采集数据,所以要有2个FIFO模块,这样易于对数据的存储和传输控制。每个FIFO存储模块的存储容量定为2 048 B,可通过MegaWizard工具来调用。

(2)数据通道选择模块

数据通道选择模块主要是针对两路的数据读取和传输而设计的。当A/D转换器采集到对应的数据后,存入两个异步FIFO存储模块中。在两个异步FIFO存储模块存储满后,对FIFO存储模块数据的读取是关键。数据通道选择模块的基本原理是在控制模块对读取数据进行计数,当把其中的一个FIFO存储模块读取完后,由控制模块发出通道切换信号,由数据通道选择模块切换数据通道,再读取另一个FIFO存储模块的数据。

(3)控制模块

控制模块要完成对TLC5510、FIFO存储模块、数据选择模块和EZ—USB FX2的控制,这是整个系统的关键。根据系统实现的功能和各个模块的控制时序,控制模块将产生相应的控制信号,实现系统的采集和存储的功能。

(4)20 MHz时钟的PLL模块

系统提供的FPGA外部时钟频率为50 MHz,而TLC5510的最大采样工作频率为20 MHz。所以通过对前置分频参数N=5、倍频器参数M=2的设置,将50 MHz钟频率分频成20 MHz的时钟作为采样时钟和系统的工作时钟。

3 EZ—USB FX2的固件设计

固件程序是指运行在设备CPU中的程序。只有在该程序运行时,外设才能称为具有给定功能的外围设备。C2ypress公司为FX2固件开发提供了一个固件库和固件框架,都是在Keil C51集成开发环境下开发的。固件库提供了一些常量、数据结构、宏、函数来简化用户对芯片的使用。固件框架实现了初始化芯片、处理USB标准设备请求以及挂起状态下的电源管理等功能。该框架不添加任何代码,编译后生成的.HEX文件载人芯片就能和主机进行基本的USB通信。用户主要的工作就是选择适合的传输方式,添加需要使用的端点,在框架预留的地方(如TD_Init()、TD_Poll()等函数中)添加初始化代码和完成特定功能的代码。这样大大简化了用户对程序的编写,在不十分了解USB2.O协议的情况下,也能通过代码的编写,实现USB的传输功能。

4 EZ—USB FX2的驱动程序

该系统需要通用驱动程序和下载固件的驱动程序。通用驱动程序完成与外设和用户程序的通信及控制;而下载固件的驱动程序则只负责在外设连接USB总线后把特定的固件程序下载到FX2的RAM中,使FX2的CPU重启,模拟断开与USB总线连接,完成对外设的重新设置。FX2根据新的设置安装通用驱动程序,重新枚举外设为一个新的USB外设。通用驱动程序一般不需要重新编写,用Cypress公司已经编好的驱动ezusb.sys;而下载固件程序的驱动则必须定做。

5 上位机用户程序

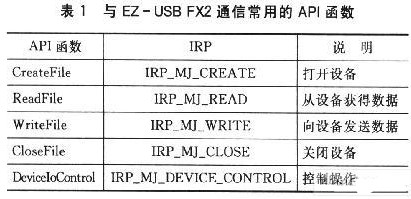

上位机用户程序主要通过VC++完成。实现从USB设备从下位机读取指定数量的数据和向下位机发送特定的控制数据。用户程序对EZ—USB FX2的控制,主要是通过I/0控制调用来访问ezusb.sys通用驱动程序,而对I/O控制的调用是通过win32的API函数来完成的。因此,用户程序通过对API函数的调用来实现与驱动程序进而与硬件的通信。API函数的执行与驱动函数中的一些分发例程相对应。与EZ-USB FX2通信常用的API函数如表1所列。

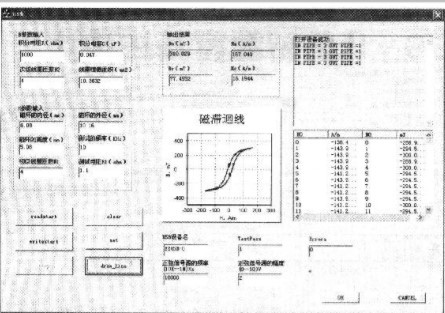

应用程序先通过CreatFile()得到设备驱动程序的句柄,然后使用DeviceloControl()来提交I/O控制码,并且设置好读取和发送数据的缓冲区,最后通过CloseFile()来关闭设备。图4是上位机应用程序界面。

结 语

EZ—USB FX2使上位机与下位机之间的数据传输更加快捷和可靠。基于FPGA和EZ-USB FX2的数据采集和传输系统满足现代高速设备对传输速度的要求,解决了传输速度慢的瓶颈。通过FPGA的模块设计、EZ-USB FX2的固件设计和上层应用程序设计,实现了整个系统的数据采集和传输。

-

基于接口芯片与FPGA器件实现生物电信号数据采集的设计2020-08-13 2104

-

USB控制中心找不到赛普拉斯EZ-USB FX2(689613)EEPROM丢失2019-05-09 3969

-

EZ-USB FX2无法工作2019-03-07 2261

-

如何将EZ-USB FX3代码移植到FX22018-10-16 2431

-

USB 在EZ-USB® FX2™ 和 FX2LP™ 中通过同步或批量端点的流数据-AN40532017-10-10 872

-

CY3674 EZ-USB® FX1 / CY3684 EZ-USB FX2LP™ Development Kit2016-06-21 1806

-

高速USB数据采集系统方案设计2015-10-27 4721

-

基于EZ-USB FX2和MAX1195的数据采集系统2011-12-06 3158

-

基于EZ USB FX2的USB2.0系统软件开发2011-09-13 749

-

EZ-USB FX2接口在诱发电位仪系统中的应用2011-05-03 1221

-

星载电子设备多余物数据采集系统的设计2011-03-21 905

-

利用USB2.0技术的高速双路数据采集系统2010-03-03 1340

-

基于USB2.0技术的高速双路数据采集系统2009-09-15 646

-

基于EZ_USB与FX2的通用数据传输模块设计2009-08-13 913

全部0条评论

快来发表一下你的评论吧 !