基于DSP5402芯片HPI接口技术分析

描述

1 引 言

TMS320VC5402是TI公司的一种16位数字信号处理器,以其独有的低功耗和高性价比,受到用户的欢迎。C54x操作灵活及运行速度高;使用改进的哈佛结构,具有专用硬件逻辑的CPU、片内存储器和外设接口,以及高度专业化的指令集。而且, C54系列DSP与主机连接通过HPI(Host Port Interface)接口,以逻辑电路设计简单、不需要额外的存储器和程序更新方便优点,可以应用灵活多样的引导加载模式以实现接口和处理功能开发。

HPI口是C54x DSP系列芯片内部的并行接口部件,用于与其他总线或CPU主机之间进行连接通信,主机是HPI口的主控者,通过专用地址和数据寄存器、HPI控制寄存器以及外部数据和接口控制信号与HPI口通信。

本文基于对一个脑电信号采集系统中数字处理电路部分的研究,设计并实现了TMS320VC5402应用程序的HPI自举加载,HPI方式通信,详细介绍了调试方法与过程,对开发

基于DSP处理芯片的脑电信号采集系统有很大的参考价值。

2 系统介绍

脑电信号(EEG)是一种比较特殊的微弱信号。它是由脑神经活动产生并且始终存在于中枢神经系统的自发性电位活动,含有丰富的大脑活动信息。脑电信号的采集处理对于生物医学工程学研究具有重要意义,可以为临床手术中的麻醉镇静监护分析提供必要的数据。脑电信号数据采集系统主要功能是将人脑部的生物电信号通过脑电极提取出来,经过放大处理,传输至上位机显示并存储。本文所研究的数字脑电采集系统就是基于DSP 芯片VC5402 处理能力强、实时性高等优点的应用。由系统模拟部分对脑电信号进行放大和预处理,经过A/D 变换后送往数字处理部分。数字处理部分由DSP 芯片和USB 等芯片构成,由DSP 控制实现对脑电数字信号的采集与处理,并完成DSP 与USB 芯片的通信,最后通过USB总线将数据送往上位机实时显示与储存。

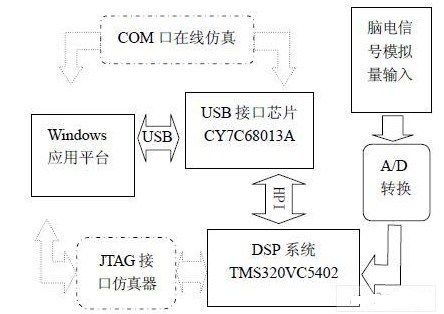

系统的核心为TMS320VC5402,有三个功能:首先,控制整个系统模数转换并设置各种模拟部分的参数;其次,对A/D变换后的数据进行各种算法处理,包括信号滤波与分析等,也是高性能脑电数字信号采集器的重点;最后完成数据接口功能,把数据按一定的格式打包,通过高速的HPI总线把数据交给USB接口芯片并送往PC机。图(1)为整个方案的原理图,其中虚线部分为调试过程示意图。调试过程中,通过集成开发环境KEIL C51和CCS 5000系统,可视化的调试过程有利于整个方案的后期调试。

图 1 系统方框图

3 透明式USB通信设计

VC5402 自身提供了标准的串行口, 时分复用(TDM) 串行口和自动缓冲串行口BSP(Auto-Buffered Serial Port),这些接口必须通过PC 机的串口与PC 机进行通信,而PC 机的串口无法满足高速数据采集对速度的要求。本文采用CY7C68013A 芯片通过HPI(HostPort Interface)接口和DSP 芯片TMS320VC5402 相连,再由CY7C68013A 通过USB2.0 将数据传送到PC 机上,方便满足系统对传输速度的要求。

3.1 硬件

CY7C68013A芯片有56脚SSOP,56脚QFN,100脚TQFP以及128脚TQFP四种封装形式。引脚少的芯片占用PCB面积小,价格低,功能基本满足需要。但在开发阶段,选取100脚TQFP封装形式以支持在线调试,可以节省开发时间。实际生产阶段,可以采用56脚封装芯片来做实际电路应用。

3.2 开发工具

本文选用Keil uVision3作为USB接口芯片固件程序的开发工具能提高开发效果。KeiluVision3是一个集成开发环境,拥有C51编译器、A51汇编器以及BL连接定位器等工具和模拟仿真与调试器。它能够支持C程序和汇编程序混合的编程工作,对软件的开发便利。

3.3 固件开发与调试过程

在编写固件程序时需要用到大量的函数,可以应用CY7C68013A芯片的开发工具包。该开发包提供了开发所需的固件框架程序以及一些例程,以简化其固件开发过程。在Cypress C51固件框架程序下的主要工作有:

1、修改设备描述符表: USB 设备与主机建立通信前须先向主机提供具体配置,包括设备的厂商、产品识别号(VID,PID),设备的供电方式以及能量消耗等系列信息。而有关设备的信息是通过设备描述符表提供给主机的,从而决定主机使用哪一个USB 设备驱动和采用哪种方式建立与设备之间的连接。

2、CY7C68013A有可编程接口GPIF。可编程接口GPIF是主机方式,可以由软件编写读写控制时序,几乎可以和所有8/16 bit接口的控制器、存储器和总线进行无缝连接。在调试过程中,把CY7C68013A芯片的串口接到PC机的串口上,无需仿真器就能完成在线仿真工作。利用CYPRESS提供开发工具包的Monitor程序,能对应用程序实施单步运行、断点设置和变量查看等调试工作,既降低了固件程序的开发难度,又加速了USB系统开发的过程。

4 DSP部分设计

4.1 HPI方式自举加载

VC5402片内ROM 固化有TI公司的自举引导程序Bootloader,在上电复位时把用户代码从外部存储器引导到片内RAM 并运行。VC5402支持多种引导方式,如HPI引导、并行EPROM引导、并行I/O引导、串行口引导等。DSP采用哪种引导模式取决于硬件设计。VC5402上电复位后,先检测MP/MC引脚,如果MP/MC=“0”,表示使用片内ROM引导。此时,DSP从0xFF80处开始执行TI的片内引导程序。进入引导程序后,首先HINT引脚变为低电平,然后开始检测INT2是否为低电平(有效)。若INT2为低电平,则进入HPI引导方式;否则,检测其它引导方式是否有效。在硬件连接上,为了使VC5402复位后进入HPI启动方式,直接使INT2接到HINT引脚上,使HPIENA引脚接高电平。对HPI接口的操作主要通过以下三个寄存器来完成:HPI地址寄存器(HPIA)、数据锁存器(HPID)和控制寄存器(HPIC)。如当前进行的是读操作,则HPID中存放的是要从HPI存储器中读出的数据;如果当前进行的是写操作,则HPID存放的是要写到HPI存储器的数据。

4.2 软件部分设计

CCS(Code Composer Studio)是TI开发的一个DSP集成开发环境。其集成了常规的开发工具,如源程序编辑器、代码生成工具(编译器,连接器)以及调试环境等。CCS的编译器和链接器生成COFF格式文件,用HEX转化程序hex500.exe将COFF格式代码转换为标准的ASCII十六进制格式TI Tagged,支持16位地址。转换而成的Hex文件为ASCII码形式的,不能用于HPI自举,需将其转换为二进制(Bin)格式。

4.3 用户代码下载(HPI)

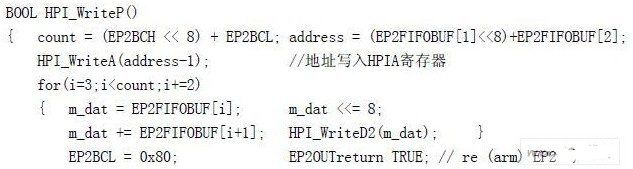

由于Intel的HEX代码格式是分段的,本文编写的代码段,是将一个Intel 的HEX代码段通过HPI接口写入DSP RAM中。下面代码段为HPI加载子程序,count为要写入代码的长度,address为起始地址,EP2FIFOBUF是指向HEX代码段的指针,HPI_WriteA子程序功能是写HPI地址寄存器,HPI_WriteD2完成部分程序的写入。代码如下:

4.4 写入DSP入口地址并运行

在TMS320VC5402进入HPI启动模式后,它将一直检查0X007F这个地址是否为0,如不为0,则跳转到0X007F指向的地址处执行代码。在将DSP的代码写入之后,只需将程序的入口地址写入0X007F这个地址,DSP将自动跳转到入口执行程序。程序的入口地址可以在CCS生成的.map文件中看到,其格式如:ENTRY POINT SYMBOL: "_c_int00" address: 000020be。

由于调用的是HPI_WriteD2()函数写数据,而HPI_WriteD2()在写数据之前,会自动将地址+1,所以在调用之前写入地址时,调用的是HPI_WriteA(0x007E),这样,最后调用HPI_WriteD2(m_dat)时,地址会自动指向0X007F。

4.5 观察写入代码

TMS320VC5402 在仿真时候其HPI接口也是正常工作的,这就方便了对HPI启动方式的调试。首先把5402连接到仿真器上,然后打开CCS5000集成环境。此时可以利用CCS5000的MemoryView来观察5402的内部RAM数据。调试中,先通过HPI接口把DSP的代码下载进去,再通过CCS5000集成环境观察,同时用UltraEdit十六进制编辑器打开由HEX500.EXE生成的.HEX文件。由于两者都是以ASCII码形式显示,可以直观地比较各个地址空间中的代码是否完全相同以及下载的代码是否完全正确。

4.6 整体方案测试效果

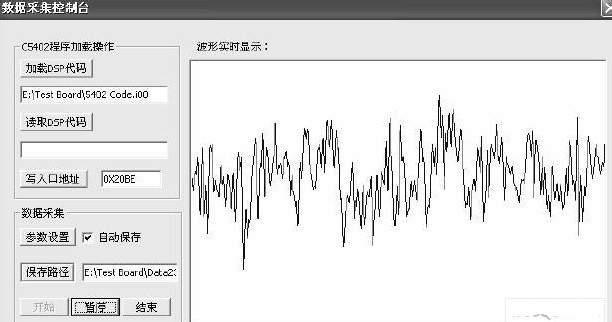

上述的各个模块调试通过后,又编写了上位机应用程序。上位机应用程序功能包括:建立USB 通信、加载DSP 代码、读取DSP 代码、写入口地址、数据采集与保存等功能。在把各个模快连接之后,用控制台通过HPI 接口加载DSP 代码5402 Code.i00,并写入程序入口地址0x20BE,启动下位机进入采集过程。图2 为上位机控制台应用程序截图。

图2 应用程序截图

5 结 论

利用 C54x 的HPI 接口在脑电数据采集系统中的设计与实现,可用于自发脑电信号实时准确的高速采集。如从DSP 的实际应用环境出发,利用DSP 的HPI 加载方式和JTAG 调试相结合的开发模式,可以在线调试该电路板的制作,自行编制相应的主机软件,设计DSP KERNEI和HPI 接口逻辑,还可以实现开发基于HPI 自举和通信的DSP 应用设计方案。这样做可以缩短开发周期,且硬件资源透明。该透明化开发过程更利于学习者理解和掌握DSP 的软硬件原理。该方案还可以从脑电采集系统设计推广到其它领域。

将USB接口芯片CY7C68013A(100引脚)的在线仿真和DSP芯片TMS320VC5402的JTAG仿真结合起来,设计VC5402基于USB2.0和HPI自举加载的脑电采集系统。通过CCS5000集成环境,能即刻查看DSP内部HPI加载代码,使该方案设计的采集系统直观地调试并缩短开发时间。该方案还可以从脑电采集系统设计方面推广到其它领域。

-

PCI总线接口与DSP的HPI接口2011-11-29 7153

-

HPI方式自举在TMS320VC5402 DSP芯片上的实现2009-08-20 2858

-

低价出售自己的DSP5402开发板, 300元2011-09-24 3368

-

求助关于DSP5402的定时器1如何使用?2014-09-30 2870

-

基于HPI主机接口的多处理器系统2019-06-06 1953

-

请问有谁做过DSP5402的指纹识别开发吗?2019-10-28 1710

-

如何使用HPI对DSP进行自举?2021-04-07 1158

-

如何去设计VC5402的HPI口与PC***的接口?2021-05-26 928

-

PC/104 总线与TMS320VC5402HPI 口通信的解决方案2009-05-31 723

-

HPI接口在脑电数据采集系统中的实现2010-01-07 774

-

基于DSP芯片TMS320VC5402的HPI通信设计2011-02-28 869

-

HPI接口技术应用2011-09-02 927

-

基于DSP5402的语音处理系统2011-09-08 1339

-

TMS320VC5402与单片机的HPI口通信设计2011-09-13 2615

-

ARM芯片通过HPI接口与DSP通信的接口技术2022-07-05 780

全部0条评论

快来发表一下你的评论吧 !