如何设计一颗车规级MCU芯片?从架构到认证的全流程实战指南

如何设计一颗车规级MCU芯片?从架构到认证的全流程实战指南

电子说

描述

在汽车电子的 “神经中枢” 里,车规级 MCU 芯片是无可替代的核心 —— 它主导着车身控制、电动助力转向(EPS)、电子稳定程序(ESP)、电池管理系统(BMS)等关键场景的实时控制,直接关系到驾驶安全与车辆可靠性。与消费级 MCU 不同,车规级 MCU 需在 - 40℃~150℃的宽温环境、10g 振动的机械应力、200V/m 的电磁干扰下稳定运行,同时满足 ISO 26262 功能安全与 ISO/SAE 21434 信息安全的严苛要求。

本文结合头部厂商的实践经验,从需求定义、架构设计、核心模块开发到认证落地,拆解车规级 MCU 芯片的完整设计流程,为硬件工程师、嵌入式开发者提供可落地的技术指南。

一、设计前置:明确车规级 MCU 的核心需求与指标

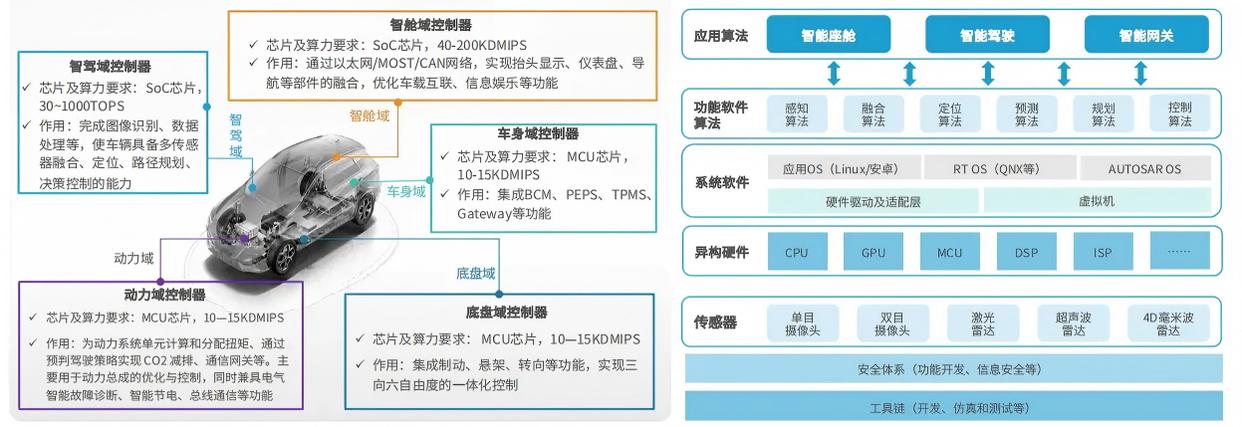

车规级 MCU 的设计始于 “需求锚定”—— 需结合应用场景(如动力域、车身域)、安全等级(ASIL-A 至 ASIL-D)、性能要求(算力、接口)等维度,定义不可妥协的核心指标。这一步是后续架构设计与模块开发的 “总纲”,直接决定芯片的成败。

1. 场景驱动的需求拆解

| 应用场景 | 核心功能需求 | 性能指标参考 | 安全等级要求 |

|---|---|---|---|

| 动力域(BMS) | 电芯电压采集、均衡控制、充放电管理 | 12bit以上 ADC、支持 CAN FD | ASIL-B/D |

| 车身域(BCM) | 灯光控制、门窗驱动、传感器信号处理 | 多IO口(≥100 个)、低功耗 | ASIL-A/B |

| 底盘域(ESP) | 轮速计算、刹车压力控制、姿态稳定 | 锁步核、1ms控制周期 | ASIL-D |

| 区域控制器 | 多协议转换、负载管理、OTA本地执行 | 集成以太网PHY、支持虚拟化 | ASIL-B/C |

不同车载场景对 MCU 的需求差异显著,需先明确芯片的定位与应用边界:

以底盘域 ESP 控制为例,其核心需求可进一步拆解为:运算单元需支持 1ms 内完成轮速融合与压力计算;通信接口需兼容 CAN FD(8Mbps 速率);安全层面需实现故障检测率≥99.9%、响应时间≤100μs。

2. 不可妥协的车规核心指标

基于场景需求,需明确以下四类硬性指标,这些指标是后续测试与认证的核心依据:

环境适应性:宽温(Grade 0 级为 - 40℃150℃)、抗振动(10g,5Hz2000Hz)、抗电磁干扰(CISPR 25 Class 3);

功能安全:ASIL 等级(如 ESP 需 ASIL-D)、故障诊断覆盖率(硬件≥90%,软件≥95%)、单点故障 metric(SPFM)≥90%(ASIL-D 级);

性能与接口:CPU 主频(Cortex-R52 核可达 600MHz)、嵌入式存储(NVM≥16MB,支持 ECC)、通信接口(CAN FD/CAN SIC、以太网 100BASE-T1/10BASE-T1S);

信息安全:支持 AES-256 加密、安全启动、硬件防篡改,满足 ISO/SAE 21434 威胁防护要求。

二、架构设计:车规级 MCU 的 “安全骨架” 搭建

架构设计是车规级 MCU 的 “灵魂”,需平衡安全性、实时性与成本,核心围绕 “计算核心冗余化、功能模块集成化、安全边界清晰化” 三大原则展开,目前主流架构采用 “锁步多核集群 + 安全岛 + 专用外设” 的组合方案。

1. 计算核心:锁步架构保障运算可靠性

车规级 MCU 的计算核心必须解决 “运算错误” 风险,Lockstep(锁步)架构是 ASIL-B 及以上等级的标配 —— 将两颗完全相同的 CPU 核心(如 Cortex-R52)并行运行,实时对比指令执行结果与输出数据,一旦出现偏差立即触发故障响应。

架构细节与工程实践:

核间同步:通过硬件同步信号(如时钟同源、复位同步)确保两颗核心的执行时序偏差≤1ns;

结果校验:在指令流水线末端设置 “比较器”,对运算结果、状态寄存器值进行逐周期比对;

故障响应:偏差发生时,立即触发本地复位(核心级)或通知安全管理单元(系统级),确保错误不扩散。

如可以采用 “Cortex-M7 + Cortex-M4” 异构锁步设计,M7 核(1GHz)负责高性能计算,M4 核(400MHz)负责实时控制与结果校验,兼顾算力与安全性。

2. 安全岛:隔离式安全管理中枢

为避免安全功能与非安全功能的相互干扰,需在架构中划分独立的 “安全岛”(Safety Island),作为全芯片的安全管控核心。安全岛需具备 “硬件隔离、权限独立、自主运行” 的特性,不受主核故障影响。

安全岛核心模块组成:

安全管理单元(SMU):统筹故障检测与响应,接收来自锁步核、外设、诊断模块的故障信号,执行分级处理(如报警、降级、关断);

加密引擎:集成 AES、RSA/ECC、SHA-2 等算法硬件加速器,支持国密算法(SM2/SM4),负责密钥存储与数据加密;

防篡改控制器:连接温度、电压、光强传感器阵列,检测物理拆解或异常访问,触发敏感数据销毁;

独立时钟与电源:采用专用 RC 振荡器与 LDO 供电,避免主系统电源 / 时钟故障导致安全岛失效。

安全岛通常采用 “硬件熔断(Fuse)+ 独立总线” 设计,安全配置参数写入 Fuse 后不可篡改,安全岛与主核间通过单向总线通信,防止主核越权访问。

3. 外设集成:满足车载场景的连接与控制需求

车规级 MCU 的外设模块需 “按需集成、冗余设计”,重点覆盖通信接口、模拟前端、控制输出三类核心外设,同时支持功能安全机制。

关键外设设计要点:

通信接口:

集成多通道 CAN FD 控制器,支持 CAN SIC 技术(降低信号反射,8Mbps 长线传输可靠);

嵌入以太网 PHY(100BASE-T1/10BASE-T1S),支持 gPTP 时间同步(微秒级对齐);

通信接口需具备 CRC 校验、超时检测、总线监控功能,符合 ISO 15765-4 标准。

模拟前端:

集成 12bit 以上 ADC(采样率≥1MSPS),支持差分输入与硬件过压保护;

配备 PGA(可编程增益放大器)与温度补偿电路,确保宽温下采样精度≤±1%。

控制输出:

提供多路 PWM 输出(支持死区控制、故障关断),用于电机驱动、阀门控制;

输出通道需具备短路保护、过流检测功能,响应时间≤10μs。

三、核心模块开发:从硬件到软件的安全落地

架构确定后,需进入模块级开发阶段 —— 硬件层面聚焦 “可靠性设计”,软件层面聚焦 “安全编码与验证”,两者协同实现芯片的安全目标。

1. 硬件模块:可靠性与安全机制双保障

硬件模块开发需解决 “故障预防、故障检测、容错运行” 三大问题,重点关注电源、时钟、存储三类核心模块。

(1)电源管理模块(PMU)

电源是芯片运行的基础,需设计多域供电与故障防护机制:

多域 LDO:核心域(VDD)、IO 域(VDDIO)、安全岛域(VDD_S)分别采用独立 LDO,输出电压精度 ±2%;

过压 / 欠压保护:每个 LDO 输出端设置比较器,阈值通过 Fuse 锁定,过压时触发钳位电路,欠压时触发预警;

掉电预警:通过电容储能检测电压下降速率(≥1V/ms),提前 50μs 生成预警,为安全岛保存关键数据预留时间。

(2)时钟管理模块(CMU)

时钟异常是导致芯片功能失效的主要原因之一,需实现全时钟域的监控与校准:

多源时钟冗余:主时钟采用车规级晶振(±20ppm),备用时钟采用 RC 振荡器,支持无缝切换(切换时间≤10μs);

频率监控:每个时钟域配备计数器,将被监控时钟与参考时钟(32kHz 晶振)比对,偏差超过 ±1% 则触发故障;

漂移校准:通过 PLL(锁相环)的频率控制寄存器,动态调整时钟频率,宽温下偏差控制在 ±0.1% 以内。

(3)存储模块(NVM/RAM)

存储模块需保障数据的完整性与持久性,同时支持安全擦写:

嵌入式 NVM:采用 NOR Flash,支持 ECC 校验(纠正 1bit 错误,检测 2bit 错误),擦写寿命≥10 万次,数据保存时间≥15 年;

安全 RAM:划分独立的安全数据区,支持奇偶校验,空闲时自动清零,防止敏感数据残留;

存储保护:通过存储保护单元(MPU)设置读写权限,非安全任务禁止访问安全存储区。

2. 软件层面:安全编码与全流程验证

车规级 MCU 的软件需 “安全优先于性能”,从编码规范、测试验证到运行时防护,构建全生命周期的安全体系。

(1)安全编码与开发流程

编码规范:严格遵循 MISRA C:2012 规范,禁止动态内存分配、隐式类型转换、汇编语言,所有变量显示初始化;

开发工具链:采用经 ISO 26262 认证的工具(如 S32 Design Studio、VectorCAST),确保工具链自身的可靠性;

版本管理:采用 Git+SVN 双备份,每版代码需关联需求文档与测试报告,支持全流程追溯。

(2)多层次测试验证

单元测试:对每个函数 / 模块进行测试,覆盖正常、异常、边界场景,ASIL-D 级要求 MC/DC 覆盖率≥90%;

故障注入测试:模拟硬件故障(如时钟停摆、电压跌落)、软件漏洞(如数组越界),验证故障检测率与响应时间;

系统级测试:搭建硬件在环(HIL)测试台,模拟车载环境(温度、电磁干扰),验证芯片与外设的协同运行。

四、测试与认证:车规级 MCU 的 “通关凭证”

没有通过车规认证的 MCU 无法进入车载供应链,测试与认证是芯片设计的 “最后一公里”,需覆盖环境可靠性、功能安全、信息安全三大维度,核心认证包括 AEC-Q100、ISO 26262、ISO/SAE 21434。

1. 环境可靠性测试(AEC-Q100)

AEC-Q100 是车规芯片的基础认证,需通过 7 大类测试,验证芯片在恶劣环境下的可靠性:

| 测试项目 | 测试条件(Grade 0级) | 合格标准 |

|---|---|---|

| 高温老化 | 150℃,1000 小时 | 无性能退化、无引脚腐蚀 |

| 温度循环 | -40℃~150℃,1000 次循环 | 焊点无裂纹、功能正常 |

| 振动测试 | 10g,5Hz~2000Hz,3 轴各 8 小时 | 封装无开裂、参数变化≤1% |

| 电磁兼容(EMC) | 辐射抗扰度200V/m,辐射发射≤40dBμV/m | 功能无中断、数据无错误 |

测试需委托第三方实验室(如 SGS、TÜV)执行,测试数据作为认证申请的核心依据。

2. 功能安全认证(ISO 26262)

ISO 26262 认证需基于 ASIL 等级开展,核心是 “安全生命周期管理” 与 “安全验证”,分为芯片级(SEooC)与系统级两个层面:

认证关键环节:

安全分析:执行 FMEA(故障模式与影响分析)、FMEDA(故障模式影响及诊断分析),明确故障模式与检测方法;

安全机制验证:通过故障注入测试,验证 Lockstep、ECC、BIST 等机制的有效性,确保故障检测率达标;

文档提交:提交安全计划、设计文档、测试报告、失效分析报告,接受认证机构(如 TÜV 莱茵)的审核。

3. 信息安全认证(ISO/SAE 21434)

随着汽车智能化升级,信息安全成为必选项,ISO/SAE 21434 认证需覆盖 “威胁防护、漏洞管理、应急响应” 全流程:

核心认证要求:

威胁分析(TARA):识别芯片面临的攻击场景(如侧信道攻击、固件篡改),评估风险等级;

防护机制验证:测试安全启动、加密引擎、防篡改功能的有效性,如通过侧信道攻击工具验证掩码技术的防护效果;

漏洞管理:建立芯片全生命周期的漏洞监测与修复流程,支持 OTA 安全更新。

五、工程落地:从原型到量产的关键挑战与应对

芯片设计完成后,需解决 “原型验证、量产良率、供应链协同” 三大工程问题,才能真正实现商业化落地。

1. 原型验证:硬件在环(HIL)测试台的搭建

原型芯片需通过 HIL 测试台模拟真实车载环境,验证功能与安全:

环境模拟:通过温度箱、振动台、EMC 模拟器复现车载工况;

外设仿真:用板卡仿真传感器(轮速、温度)、执行器(电机、阀门)的输入输出信号;

自动化测试:编写测试脚本(如 Python+CANoe),执行 10 万次以上的循环测试,捕捉偶发故障。

2. 量产良率:车规级制造与测试保障

车规级 MCU 的量产需满足 “高良率、高一致性”,制造环节需:

晶圆制造:采用车规级制程(如 16nm Auto),晶圆测试(CP)覆盖电学参数、功能测试,筛选不良品;

封装工艺:采用 QFN/LGA 封装,添加金属屏蔽层,封装后测试(FT)包含环境应力测试;

质量管控:执行 AEC-Q001(分立器件)、AEC-Q002(电源)等标准,确保器件一致性。

3. 供应链协同:与车企、Tier1 的联动

芯片厂商需与下游伙伴深度协同,确保芯片适配系统需求:

早期介入:在车企车型定义阶段参与需求讨论,明确芯片接口与安全需求;

提供参考设计:提供硬件开发板(如恩智浦 MR-VMU-RT1176)、软件栈(Zephyr、ROS2),降低 Tier1 的开发难度;

支持认证:协助车企完成系统级 ISO 26262/21434 认证,提供芯片级安全证据。

六、总结:车规级 MCU 设计的核心原则与趋势

车规级 MCU 的设计是 “安全、可靠、成本” 的平衡艺术,核心遵循三大原则:安全优先(锁步、安全岛等机制不可妥协)、场景驱动(外设与性能按需设计)、全周期管控(从需求到量产的安全验证)。

未来,随着汽车区域控制、智能驾驶的发展,车规级 MCU 将呈现三大趋势:算力升级(多核异构、NPU 集成)、安全融合(功能安全与信息安全深度协同)、接口高速化(支持 CAN-XL、5G 以太网)。掌握这些趋势与设计方法,才能在车规芯片赛道中打造出满足市场需求的产品。

-

车规级MCU缺货持续2年,上海航芯助力国产市场2023-02-03 1703

-

笙泉MCU喜获AEC-Q100认证,正式在车规赛道上奔驰2023-06-26 1279

-

高可靠、高性能车规MCU, 满足车身控制多元应用2023-09-15 1445

-

琻捷电子发布国内第一颗车规级TPMS芯片SNP70X2018-04-28 8412

-

杰发科技推出国内首颗车规级MCU芯片,助力汽车“新四化”2020-03-24 17735

-

解析车规级MCU的技术难点2021-02-16 12487

-

通过车规级认证的MCU国产公司盘点2022-09-01 2138

-

贞光科技:什么是车规级MCU?2022-10-13 2100

-

什么是车规等级芯片?一颗***想要上车有多难?2023-08-08 2489

-

一颗芯片从初步设计到实际应用落地比你想象的更难!2023-08-15 2242

-

昂瑞微电子车规级蓝牙SoC芯片OM6650AM通过车规级认证2023-09-19 2256

-

芯旺微电子KungFu内核车规级MCU累计交货突破1亿颗2024-03-19 1514

-

中微爱芯一款车规级信号链芯片和四款车规级逻辑芯片通过认证2024-04-22 2135

-

芯弦半导体高性能车规MCU系列获AEC-Q100车规级认证证书2024-04-29 1614

-

AMEYA360 | 江苏润石最新发布12颗车规级模拟芯片2024-06-19 916

全部0条评论

快来发表一下你的评论吧 !