Labview控制FPGA实现SOPC数据采集系统的设计方案

描述

引言

传统数据采集卡多采用PCI或ISA总线接口,这种方式安装麻烦、价格昂贵,且受计算机插槽数量、地址、中断资源限制,有扩展性差等缺点。而USB通用串行总线则具有安装方便、高带宽、易扩展等优点,其中USB2.0标准具有480Mbps的最高数据传输率,这使USB成为本系统所选接口的主要类型。控制方面,传统数据采集通常使用单片机或DSP作CPU来进行控制和数据处理。其中单片机的时钟频率低,无法适应高速数据采集;DSP虽能满足速度要求,但在速度提高的同时,也提高了成本。而用FPGA实现的SOPC则具有时钟频率高、内部延时小和配置灵活等优势。数据显示方面,采用虚拟仪器不但可按要求设计且变换灵活,还能执行传统仪器无法实现的许多功能。为此,本系统使用FPGA实现SOPC数据采集系统,并利用Labview实现系统的显示与控制。

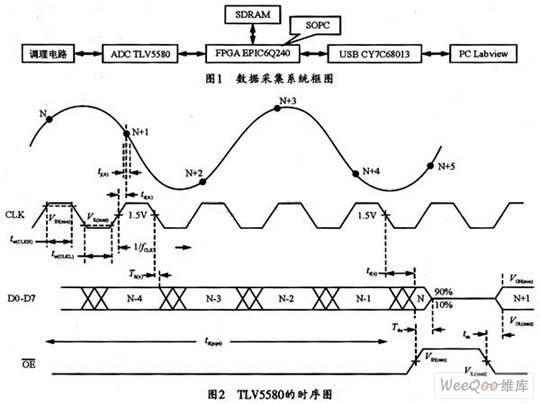

1数据采集系统总体设计

基于SOPC的高速数据采集系统总体框图如图1所示。图中,ADC(Analog t0 Digital Converter)模数转换器采用的是8位高速模数转换器TLV5580。调理电路用于实现对输入信号的限幅、限压、滤波,并用增加输入阻抗的措施来获取预期有效信号,同时保护后端AD转换芯片。FPGA采用ALTERA公司的EPIC6Q240芯片来实现ADC控制及FIFO数据缓存;基于FPGA芯片的控制系统可直接用逻辑实现,也可在其基础上实现SOPC对数据的采集、传输的控制。USB采用CYPRESS公司可支持USB2.0协议的高速芯片CY7C68013。FPGA可控制TLV5580的连续采样,并将数据送到FIFO数据缓存。当采集到一定量的数据后,CY7C68013便采用slave fifo方式将数据送给PC端,并由PC端软件Labview实现的虚拟仪器进行显示和控制等处理。

2数据采集系统硬件设计

2.1 模数转换器TLV5580及其控制

TLV5580是一款高速8位模拟/数字转换器,它具有80 Msps采样速率,是一款3.3 V工作电压的低功耗6级流水线结构高速A/D芯片。它的采样信号每1个时钟周期可通过一个STAGE,完成连续转换到数据输出共需6个时钟周期。此流水线结构由6个ADC/DAC级和一个终极快闪ADC构成。采用A/D-D/A两次变化以及纠错逻辑的目的在于进行差错校正,以保证流水线上各个阶段在满操作温度范围下,ADC的偏移量能够得到补偿且不丢失代码。TLV5580的时序图如图2所示。可以看出,该A/D转换器时序简单,容易控制。当输出使能(OE)为低电平时,一旦数据流水线满,其数据将在每一个时钟周期的上升沿输出。

2.2 USB芯片CY7C68013(FX2)

为了满足对USB传输速度较高的需要,本设计选择了Cypress公司内置USB接口的微控制器芯片EZUSBFX2。FX2系列芯片独特的结构使其数据传输速度最高可达56Mbps,故可最大限度地满足USB2.0的带宽。此外,CY7C68013提供有一个串行接口引擎(SIE),可负责大部分USB2.0协议的处理工作,从而大大减轻USB协议处理的工作量,并可提供4KB的FIFO,以保证数据高速传输的需要。CY7C68013可配置成三种不同的接口模式:Ports、GPIF Master和Slave FIFO。本项目采用Slave FIFO模式。在该模式下,外部逻辑或外部处理器直接连接到FX2的端点FIFO,因为外部逻辑可以直接控制FIFO,所以,FIFO的基本控制信号(标志、片选、使能)均由FX2的引脚引出。其外部控制可以是同步,也可以是异步,可以使用内部时钟,也可以使用外部时钟。

2.3 FPGA器件EPIC60240C6

FPGA (Field Programmable Gate Array)即现场可编程门阵列。本设计选用的是ALTERA公司的EPIC60240芯片,该芯片的工作电压为1.5 V,存储器密度可达5980个逻辑单元,它包含20个128x36位RAM块,总的RAM空间达92160位,此外还内嵌了2个锁相环电路和一个用于连接SDRAM的特定双数据率接口,故可支持多种不同的I/O标准。事实上,这里的FPGA除了可以直接编程以进行逻辑控制外,也可在此基础上构建SOPC系统,以便使用软、硬件协同方法,与SDRAM构成一个大容量的FIFO来对SDRAM以及MD转换器进行控制,同时完成与USB器件的协同工作。

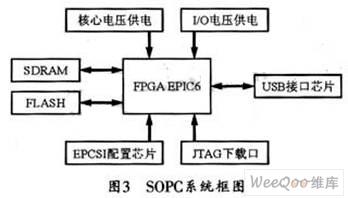

2.4 SOPC及其设计

SOPC (System on a Programmable Chip)即可编程片上系统。它可以由单个芯片完成整个系统的主要逻辑功能;这种可编程系统具有灵活的设计方式,而且可裁减、可扩充、可升级。本设计采用ALTERA公司率先推出的SOPC解决方案,来将处理器、存储、I/O口等系统所需集成到一个FPGA器件上,并对其进行软、硬件配置,从而实现对数据的采集、传输、显示控制。图3所示是其SOPC系统框图。

3数据采集系统软件设计

本系统软件包括SOPC系统程序、USB固件程序、驱动程序和应用程序等4个方面的设计。其中SOPC系统程序和USB固件程序是整个程序设计的核心。

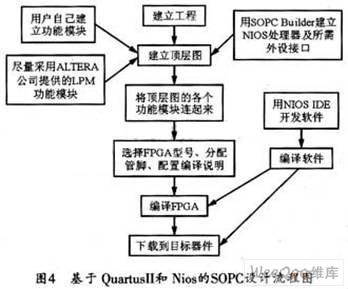

3.1 SOPC系统程序设计

基于QuartusII和Nios的SOPC设计流程如图4所示。

本系统中的SOPC系统软件设计是指在FPGA中配置ALTERA公司NiosII嵌入式处理器的硬件环境。其中NiosII处理器的配置可基于QuartusII,它是ALTERA公司的大规模FPGA/CPLD开发工具。为了进行Nios处理器的开发,通常要在Quartus里装入NiosII的软硬件开发工具,同时在提供的开发包中使用软件SOPC Builder开发工具加载NiosII核和外围接口,并定义相应的指令,然后对系统进行综合后,再下载到FPGA中,就可以完成特定功能的处理器设计。

3.2 USB固件程序设计

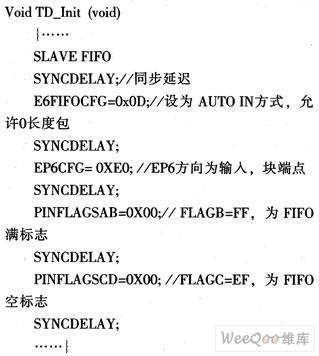

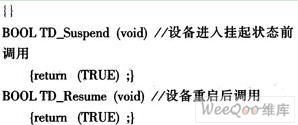

CY68013芯片的固件程序主要负责处理PC机发来的各种USB设备请求,并与外围电路进行数据传输。CYPRESS公司提供的固件程序框架中的两个程序分别是FW.C和PERIPH.C。其中FW.C是固件运行的主程序文件,负责处理各种USB设备请求,包含程序框架的MAIN函数,它可管理整个51内核的运行。而对于PERIPH.C,则必须将PERIPH.C实例化,以实现所需的功能。固件程序中最重要的是TD_init()和TD_poll()两个函数。TD_Init函数负责对CY7C68013的初始化,它一般在固件运行开始时调用;TD_poll函数是数据采集的执行子程序,它首先判断内部端点6的缓冲区和外部FIFO缓冲器是否非空,如满足条件,则启动A/D转换,并根据USB设备工作在高速和全速的不同来设置不同的传输计数。本设计中将接收数据端点6设为SLAVE FIFO模式,并使用AUTO IN模式来接收FPGA发来的数据,数据流由外部FIFO控制器控制,并直接传人端点6的FIFO,以等待主机提取。这里,CY7C68013仅作为数据通道,CPU不参与此过程。因此,只需在固件的初始化程序中配置好端点6的SLAVE FIFO接口模式,剩下的传输控制和其它的工作则可由FPGA来完成。以下是针对本设计的部分固件程序:

Void TD_Poll(void)//在设备运行时反复被调用,主要完成外部FIFO状态检测和数据传输

3.3 USB驱动程序设计

Windows下的USB驱动程序通常由3部分组成:USB设备驱动程序、USB总线驱动程序和USB主控制器驱动程序。其中,Windows操作系统已经提供了处于驱动程序栈底的USB总线驱动程序和USB主控制器驱动程序。而USB设备驱动程序则要由设备开发者编写。它应能通过向USB总线驱动程序发送包含URB(USB Request Block)的IRP(I/O Request Packet)来实现USB外设之间的信息交换。本设计采用Jungo公司的Win Driver进行驱动程序开发,并根据Win Driver提供的驱动向导和用户需要,来自动生成代码框架,从而简化驱动程序的开发。

3.4应用程序设计

本设计采用NI公司的虚拟仪器(VI)开发平台Labview来进行应用程序的设计。VI包括三部分:前面板、框图程序和图标/连接器。其中前面板用于设置输入数值和观察输出量。每一个前面板都对应着一段框图程序。框图程序可用Labview图形编程语言—G语言来编写。图标/连接器是子VI可被其它Ⅵ调用的接口。图标是子VI在其它程序框图中被调用的节点表现形式;而连接器则是节点数据的输入/输出口。连接器端口与前面板的控制和显示一一对应。

4结束语

本文介绍了一种基于SOPC和USB2.0接口的高速数据采集系统及其虚拟仪器的设计方法。实验表明,基于本设计的高速数据采集系统具有抗干扰、可靠性高、失码率低等优点。

-

基于ARM和FPGA的微加速度计数据采集设计方案2020-11-25 2054

-

如何使用FPGA实现ADC采集系统的设计2020-08-21 2768

-

基于FPGA的高速数据采集系统该怎么设计?2019-09-05 2365

-

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究2019-07-09 2975

-

一种基于SOPC和USB2.0接口的高速数据采集系统及虚拟仪器设计2019-07-05 2015

-

多路模拟数据采集接口设计2018-09-21 2841

-

研华数据采集/控制卡+LabVIEW ——便捷的量测与控制系统解决方案2018-04-28 2639

-

基于SOPC技术的数据采集系统设计2016-02-17 1186

-

基于SOPC数据采集与控制系统2012-07-16 762

-

基于SOPC数据采集与控制系统的设计2012-07-12 891

-

基于SOPC的数据采集与处理系统设计2012-05-23 2211

-

SOPC基础上的数据采集系统设计2011-07-04 1479

-

基于SOPC的高速数据采集系统研究与设计2010-07-17 628

-

基于LABVIEW与DSP串口的数据采集系统2009-07-31 1722

全部0条评论

快来发表一下你的评论吧 !