利用ATmega48芯片和CMX865芯片实现串口转FSK的通信模块设计

描述

随着信息技术与网络技术的飞速发展,信息交互应用业务给人类生活带来更多的便利,信息终端表现出巨大的市场潜力。但是由于终端用户环境不同,用户信息交互方式可能不同,目前常用的有IP方式、FSK方式以及无线通信方式等。为了能够提高终端市场竞争力,减少系统开发成本投入,通信模块与终端程序独立设计是较为理想的解决方案。本文采用ATmega48芯片及CMX865芯片实现FSK通信模块,基于此模块,用户与业务平台之间进行FSK信息交互,相对于终端来说就是简单的串口通信。

1 ATmega48介绍

ATmega48是基于AVR增强型RISC(精简指令集)结构的高性能、低功耗的8位CMOS微控制器。微控制器具有可控制的上电复位和可编程的掉电检测电路、经过标定的片内RC振荡器、片内外18个中断源和5种休眠模式。由于其先进的指令集以及单时钟周期指令执行时间,ATmega48的数据吞吐率高达1 MIPs/MHz,运行速度比普通的单片机高出10倍,从而可以缓解系统在功耗和处理速度之间的矛盾。

其片内集成了4 KB的系统内可编程Flash、256字节的EEPROM、512字节的SRAM.其外设具有可编程的串行USART接口、可工作于主机/从机模式的SPI串行接口;存在2个具有独立预分频器和比较器功能的8位定时/计数器和1个具有预分频器、比较功能和捕捉功能的16位定时/计数器、具有独立片内振荡器的可编程看门狗定时器等。ATmega48/88/168芯片硬件电路可以完全兼容,完全可以根据软件实际需求灵活选择AVR芯片,极大地方便系统的开发与研制。

2 CMX865简介

CMX865是CML公司新出的一款DTMF编/解码器/FSK调制解调器复合IC芯片,它采用单个高速串行总线控制,与大多数串行接口兼容。 CMX865的主要特征是:

◆供电电压2.7~5.5 V,低功耗操作模式;

◆支持V.23、Bell202 FSK 1200 bps编码/解码;

◆集成高可靠性DTMF、编码器/解码器;

◆集成振铃检测功能,支持语音探测功能。

3 硬件设计

图1为串口转FSK通信模块电路。系统主要以AVR单片机ATmega48芯片和CMX865调制/解调芯片为硬件架构,ATmega48芯片利用C-BUS总线对CMX865芯片进行控制操作,实现FSK通信。CMX865芯片的IRQN终端与CPU芯片的外部中断0(INT0)相连,确保软件可以采用中断方式接收/发送FSK数据。CMX865芯片的时钟信号、片选信号、响应应答数据信号、接收控制数据信号分别与ATmega48芯片的普通I/O接口引脚相连,CPU可以通过模拟口线方式对CMX865芯片进行控制。

图1还提供了基本的FSK接收/发送数据接口电路和振铃检测电路。在FSK发送电路中,CMX865芯片TXA(15引脚)处外接电阻的目的是匹配芯片接口对线路的交流阻抗。在FSK接收电路中,CMX865芯片RXAFB(9引脚)与RXAN(10引脚)之间的电容以及隔离变压器之间电容设计的目的是滤除高频噪声;通过调节接收电路中两个电阻R1、R2的阻值即可改变接收端提供给CMX865芯片信号的幅度。在振铃检测电路中,IC1是光电耦合器,不振铃时光电三极管截止,RING为高电平;振铃时,振铃信号经过电容耦合及稳压管稳压,振铃电压使IC1内发光二极管发光,照射到光电三极管的基极上导致光电三极管导通,RING为低电平,通过ATmega48引脚检测到低电平的振铃信号。

4 软件实现

ATmega48芯片具有4 KB内部Flash和512字节的片内SRAM,软件实现需考虑资源分配问题,特别是SRAM使用情况。由于程序涉及串口通信、DTMF通信和FSK通信3种情况,理论上需要开辟6个缓冲区。如果这样,每一个缓冲区的大小显然不能确保达到实际通信数据量的需求。结合FSK通信特点,DTMF数据传输与FSK数据传输不可能同时发生,因此FSK与DTMF可共用相同缓冲区。同样串口接收与FSK发送、串口发送与

FSK接收都不会同时发生,这样通信只需要开辟两个缓冲区就可以确保模块正常通信,考虑实际业务平台数据量情况,软件设计中为FSK接收开辟255字节缓冲区复用;FSK发送开辟45字节缓冲区复用。

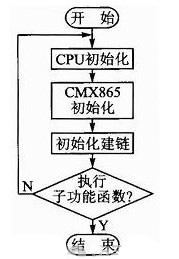

4.1 主程序实现流程

通信模块主程序包括:CPU初始化、CMX865初始化、初始化建链、串口通信和FSK通信子程序等。主程序流程如图2所示。初始化建链环节是模块正常工作的基础,通过初始化建链操作,信息终端可以根据线路环境以及平台超时机制对通信模块参数进行设置,确保通信的稳定性。通信主流程循环执行3个子功能函数:线路状态处理函数、串口数据解析与处理函数、链路保持函数。线路状态处理函数设计了3种线路状态,即初始状态、空闲状态和摘机状态;正常工作时仅在空闲状态和摘机状态之间切换。其中在空闲状态检测振铃、根据状态位执行摘机、DTMF拨号等操作;在摘机状态根据状态位执行FSK收发、脱线检测、挂机控制等操作。串口数据解析与处理函数包含串口数据按命令集解析、对解析命令进行应答和状态置位处理部分。这样线路状态处理函数和串口数据解析与处理函数通过状态置位标志紧密连接起来。FSK数据采用中断方式直接接收,接收完毕后在摘机状态下直接通过串口发送给信息终端。由于串口发送应用相对单一,为简单处理串口发送采用即时应答处理方式,分散在通信主流程各子功能函数中实现,提高了通信效率。通过链路保持函数判断串口通信是否异常,通信模块周期性地向信息终端发送链路保持命令,如果3次重发均未收到终端应答命令,通信模块将自动锁闭线路,重新执行初始化建链操作,实现串口异常的处理。

图2 主程序流程图

4.2 对外串口通信协议

模块采用标准串口通信,波特率为19 200 bps,10位异步方式。定义串口通信数据包格式为:0x1E+命令+校验和反码(对命令的校验和反码),其中部分命令以变长方式发送。串口通信主要命令有:模块初始化、链路保持、DTMF接收/发送、FSK接收/发送、振铃、挂机等,命令具体格式和描述此处不加详述。模块初始化上电后由通信模块自动发起,直到正确接收到终端应答初始化命令后,通信模块才建链成功。信息终端初始化应答命令主要提供FSK通信模块参数配置信息。上电后如果FSK模块未收到终端初始化应答信息,则周期性地(每2 s)发送一次初始化建链命令,直到成功为止;模块FSK通信过程中周期性地向终端发送链路保持命令,如果未收到终端应答信息,则断开FSK链接重新开始模块初始化。

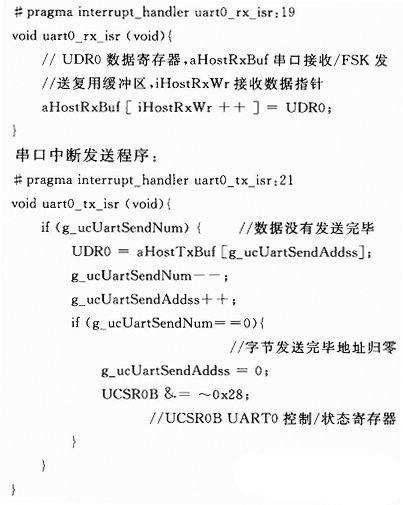

4.3 串口通信实现

AVR单片机串口通信往往采用SPI通信方式,通信模块串口通信采用UART0控制/状态寄存器和数据寄存器实现。串口通信子程序主要由串口发送/接收中断子程序、串口接收命令解析子程序和串口组包发送子程序3部分组成。其中串口中断接收程序为:

具体执行串口数据发送时,需要提供发送数据长度、发送起始地址、置UCSROB寄存器值(UCSR0B |=0x28)。串口接收命令解析子程序按照对外串口通信协议解析串口命令,并根据命令描述调用子程序代码执行相应子功能操作。为了通信容错处理,通信模块需对接收串口数据进行校验,如果解析的串口命令格式正确,则向终端发送肯定应答;否则发送否定应答,等待终端重传命令数据。串口组包发送子程序对接收的FSK数据以及线路状态等信息数据,按照串口通信协议组包发送给信息终端。

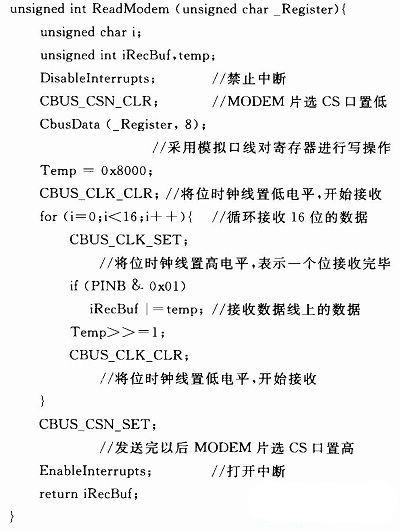

4.4 FSK通信实现

FSK通信子程序主要由CMX865芯片寄存器操作、FSK收/发、DTMF收/发以及线路状态检测等子程序组成。ATmega48芯片采用模拟口线的方式对CMX865寄存器进行读/写操作,其中对CMX865芯片寄存器读操作程序为:

FSK收/发、DTMF收/发子程序均以CMX865寄存器读/写操作函数为基础,通过设置CMX865寄存器的值,确定其工作模式。FSK数据发送、接收都可以通过CMX865芯片的IRQ中断口线引起ATmega48芯片中断,因此FSK数据收/发都通过中断实现。芯片程序采用10 ms定时器循环检测线路状态。

结语

本文利用ATmega48芯片和CMX865芯片为硬件架构设计了串口转FSK通信模块。由于ATmega48芯片与ATmega88芯片除了Flash、EEPROM、SR AM容量差异外,性能完全相同。通信模块可以不更改硬件电路,仅配置相应AVR芯片,对软件稍作调整,能够满足通信业务对通信数据量增加的需求,节约模块二次开发的成本。目前本通信模块已在一款新型的电子交易终端上使用,并与中兴、精伦等电子交易平台进行信息交互,运行效果良好。

-

基于AVR单片机的串口转FSK的通信模块设计2014-06-23 2282

-

atmega48的调试问题2012-03-31 3072

-

AVR 单片机的串口模块设计教程2012-07-11 2792

-

aTmega48怎么做电池电量检测2013-08-05 4417

-

8位微控制器ATMEGA48资料推荐2021-03-26 1561

-

如何利用ATmega48单片机实现交通灯系统的设计?2022-01-24 660

-

ATmega48中文资料,ATmega48中文数据手册2008-04-08 4052

-

atmega48/atmega88/atmega168 pd2008-06-05 1411

-

基于ATmega48的3相无刷电机的控制方法2010-12-21 1490

-

AVR单片机的串口转FSK的通信模块设计2012-11-26 3983

-

基于Atmega48和CC1100模块的无线通信功能的实现2016-01-25 874

-

基于Atmega48和 CC1100模块的无线通信功能的实现2017-08-31 889

-

atmega48单片机特性 atmega48的低功耗设计2018-03-26 8948

-

如何使用ATmega48单片机进行微功耗电刺激器的设计2018-11-14 1757

-

ATmega48和ATmega88及ATmega168微控制器的数据手册免费下载2021-03-25 1498

全部0条评论

快来发表一下你的评论吧 !