采用FPGA芯片的慢门限恒虚警处理电路设计及波形仿真分析

描述

慢门限恒虚警处理是一种对接收机内部噪声电平进行恒虚警处理的电路,内部噪声随着温度、电源等因素的改变而改变,这种变化是缓慢的,所以针对内部噪声的处理称为慢门限恒虚警处理。通过对雷达信号的慢门限处理降低了虚警概率,为后处理提供了必要条件。

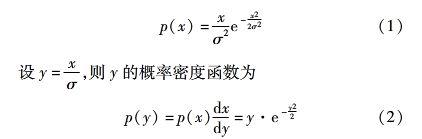

利用大规模可编程电路来实现慢门限恒虚警处理,具有方便、可靠的特点,可以方便地修改和仿真。雷达工作期,接收机输出除噪声外还有信号和地物杂波等,所以对噪声的采样应在休止期进行。接收机检测器后噪声电压的概率密度函数服从瑞利分布

由式(2)可得出,P(y)与σ无关,如果能将变量x归一化为变量y,则噪声强度σ变化时将保持输出恒虚警;恒虚警处理装置就是设法检测出噪声x的均方差σ值,再算出值;这个过程称为归一化,归一化的结果就达到了恒虚警的目的。

用数字电路实现除法运算比较复杂,故采用取对数的方法,将除法运算转化为减法运算,简化了电路实现

1 工作原理

在休止期对噪声值lgx采样,得到lgσ。取雷达工作期的lgx减去lgσ,算出lgy式(3),完成了归一化处理。设计中慢门限恒虚警处理电路是采用开环式噪声电平恒定电路,省略了反对数电路,增加了部分检测电路,原理如图1所示。

2 FPGA设计

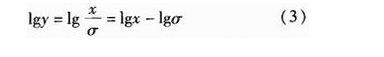

在休止期选8位I/Q信号幅度值进行累加,并对累加值进行锁存,当累加128个单元后,取出平均值并锁存作为第一门限值。在工作期选取8位I/Q信号幅度值一方面与噪声平均值比较,另一方面减去噪声平均值再与人工门限比较,如果两次比较都为大于,则输出1 bit过门限信号。人工门限值的选定要根据虚警率确定,如果虚警点多则调高门限值,反之降低门限,保持一定的虚警点数。

电路总框图如图2所示,包括3个子模块分别为时序产生模块、求噪声平均值模块、减法运算及比较模块,虚框表示FPGA芯片外围电路。

设计遵从了流水线和模块化设计原则,把总模块划分为几个功能独立又相互联系的子模块;上一个模块的输出即为下一个模块的输入,由最后一个模块完成最终结果的输出。

各子模块电路设计完成后,建立相应电路符号,在原理图输入方式下,将各单元电路符号按原理框图逻辑关系连接,通过保存、编译,再进行项目处理包括器件选择、引脚定义,确认正确无误后便完成了FPCA内部电路的设计,将设计项目下载至芯片,嵌入板级电路与其它器件配合使用,完成电路功能。

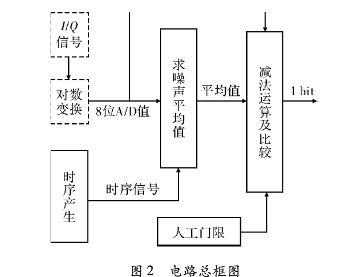

2.1 时序产生模块

利用10 MHz时钟产生τ脉冲RM;在休止期128 τ处产生平均值打入脉冲RM128和清除脉冲RST128。原理图如图3所示。

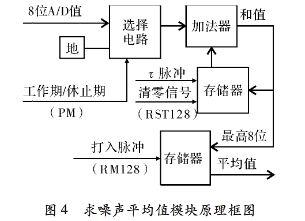

2.2 求噪声平均值模块

当休止期时,选8位I/Q信号幅度值进行累加,并对累加值进行锁存,当累加128个单元后取出平均值用RM128打入存储器锁存输出作为第一门限值,然后清除脉冲RST128清除累加值。取平均值方法:128个单元8位I/Q信号幅度值累加最大能达到15位数,平均值即为高8位值,所以取累加值的高8位作为平均值即可,原理如图4所示。

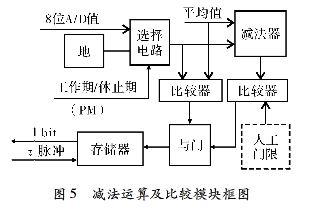

2.3 减法运算及比较模块

在工作期选取8位I/Q信号幅度值一方面与噪声平均值比较,另一方面减去噪声平均值再与人工门限比较,如果两次比较都为大于,则输出 1 bit过门限信号。原理图如图5所示。

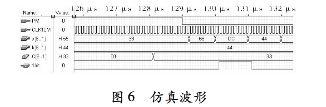

3 仿真

慢门限恒虚警处理电路仿真波形如图6所示。PM=‘1’时为休止期,PM=‘0’时为工作期;为使仿真波形更直观、易理解,休止期恒取8位I/Q信号幅度值X[8..1]=“33”,128单元后送出平均值C[8..1]=“33”;人工门限为恒定门限,此处设为K[8..1]=“44”;在工作期,当X[8..1]=“66”和“44”时,66-33<44、44-33<44故1 bit=‘0’,当X[8..1]=“DC”时,DC>33,DC-33>44连续通过两道门限故1 bit=‘1’。

4 结束语

以上是在MaxplusⅡ环境中设计、编译、仿真。一般为减少积累单元数和存储计数设备,采用降低第一门限以达到高虚警率,而后面采用较高的人工门限以保证工作时的低虚警概率。该慢门限恒虚警处理电路的设计成功,为设计此类型电路提供了借鉴。采用8位二进制值累加128次,取高8位作为平均值的方法,使得电路易于实现,该方法简单、可靠。

-

如何使用FPGA实现激光雷达恒虚警率控制技术研究说明2021-03-11 1052

-

基于ADSP-TS201处理器实现雷达恒虚警的软硬件设计和系统仿真分析2020-05-07 2097

-

基于数字技术实现闭环式噪声电平恒定电路的设计2020-04-29 3755

-

电路精选:怎么分析虚断与虚短运放电路2019-03-27 4379

-

saber仿真软件波形如何处理分析、saber仿真软件如何画电路图2017-12-08 26185

-

激光信号处理器的检测和虚警概率分析2017-01-19 758

-

基于频谱分析恒虚警技术的脉冲多普勒引信2016-12-24 857

-

基于ADSP-TS201的着陆雷达恒虚警电路实现2012-11-26 987

-

一种基于FPGA的慢门限恒虚警处理电路设计2012-05-29 776

-

噪声恒虚警处理电路的计算机仿真2009-11-21 1391

全部0条评论

快来发表一下你的评论吧 !