基于Python软硬件协同设计方法,仿真和校验的流程介绍

描述

引言

现代系统设计许多都是由C/C++,Python等高级语言来完成,而且这些系统越来越复杂,涉及到的算法的运算量也越来越大,许多算法需要用硬件实现来满足算法的实时性要求.FPGA是一种可编程的逻辑器件,它具有便于修改,调试,并能并行地完成大量的运算,从而提高算法的实时性,并且随着硬件制造水平不断地提高,FPGA的资源越来越大,工作频率也越来越高,使得能在其上面完成的算法也越来越复杂.但是传统的软硬件分开设计的方法由于软硬件设计者采用不同的设计语言,存在软硬件设计者之间难以沟通导致设计周期长等问题,这种设计方法已不能满足快速地增长的市场要求,如何将这些系统设计中的算法快速转换为相应的硬件来实现,需要新的软硬件协同设计方法.当前基于C/C++的软硬件协同设计,有一个SystemC 标准化组织一直致力于这个工作,也有少量商业化工具例如Syn-opsys 公司Synphony C Compiler 和Calypto Design Sys-tems 公司的Catapult SL Synthesis 可以将C/C++算法转换为相应的硬件.Python是一种简单易学并且功能强大的编程语言,有许多算法是由Python来实现,而且这些算法很多是免费.开源的,和C/C++类似需要如何完成基于Python的软硬件协同设计.

1 基于Python 的软硬件协同设计发展

由于Python的强大的软硬件描述能力,近年来许多研究者在Python的软硬件协同设计方面进行了许多研究,其中Logaras E 提出了一种称为SysPy(System Py-thon)可以使用Python 来描述硬件并将其自动转换为VHDL,Zhang mi采用PDSDL(Dynamic System Descrip-tion Language)来进行系统建模和校验并可将系统转换为Verilog的硬件描述,特别是Decaluwe J提出一种称为MyHDL 的Python 扩展包来进行软硬件协同设计,Villar J I采用MyHDL 完成了一个接口设计实例.这些开发工具各自具有自己的一些特点,但是他们有一点是相同,就是采用Python来进行软硬件协同设计.下面以MyHDL为例介绍基于Python的软硬件协同设计.

2 基于Python 的MyHDL 包简介

MyHDL采用Python扩展包的形式使其能支持硬件设计和仿真并在仿真结果符合要求后可将软件算法自动转换为相应的采用Verilog 或VHDL 硬件描述,由于MyHDL包是基于Python的硬件扩展,下面主要对MyH-DL硬件方面的一些主要特点做简要介绍.

2.1 数据类型

标准Python的int类型已经具有许多硬件设计所需要特征,但是在硬件设计中由于包含许多位操作和处理,MyHDL设计了intbv类,提供索引和切片操作来支持位的操作和处理.

2.2 模块,端口和信号

在MyHDL采用函数来对硬件的模块进行建模,My-HDL也有信号对象,类似于VHDL语言的信号,采用信号作为函数的参数来定义模块的端口.

2.3 发生器

发生器是MyHDL 的一个关键概念,用来建立并发性模型,对应于Verilog的always块或者VHDL的进程.

2.4 自动转换

在一定限制条件下,MyHDL使用toVerilog()或者toVHDL()函数将MyHDL设计自动转换为相应的Veril-og或者VHDL代码,如果符合MyHDL可综合子集的要求,就可使用MyHDL完成可硬件综和的代码并在FPGA上实现.

2.5 仿真

MyHDL通过Cosimulation对象使其能支持仿真,对于自动转换的Verilog 代码或者VHDL 代码,MyHDL 还可作为硬件校验语言来对转换后的Verilog或VHDL进行协同仿真和校验.

3 采用MyHDL 的硬件设计优点

Verilog和VHDL是当前的主流硬件设计语言,但是使用基于Python的MyHDL作为硬件设计也具有许多优点使得其可以作为设计者特别是硬件设计的初学者另外一种较好的选择.

3.1 MyHDL使用成本低

MyHDL是免费的并且开源,在使用MyHDL设计的工具链中同样可以使用大量的免费工具比如ICArus,IVERILOG仿真工具,GTKWAVE查看仿真波形,从而可以减少设计成本.

3.2 在硬件设计中使用先进的软件开发技术

由于Python本身是一种软件开发语言,现代软件开发的先进方法比如快速应用开发,测试驱动开发都在Python上得以体现,由于硬件描述语言的硬件设计和软件开发具有一定的相似性,采用MyHDL可以使用最新的软件开发技术.

3.3 软硬件设计可以采用同样的开发环境

Python是算法实现的一种理想的语言,很多算法都由Python实现,通常算法的软硬件实现由不同工程师来实现,软件工程师使用Python,硬件工程师使用通用的硬件描述语言,例如Verilog或VHDL,硬件工程师和软件工程师之间存在一条鸿沟,而采用MyHDL,就可以在同一个Python环境实现算法设计,仿真和校验.

3.4 其他优点

对于没有一定硬件设计经验的设计者,通常采用Verilog 设计会混淆阻塞和非阻塞赋值,不清楚Verilog的符号运算,采用VHDL进行设计又不理解VHDL的信号概念,会觉得VHDL的类型和位宽转换很繁琐,但是如果采用基于Python 的MyHDL 包作为设计语言,这些都将不成为问题.

4 基于Python 的软硬件设计流程

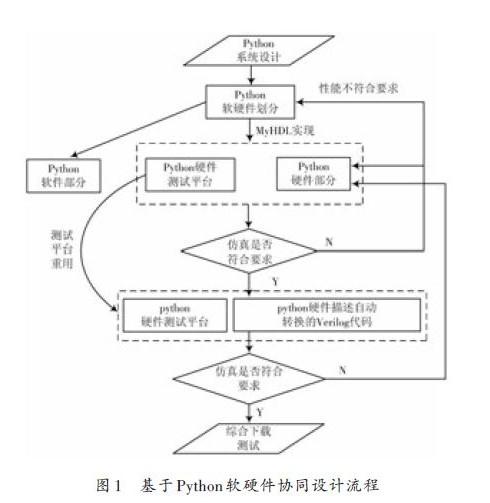

在现代系统设计中,软件工程师采用Python等高级语言,而硬件系统设计多采用Verilog,VHDL硬件描述语言,在如何将Python描述的软件映射为相应的硬件上,软硬件开发者之间的交流存在一道天然的鸿沟,而采用Py-thon来进行软硬件协同设计就可以解决这一个问题,基于Python的软硬件协同设计的流程如图1所示.

首先采用Python进行系统设计,然后根据系统性能要求进行软硬件划分,对于系统性能要求比较高的部分采用Python的MyHDL扩展包的形式来由硬件实现,同时采用Python来编写硬件测试平台.测试仿真如果不符合系统设计要求可以重新进行软硬件划分,如果测试仿真结果不正确,可重新修改.仿真通过后可以用MyHDL扩展包自动将Python转换为Verilog代码,这时的Python测试平台无需修改还可以与转换后的Verilog代码一起进行混合仿真,如果仿真通过就可以进行硬件的综合,下载,测试阶段,这与传统的硬件设计过程相同.

5 结语

从上面分析可以看出基于Python的MyHDL既是一种软硬件协同设计方法,同时其也是Python的扩展包,使得整个开发过程仅使用一种Python语言,并可以很方便地将一个软件算法快速地转换为其相应的硬件实现,从而完成一个软硬件系统设计.由于Python目前的可综合子集的限制和其本身还处在发展阶段,基于Python的软硬件设计还主要用于系统的建模方面,将其用于芯片设计的应用还不是很多,有研究者比较过MyHDL与传统硬件设计语言的实现,对于小规模的应用优势不是很明显.但是随着现代系统的算法越来越复杂性,系统规模也不断增大,相对于传统的软硬件设计方法采用Python来进行软硬件协同设计的优势就会体现出来,系统设计.仿真.校验的速度会大大提高,采用Python进行系统设计的产品能更快地进入市场.随着基于Python系统设计方法和工具的发展,基于Python的软硬件协同设计方法将会有广泛的应用前景.

-

基于FPGA的软硬件协同仿真加速技术2014-03-25 6035

-

基于SoPC的状态监测装置的嵌入式软硬件协同设计2013-01-22 3504

-

基于Altera FPGA的软硬件协同仿真方法介绍2019-07-04 2874

-

如何去实现一种基于SoPC的软硬件协同设计呢2021-12-24 1896

-

基于EDA 的嵌入式系统软硬件划分方法2009-12-05 720

-

基于SOC的USB主设备的软硬件协同验证2009-12-14 656

-

基于软硬件协同设计的低功耗生理信号处理ASIC设计2010-06-19 669

-

面向HDTV应用的音频解码软硬件协同设计2010-07-02 839

-

FPGA-SoPC软硬件协同设计2011-05-09 1082

-

可测性DSP软硬件协同仿真验证平台设计2011-06-09 1176

-

嵌入式软硬件协同设计在气象主采集器中研究2011-08-04 990

-

利用FPGA软硬件协同系统验证SoC系统的过程和方法2017-11-17 5181

-

基于FPGA的软硬件协同测试设计影响因素分析与设计实现2017-11-18 2307

-

软硬件协同设计机遇与挑战分析2017-11-25 958

-

软硬件协同设计是系统芯片的基础设计方法学2022-08-12 4282

全部0条评论

快来发表一下你的评论吧 !