利用CPLD器件实现多开关的SSPC组共享控制芯片的设计

描述

SSPC(固态功率控制器)是由半导体器件构成的智能开关装置,用于接通/断开电路,实现电路保护和接收上级计算机的控制信号并向上位机实时反馈其状态信息。由于控制逻辑完全由CPLD内部的硬件电路完成,因此与功率器件一起工作时,具有很好的电磁兼容性和抗干扰能力。研制多开关的SSPC组共享大规模控制芯片,具有相当大的工程实用价值,尤其适用于空间有限的场合,如飞机上。

本文充分利用CPLD的特点,设计了具有集成度高、速度快、抗干扰能力强和可靠性高等优点的28V直流SSPC。在一块电路板上集成多个SSPC,各个功率开关问相互独立工作,进一步提高了功率密度。

1 功能定义

28V直流SSPC应该具有以下功能:

(1) 接收上位机的控制信号。该控制信号能够兼容TTL/CMOS电平,且高电平表示导通,低电平表示关断;

(2) 根据流过的SSPC的电流逻辑分析出自身的状态,并根据表1中的代码表示上传给上位机;

(3) SSPC能够实时诊断自身故障,并根据故障的严重程度不同,采取不同的保护措施。

2 总体方案设计

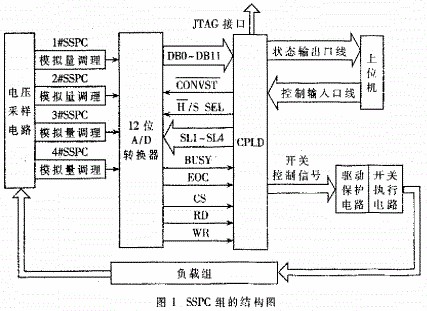

28V直流SSPC组的结构如图1所示。

每路SSPC的取样电阻上的电压经过调理电路和低通滤波以后,送到4通道的A/D转换器的模拟输入端,A/D转换器的数据输出端、状态信号和控制信号分别接到CPLD的I/O引脚,便于程序控制A/D转换器的动作。CPLD另外的I/O口可以配置为MOSFET的动作命令输出口线、SSPC的状态输出口线和与上位机相连的控制命令输入口线;CPLD自身提供的JTAG BST电路,可以方便地测试系统内部测试器件之间的连接和检验器件的操作。

由CPLD组成的逻辑判断电路的主要功能有:

(1) 将A/D转换得到的数据通过逻辑判断,综合出SSPC的工作状态并向上位机输出;

(2) 接收上位机的控制命令,结合自身的工作状态,综合得出SSPC的通断信号,控制MOSFET的开通和关断。

3 硬件设计

(1) 关键器件选型

电力MOSFET选用IR公司的IRF540N,它的漏-源最大耐压为IOOV,导通阻抗44mΩ,允许通过的最大电流33A。其最大优点为纳秒级的开通和关断时间,能够完全满足设计需要。

逻辑控制芯片采用ALTERA公司的flex6000系列。该系列采用的OptiFLEX结构增加了器件的有效面积,可用门的数目达8 000~24 000门,触发器丰富且基于LUT(查找表)结构,能够满足系统处理数据的需要。其待机状态的电流小于1mA的低功耗模式,具有强功能的I/O引脚和灵活的内部连接等优点,从而使其成为设计首选。

(2) 硬件电路的组成

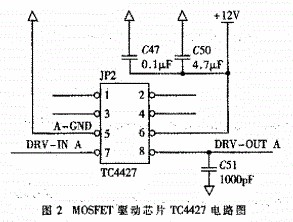

①电力MOSFET驱动和保护电路:采用专门的驱动芯片TC4427,12V供电,如图2所示。为了抑制电压和电流的瞬变,MOSFET保护电路采用RCD吸收电路,用以减小器件的开关损耗。

②取样电路:利用取样电阻(一般选用康铜丝),将流过负载的电流信号转化成可测的电压信号,经过隔离放大器、整流电路、滤波电路、采样保持器和A/D转换电路,将数字信号传送到CPLD进行逻辑分析。

③信号采集和调理电路:通过隔离放大器,将取样电阻的电压调节到A/D转换器的允许范围内,经过R-C低通滤波器滤除噪声信号后,送到A/D转换器的输入端。

④A/D转换电路:采用12位的四通道A/D转换器AD7864,与CPLD的接口主要有:a.数据输出线:与CPLD的I/O口相连;b.控制线:转换启动信号(CONVST)、片选信号(CS)、通道选择信号(H/S SEL和SL1~SL4)以及读写控制信号(RD/WR)等;c.状态线:BUSY信号和转换结束标志(EOC)等。

⑤隔离电路:CPLD为3V I/O供电和2.5V内核供电,因此采集的SSPC状态信号和接收的电力MOSFET控制信号都需要经过电平转换及电气隔离,但实际上要采用光耦隔离的方式进行。因为MOSFET的控制信号需要较大的驱动电流,如果直接从CPLD输出来驱动,会因CPLD电流太小而无法驱动,所以实际中采用六通道反相器74LF04来做光耦前一级的驱动;接收上位机输出的控制信号是从光耦输出来的,其电流一般不大(Ie<5mA),所以可以直接接在CPLD的I/O口上。

4 软件功能设计

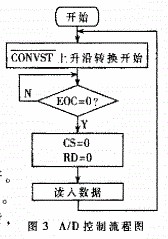

(1) 控制AD7864的动作,从数据口读出转换的结果。

运用状态机的设计方法,AD7864的动作可大致分为3个步骤区间,每个步骤对应一个状态,每个状态赋予CPLD特定的功能。

①在步骤S0(CS=1、WR=1、RD=1)时,A/D转换之中;

②在步骤S1(CS=0、WR=1、RD=1)时,监控EOC信号是否由高电平变为低电平,即

A/D转换是否结束;

③在步骤S2(CS=0、WR=1、RD=0)时,从DB0~DB11读取转换的结果。

软件流程如图3所示。

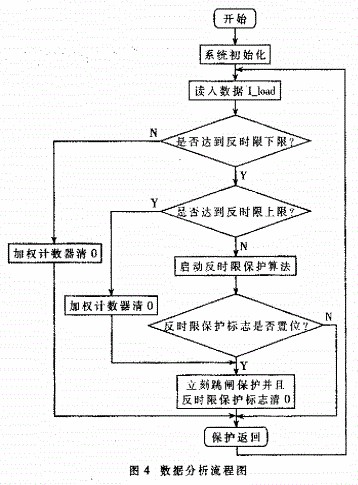

(2) 对采集的数据进行分析。

数据分析流程如图4所示。

①当电流在额定范围内时,SSPC正常工作;

②当电流大于额定电流,而小于额定电流的800%时,SSPC进入反时限保护;

③当电流大于额定电流的800%时,SSPC立刻跳闸。

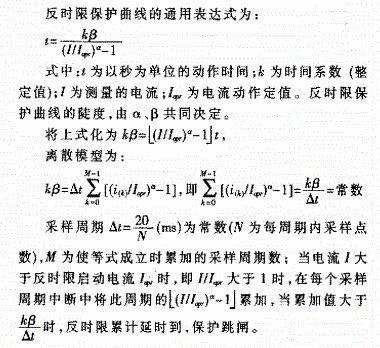

下面介绍SSPC的反时限保护阶段的算法推导。

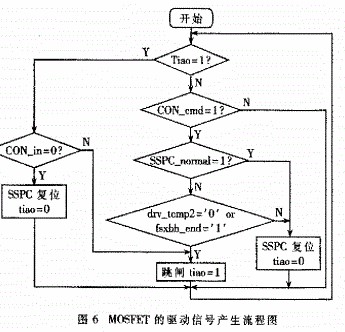

用VHDL语言实现的反时限保护算法流程如图5所示。

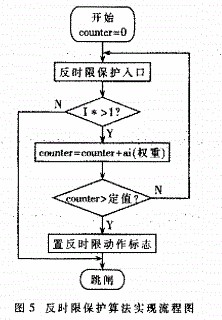

(3) SSPC将内部采集到的电流信号、接收到的控制命令和内部状态(包括系统启动的状态、电流在不同的范围内变化、跳闸的条件和从跳闸恢复到正常的条件以及故障切除和未切除时的系统启动等)经过逻辑判断后,综合出MOSFET的导通/关断指令,作为驱动电路的输入信号。

软件流程如图6所示。

5 试验结果

该仿真是在ALTERA系列CPLD的开发环境MAX+PLUS II上进行的。当在不同的电流值下采集到的四路SSPC负载电流为不同值时,SSPC的工作情况也不一样。

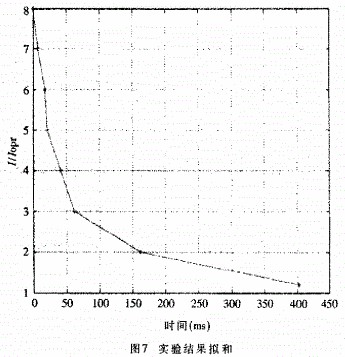

(1) 当I/Iopr8时,SSPC立即跳闸。

(2) 当I/Iopr为1.2(SSPC_1)、2(SSPC_2)、由1.2增加到2(SSPC_3)和5(SSPC_4)时,SSPC的跳闸时间分别为402ms、161ms、223ms和26ms。

各个临界点的实验所得数据经过曲线拟和,得到如图7所示结果。

试验结果表明,利用CPLD进行SSPC的开发设计,其延迟时间完全可以通过编程控制,且各路SSPC之间干扰较少。

CPLD内部的硬件结构决定了系统良好的抗干扰性和高可靠性,非常适合于电力系统方面的控制。因此,采用CPLD应是一个研究方向。

-

基于PLD器件EPM3256ATC144-10芯片实现固态功控系统的设计2020-07-15 2077

-

利用可编程器件CPLD/FPGA实现VGA图像控制器的设计方案2020-08-30 1765

-

基于CPLD控制的直流固态功控系统的研究与设计2021-03-17 3286

-

汽车类多开关检测接口 (MSDI) 设计包括BOM及组装图2018-09-26 2800

-

多开关检测接口实现尺寸更小空间利用率更高2019-03-18 1559

-

如何利用CPLD实现直流固态功率控制器的设计2021-04-30 1544

-

怎么实现基于DSP芯片和CPLD的刹车控制系统设计?2021-05-12 1338

-

如何利用CPLD进行数字逻辑器件设计?2021-05-14 1304

-

CPLD 器件在电机调速中的应用2009-05-15 444

-

CPLD器件应用2010-01-27 524

-

基于CPLD的电器定时开关控制系统设计2010-12-17 517

-

基于CPLD的开关电容组式跟踪滤波器设计与实现2013-09-25 814

-

如何使用CPLD进行电器定时开关控制系统的设计2019-06-11 1280

-

利用MAX II CPLD实现LCD控制器2023-11-10 540

-

NXP MC33978:22通道多开关检测接口芯片的深度解析2026-03-31 345

全部0条评论

快来发表一下你的评论吧 !