基于SOPC的1553B总线通讯解决方案

描述

自2005年9月LXI总线推出以来,已经显示出其组建测试系统的众多优点。基于LXI总线组建测试系统具有易于使用、灵活性高、模块化和可扩缩性、实现更快的系统吞吐率、可分布式应用、长寿命、低成本、通过IEEE1588时钟同步、机架空间小、合成仪器等诸多优点。

1553B总线的全名为"时分制指令/响应式多路传输数据总线",国内多型战斗机、军舰等武器平台都采用其作为传输总线。因此研制基于LXI总线的1553B通讯模块,不仅能满足多型武器装备对1553B总线的测试需求,也对LXI总线在国内的研究和应用有推动作用。

1 模块总体方案

模块基本设计指标为:满足LXI规范C类仪器标准;支持DHCP、自动配置IP地址和手动配置IP地址;支持ICMP协议、TCP/IP协议和UDP协议;同步采用网络命令方式;能完成1553B在BC模式下的所有功能。

根据指标要求采用基于SOPC的32位处理器+实时多任务操作系统(Real Time Operation System,RTOS)总体方案,在一块FPGA芯片上集成了控制器和逻辑单元,既降低了开发的难度、减少了模块体积,也易于以后的升级。32位处理器有足够的资源可以扩充利用,RAM和ROM可以做的足够大,整个TCP/IP协议族可以做到系统里面去,甚至可以嵌入一个带TCP/IP协议族的操作系统。

2 基于SOPC的硬件设计与开发

片上可编程系统(System on a Programmable Chip,SOPC)将处理器、存储器、I/O口、LVDS和CDR等系统设计需要的功能模块集成到一个PLD器件上构建成一个可编程的片上系统,是一种灵活高效的SOC解决方案。SOPC结合了SOC和可编程逻辑器件各自的优点,具有灵活的设计方式、可剪裁、可扩充、可升级,并具备软硬件在系统可编程的功能,成为SOC设计的新趋势。

2.1 模块硬件架构

模块硬件主要由NiosII软核处理器、以太网组件、1553B总线组件、存储器、片内RAM、通用I/O接口和调试配置模块7部分组成,架构示意如图1所示。

图1 硬件架构示意图

1)NiosII软核处理器:模块的CPU,负责系统工作调度。在其内部移植了μC/OSII实时操作系统和LwIP协议;它接受客户端通过以太网发送过来的请求,经解析后回复Web界面或控制1553B功能接口;2)以太网组件(DM9000A):完成对以太网控制器的操作,将网络上的数据经以太网控制器送到网际层,由NioslI软核处理器内的LwIP协议处理;或者将网际层送来的数据经以太网接口发送出去:3)1553B总线组件(BU-61580):受NiosllI软核处理器控制,完成在BC模式下各类消息和命令的发送及状态的读取;4)Flash存储器:主要用来存储模块的一些固定参数和静态Web界面;5)片内RAM:RAM是在FPGA剩余逻辑中用Quartusll内所带的MegaWizard管理器生成的,这样就不需要外加RAM芯片。片内RAM主要是用来存储程序运行过程中所接收和产生的一些数据;6)通用I/O接口:用来完成对LED或按键的控制;7)JTAG调试模块和EPCS配置模块:J1TAG模块用来完成对程序的调试工作。配置是对FPGA的内容进行编程的过程,每次上电后都需要配置,EPCS配置模块允许NioslI访问EPCS串行配置器件。

具体开发主要有3部分工作:1)NiosII软核处理器及其外设的设计。2)自定义宏功能模块RAM的开发,这部分工作在QuartuslI软件中完成;3)应用软件程序的编写,在NiosIIIDE软件开发环境中完成。

2.2 模块硬件设计

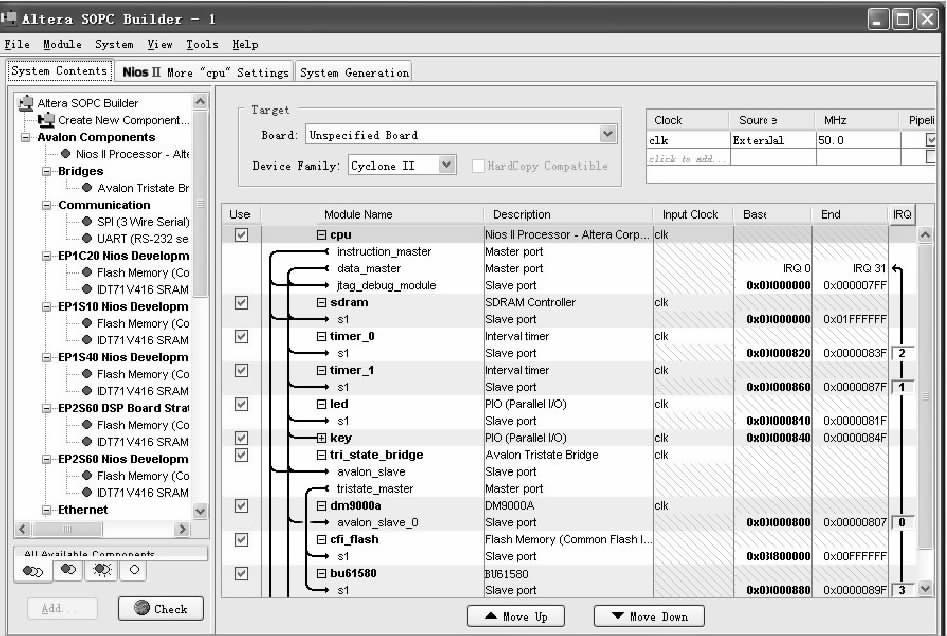

SOPC Builder是Altera公司为用户自定义系统而开发的工具。用户使用SOPC Builder可以将IP核、存储器、接口、微处理器和自定义组件等复杂系统组件简单又快速的集成到Ahera高密度FPGA芯片上。按照模块硬件系统的要求,借助SOPC Builder生成的模块硬件结构,包括:32位标准NiosII软核处理器:cpu;JTAG调试接口:jtag-debug-module;外部SDRAM存储器接口:sdram;Avalon三态桥:tri_state_brid ge;EPCS串行闪存控制器:EPCS_controller;外部FLASH存储器接口:cfi_flash;定时/计数器:time0/timel;以太网接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按键接口:key;系统识别模块:sysid。

图2 基于SOPC Builder的硬件系统设计

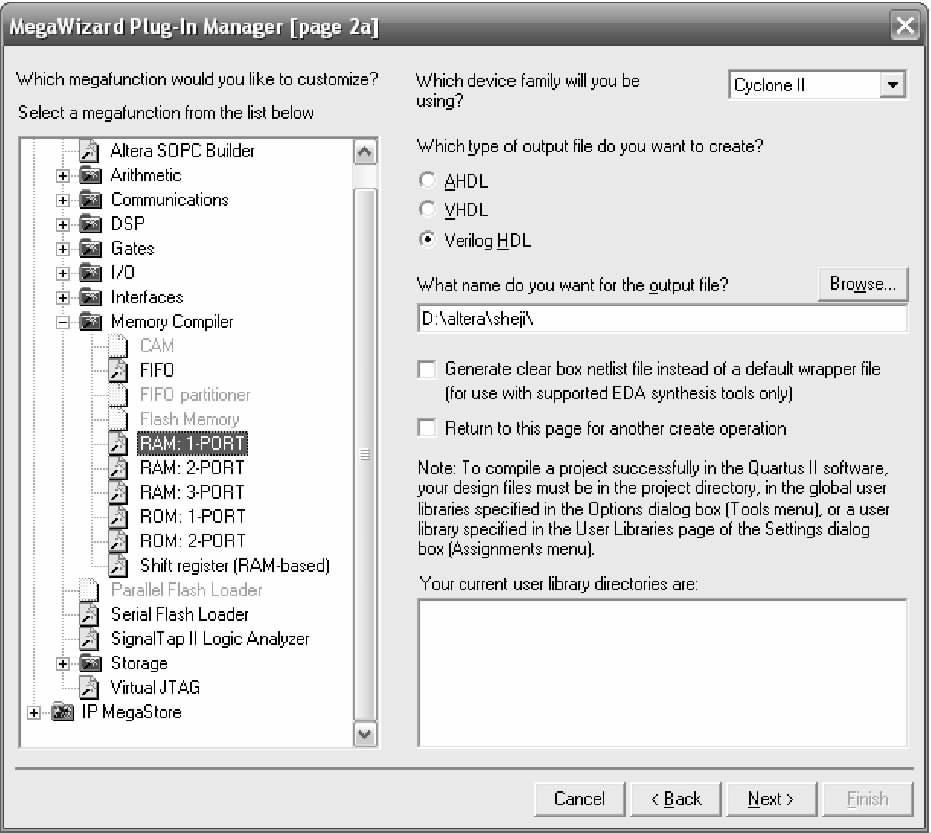

2.3 宏功能模块RAM生成

CycloneII器件内部的RAM块只有M4K一种,可用来实现真正的双端口、简单双端口和单端口的RAM,可以支持移位寄存器和ROM方式。用QuartusII内所带的MegaWizard管理器来生成RAM,首先运行MegaWizard管理器选择"创建一个新的宏功能",在出现的对话框内选择Insta lled Plug-Ins下的memory compiler下的RAM:1-PORT,如图3所示。

图3 MegaWizard管理器

在接下来的各页中选择如下参数:数据线宽度16位;存储64个字;自动单时钟驱动;选择生成*.v,*.bsf,*_inst.v,*_bb.v,*_waveforms.html 5个文件。其他参数默认即可。

2.4 以太网接口设计

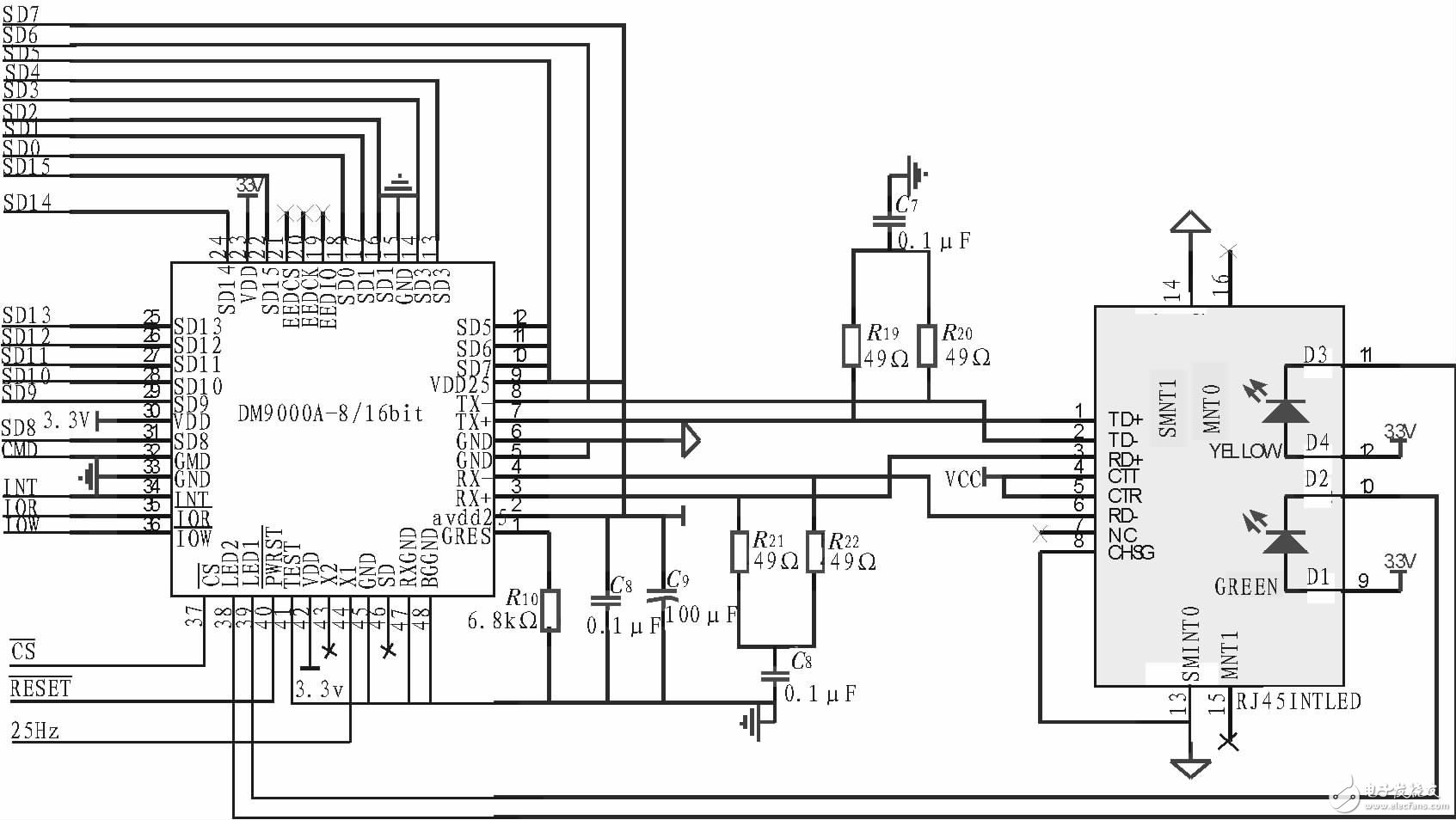

以太网控制器选用DM9000A,芯片为48管脚的LQFP封装,支持处理器接口以字节/字模式的I/O命令操作内部存储器数据,集成10/100M带有AUTO-MDIX的接收器,支持用于全双工流控制的IEEE802.3x标准,提供IP/TCP/UDP校验和生成以及校验过程,可选的EEPROM配置。

DM9000A与控制器和RJ45连接器的连接如图4所示。DM9000A与控制器有两种数据总线宽度的连接方式,即8位/16位模式,论文选用16位操作模式。DM9000A通过TX+、TX-、RX+和RX- 4条线与自带隔离变压器的RJ45转换器相连。RESET引脚为DM9000A的复位引脚,低电平有效;X1外接25 Hz时钟频率。

图4 DM9000A外围连接图

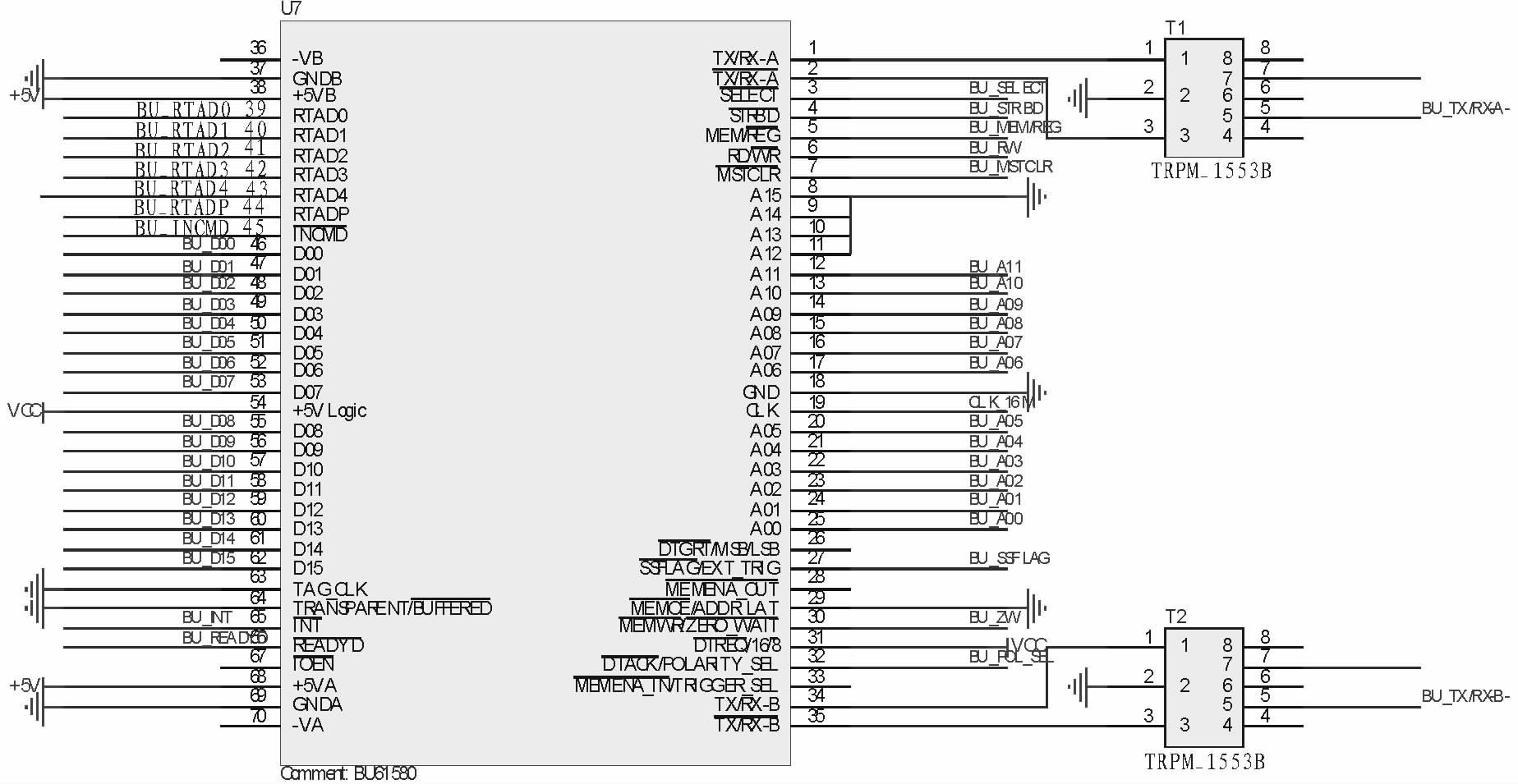

2.5 1553B接口设计

BU-61580与控制器的接口形式非常灵活,本文根据需求和资源情况选择16位缓冲连接方式。为了提高本模块的抗干扰性,论文采用变压器耦合方式。BU-61580的外围电路连接图如图5所示。

图5 BU-61580的外围电路连接图

3 模块软件设计与开发

3.1 软件结构设计

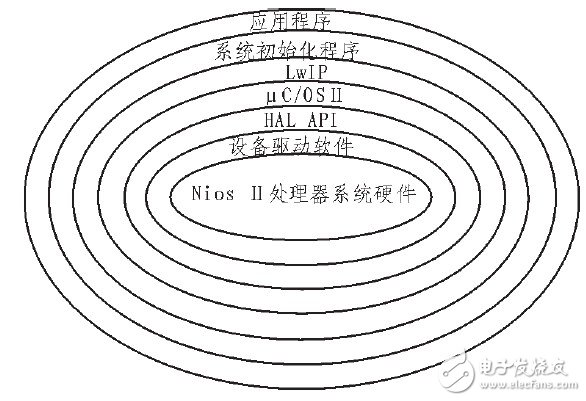

软件结构层次由NiosII处理器系统硬件、设备驱动程序、HAL API、μC/OSII、LwIP协议栈、系统初始化和应用程序7部分组成,如图6所示。

图6 软件结构层次图

1)NiosII处理器系统硬件:模型的核心,包括在FPGA中实现的NiosII软核处理器和硬件外设;2)设备驱动程序:管理以太网、1553B组件和其它外设的软件函数;3)HAL API:硬件抽象层应用程序接口,对设备驱动程序提供标准化的接口,对外层提供类似于POSIX的API;4)μC /OSII:实时操作系统层,为LwIP协议栈、1553B任务和嵌入式Web任务提供多任务和任务间通讯服务;5)LwIP协议栈:通过套接字API为应用程序和应用系统初始化提供网络服务;6)系统初始化:包括μC/OSII、LwIP协议栈和1553B组件初始化函数,也包括所有应用程序的任务、信号量、队列和事件性标志等实时操作系统任务间通讯资源的创建;7)应用程序:最外一层是建立的各项应用任务。

应用程序工作过程如下:首先进行系统初始化,然后进入工作等待状态。以太网任务等待客户端通过以太网发来的数据包,当有数包到达时,经物理层处理后交于TCP/IP层处理。在TCP/IP协议层之上,建立了3个套接字接口来侦听套接字连接:嵌入式Web端口、PING端口和1553B端口。对于1553B任务,根据客户端不同的请求,将启动不同的任务来完成相应的数据命令的发送或状态的读取。

3.2 基于μC/OSII的LwIP协议实现

轻量型IP(Light Weight IP,LwIP)协议是用于嵌入式系统开放源代码的TCP/IP协议栈。LwIP在保持TCP协议主要功能的基础上减少对RAM的占用,非常适合在嵌入式系统中使用。

LwIP协议栈在设计时就考虑了移植问题,把所有与硬件、OS和编译器相关的部分独立了出来,因此LwIP在μC/OSII上移植只需修改目录下的文件即可。

3.3 1553B总线协议任务的实现

为方便对BU-61580芯片操作,开发了BU-61580的驱动程序。驱动程序包括BU-61580芯片的初始化函数、BC发送接收命令函数、BC发送发送命令函数、BC发送接收/发送命令函数、BC发送不带数据字的方式命令函数和BC发送带数据字的方式命令函数。

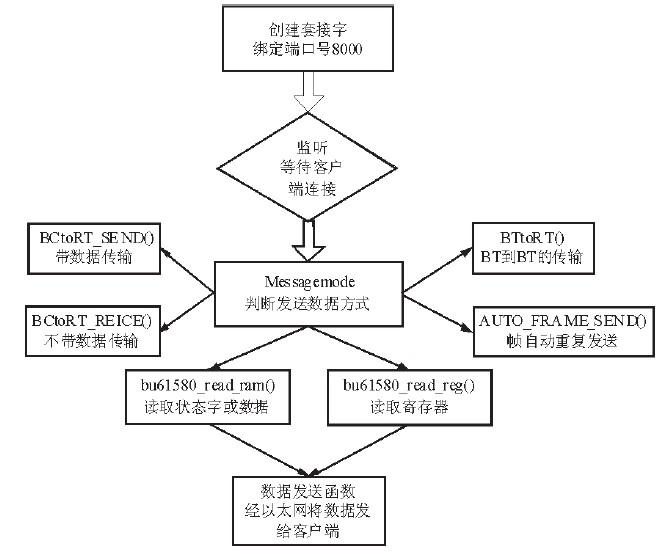

参考嵌入式Web服务器的实现方式,基于LwIP和μC/OSII建立了端口号为8000的1553B套字接口任务,流程如图7所示。

图7 套字接口任务程序的流程图

首先建立1553B任务接口守护进程,创建TCP套接字,绑定端口,将TCP套接字转换成侦听套接字,进入循环结构,等待接受用户的连接请求。当有客户端请求连接端口8000时,调用套接字数据接收函数recv()将客户端发送的数据读取过来,将数据映射到定义的结构体变量alt_avalon_BU61580*bdev上;用请求解析函数int 1553B_request(alt_avalon BU61580*bdev)根据messagemode判断需要采取什么操作方式:然后BU-61580的发送数据函数将数据内容写到相应的寄存器或存储器内,启动BC发送;如果调用读取数据函数,则将存储器或寄存器地址传递给读取函数,将读取到的数据调用函数int 1553B_transmit(&bdev[i],i)经以太网打包后发送给客户端。

4 仪器驱动程序开发

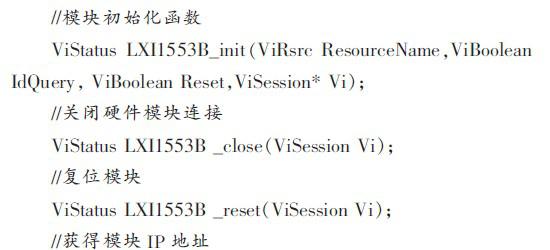

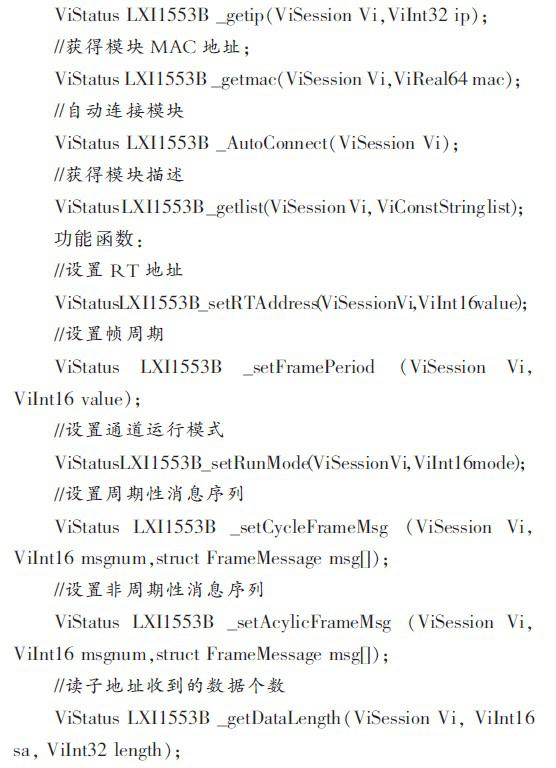

仪器驱动程序是介于上层用户应用程序和底层仪器硬件之间的一组函数,用户在开发上层应用程序时,可以调用这些基本动作函数来使用仪器,而无须与底层硬件通讯。

参阅VPP规范,模块提供了基于VISA函数的仪器驱动程序。通过调用VISA函数,向模块发送命令来完成模块的功能。开发环境为LabWindo ws/CVI,而选用Agilent VISA作为VISA函数库,主要是考虑Agilent是LxI总线的发起者,而且其提供的Agilent I/O Libraries封装了许多关于LxI的功能。VISA函数所用的LxI仪器描述符有两种:

1)对于VXI-11规范为:TCPIPO::192.168.4.10::instO::INSTR;

2)对于Sockets接口为:TCPIPO::192.168.4.10::8000::SOCKET.

其中192.168.4.10为模块地址(非固定),8000为1553B接口任务的端口号。开发的驱动程序以动态链接库形式提供给上层应用程序使用。

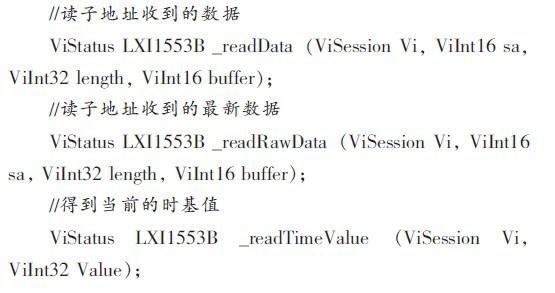

仪器驱动程的开发步骤、驱动函数原形以及发送的具体命令本文不再赘述。具体的驱动程序函数及其功能如下:

系统函数:

5 结论

针对基于LxI总线的1553B模块开发需求,本文提出了一种利用SOPC技术实现LxI总线到1553B总线通讯的硬件解决方法。在NioslI软核处理器上移植了μC/OSII嵌入式实时操作系统,实现了TCP/IP协议;开发了以太网和1553B自定义组件,并开发了其相应的DM9000A和BU-61580驱动程序;最终开发了仪器的驱动函数为便于模块工程应用。

文中设计方法降低了仪器的开发难度,减少了模块体积,同时也便于模块的升级,具有良好的工程应用和经济价值。

-

基于LXI总线的1553B通讯模块设计与开发2023-10-24 446

-

基于DSP的1553B总线系统设计解析2017-10-31 1809

-

1553B通讯模块设计与开发方案2017-10-19 1324

-

MIL-STD-1553B入门教程_1553B总线资料课件2012017-10-14 1522

-

1553b总线2016-04-16 5196

-

基于PCI局部总线的1553B总线接口卡设计2012-07-31 4114

-

什么是1553B总线?2011-04-19 3594

-

MIL-STD-1553B入门视频教程 1553B总线资料课件2011-02-13 6967

-

基于SOPC的1553B总线接口逻辑设计2010-01-25 741

-

基于SOPC的1553B总线远程终端接口设计2009-12-19 931

-

基于ARM的1553B总线应用2009-09-03 971

-

1553B总线在武器通信中的应用探讨2009-06-19 1035

全部0条评论

快来发表一下你的评论吧 !