PCIe中断机制介绍(MSI)

电子说

描述

前面的文章中介绍过,MSI本质上是一种Memory Write,和PCIe总线中的Message概念半毛钱关系都没有。并且,MSI的Data Payload也是固定的,始终为1DW。

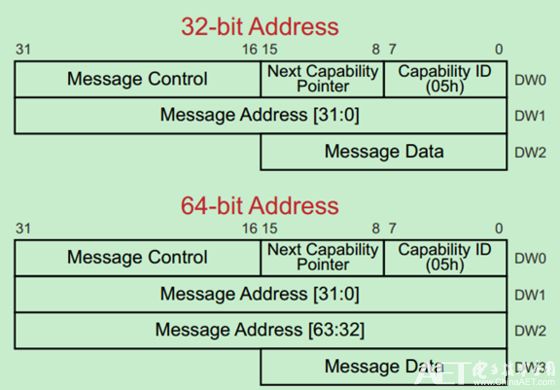

由于MSI也是从PCI总线继承而来的,因此MSI相关的寄存器也存在于配置空间中的PCI兼容部分(前256个字节)。如下图所示,MSI有四种类型:

其中Capability ID的值是只读的,05h表示支持MSI功能。

Next Capability Pointer也是只读的,其用于查找下一个MSI的位置,00h则表示到达Linked List的最后了。

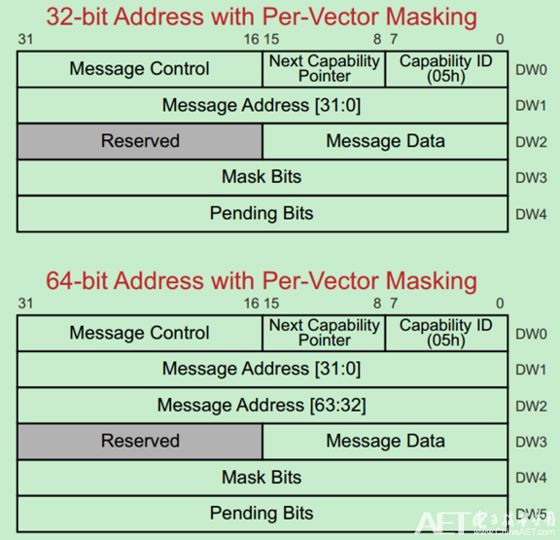

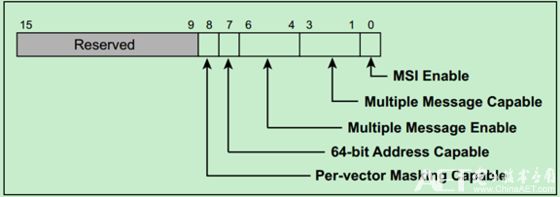

Message Control Register用于确定MSI的格式与支持的功能等信息,如下图所示:

具体描述如下:

Message Address Register:32-bit最低两位固定为0,使得该地址是DW对齐的。

当Mask Bits将相关的中断向量(Interrupt Vector)屏蔽后,该MSI将不会被发送。软件可以通过这种方式来使能或者禁止某些MSI的发送。如果相关中断向量没有被屏蔽,则如果发生了相关中断请求,这时Pending Bits中的相应bit则会被置位。一旦中断信息被发出,则该bit会立即被清零。

注:可能有的人会有疑惑了(无论是Mindshare的书,还是PCI的Spec都没有明确解释),因为Mask Bits和Pending Bits都只有32位,而8位的中断向量号最多可以表示256个!显然,32位最多只能对应32个中断向量号,无法支持256个的。实际上,一般的系统不会支持256个中断向量号的,32个就已经足够用了,所以并不用担心这个问题。

PCIe设备会根据配置空间中的MSI请求信息,来创建Memory Write TLP,来讲MSI信息发送出去。作为一种特殊的TLP,传递MSI的TLP需要遵循以下规则:

· No Snoop和Relaxed Ordering bits的值必须为0

· TLP长度值必须为01h

· First BE必须为1111b

· Last BE必须为0000b

· 地址是直接从配置空间中的响应位置复制过来的

如下图所示:

-

一文看懂PCIe中断机制2026-03-11 520

-

PCIe热插拔机制介绍2024-11-20 5952

-

MSI中断简介和生成方法2024-02-25 5702

-

Linux内核PCIE基础知识整理2024-01-12 4146

-

PCIe设备发出MSI-X中断请求的方法2022-02-16 1092

-

x86处理器如何处理MSI-X中断请求2021-12-17 1084

-

教大家如何处理x86处理器中MSI-X中断请求2021-08-12 8319

-

简述MSI和MSI-X中断机制2021-08-10 7027

-

简述PCI总线的中断机制2021-07-18 3895

-

克服MSI机制的三个主要的缺陷2018-09-02 5229

-

PCIe两种中断传递方式2018-08-31 9935

-

DM8168 C6678 pcie msi 中断不能触发,请问是什么原因?2018-08-06 4328

-

PCIE MSI中断的配置2018-06-21 4047

全部0条评论

快来发表一下你的评论吧 !