采用VHDL语言在FPGA芯片上实现NAND Flash的数据存储系统的设计

描述

引言

传统的存储设备虽然具有价格低廉的优势,但是在高温、高速、高冲击的测试环境中,往往存在设备存放空间有限、测试参数较多、采集速率高、环境复杂等因素。为了得到准确的测试数据,对存储设备的性能也提出了较高的要求,如高存储速度、大存储容量、小巧轻便、抗冲击等。此时传统的存储设备便无法完成复杂环境测试数据的存储任务。为解决这个问题,本文设计了基于NAND Flash的数据存储系统,该系统采用Xilinx公司提出的灵活、高效、低成本的解决方案SOPC,把通用的RISC处理器MicroBlaze与用户设计的特定功能逻辑电路集成到FPGA上,在FPGA的控制下将数据存储到NAND Flash存储设备中,实现了一个基于SOPC方案的嵌入式数据存储系统。

NAND Flash存储设备是Flash内存的一种,其内部采用非线性宏单元模式,为固态大容量内存的实现提供了廉价有效的解决方案。NAND Flash存储器具有体积小、功耗低、读写速度快等优点,适用于大量数据的存储,被广泛应用到数码相机、MP3、U盘等嵌入式产品中。

1 系统整体设计方案

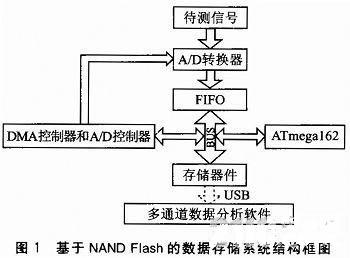

基于NAND Flash的数据存储系统结构框图如图1所示。

本文采用Samsung公司的NAND Flash芯片K9F4GOSUOA作为主要存储器件,控制器件使用Atmel公司的ATmega162和Xilinx公司Spartan-3E系列的XC3S500E,结合对NAND Flash的读、写、擦除等操作进行时序配置。A/D转换芯片使用Maxim公司的MAX1308.另外,为实现通过USB总线将数据从采集设备传送至PC,采用FTDI公司的FT245R芯片作为USB2.0接口控制器;并以LabVIEW为平台设计开发了专用"多通道数据分析软件",用于对存储系统中数据后期的分析与处理。

2 NAND Flash阵列式存储原理

Flash存储器编程是以页为单位,单片NAND Flash的单页编程操作时,命令锁存信号CLE向端口写入编程操作命令,地址锁存信号ALE写入操作块地址,并传输2 KB数据到数据寄存器后,Flash进入编程阶段。此时其端口R/B信号被拉低,显示Flash正处于忙工作状态,直到编程结束,这段时间系统不能对该Flash再进行任何操作,一般该阶段典型的时间为200μs.如果使用单片Flash存储器进行存储,则需等待编程结束后才能再写入数据。这样大量的时间耗费在编程过程中,极大限制了系统存储速度的提高。

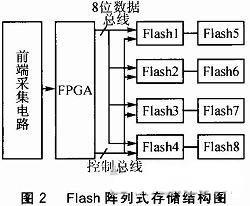

为提高系统的存储容量和存储速度,系统使用8片NAND Flash存储器,每4片为一组构成一个总线宽度为8位的存储阵列。控制信号中除设置独立的片选信号CE外,其他的控制信号为8片共用;两组Flash共用数据总线,存储数据时先对第一组Flash进行存储操作,待第一组存储完毕后再对第二组进行数据存储操作。Flash阵列式存储结构图如图2所示。

由以上分析可以看出,Flash存储数据的过程由写地址命令、数据传输以及Flash编程阶段组成。为提高系统整体的存储速度,减少系统等待时间,根据NAND Flash存储器的特点,借鉴时分多路复用技术,设计了Flash存储阵列,即利用上一片Flash的编程时间对下一片Flash进行操作,将数据加载到该片数据寄存器中,以此类推实现四级的流水线。这样整个系统每个时刻都能对Flash加载数据,保证了数据存储的连续性。

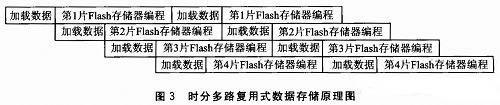

时分多路复用(Time Division Multiplexing,TDM)是按传输信号的时间进行分割的,它使不同的信号在不同的时间内传送,将整个传输时间分为许多时间间隔,每个时间片被一路信号占用,这样既可以保证各传输信号的相互独立,又提高了系统的传输效率。借鉴该原理,可以将Flash的编程时间看成一个固定的时间段,将这个时间段分成4个时间片,在这4个时间片上分别对Flash阵列的一个模块中的4个Flash加载数据,输入存储系统的高速数据流看作是以传输一组数据所需时间的一个时间片。

具体的操作如下:首先加载数据到第1片Flash存储器中,该Flash进入编程状态;在第1片Flash的编程时段内,对第2片Flash进行数据加载操作;当第2片进入编程状态时,再对第3片进行数据加载操作;依次执行下去,待一次整体操作完成后4片Flash都已加载完数据。此时,第1片Flash的编程已经完成,处于准备就绪状态,可以写入新的数据,由此可以等效为Flash存储器的编程时间为0.这样就可以实现Flash阵列的连续传输数据,提高系统的整体速度。

多片Flash时分多路复用式数据存储原理如图3所示。

3 系统硬件实现

系统采用了Xilinx公司的FPGA进行SOPC开发,处理器选用了MicroBlaze软核,并配置相应的参数使标准IP核适应用户所设计的系统,结合外围电源电路、USB接口电路、程序配置电路,构成了一套稳定的数据存储系统。

3.1 FPGA片上系统的实现

FPGA程序主要的功能是:软件控制启动存储,在控制逻辑的作用下将前端A/D转换之后的数据先存入内部FIFO缓存中,同时启动DMA将缓存中的数据存储到外部NAND Flash存储阵列中。本文利用VHDL语言编写程序,在FPGA芯片上实现了数据的高速存储和传输控制。

3.2 USB接口电路模块

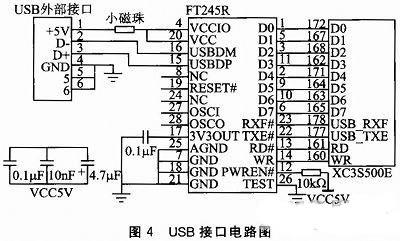

USB器件主要用于实现SOPC系统在联机模式下与主机通信以及数据的传输。USB芯片使用由FTDI公司推出的FT245R,该接口能够将USB接口信号转换为8位并行信号,上传至时钟频率为150 MHz的MicroBlaze处理器进行分析处理;并将处理器发送的数据转换成标准的USB接口数据传向PC机,完成SOPC系统与PC机之间的通信。USB接口电路如图4所示。

3.3 FPGA配置电路模块

本系统在FPGA配置电路中采用了主串配置模式。外部的配置芯片选用了XCF04S系列的PROM串行配置芯片。当系统上电时,芯片以主动配置方式来实现系统中FPGA的硬件配置。通过高速的串行接口,整个芯片的配置工作可以在很短的时间内完成。

3.4 电源模块

电源模块不仅能够为系统各器件提供各种高性能的功率输出,还能够选择合适的旁路、去耦电容来滤除各种干扰信号,保证系统的稳定工作。本系统电源模块采用了TI公司的TPS75003芯片配置相应的外围电路,实现了由5 V输入电压到3.3 V、2.5 V和1.2 V输出电压的精确转换。

4 系统验证与分析

在系统的软硬件程序设计完成并生成BIT流文件后,下载到FPGA电路板上,结合PC机中的专用软件对系统功能进行验证测试。

4.1 对NAND Flash的操作验证

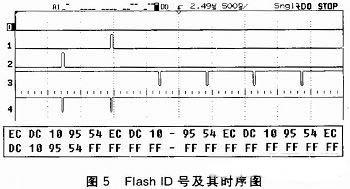

在数据存储硬件系统设计过程中,用户IP核设计得好坏决定着整个系统设计的成败。系统IP核设计中集成了Flash控制器、DMA控制器以及数据和地址FIFO,为验证该IP核是否能正常工作,对其进行了Flash操作验证。示波器捕获的读Flash存储器ID号时序图如图5所示。其中通道0~4分别代表Flash的CE(片选)、ALE(地址锁存)、CLE(命令锁存)、RE(读)、WE(写)信号。图中Flash阵列的4片Flash的ID号都为EC DC 10 95 54,这与实际Flash ID相符。实验证明,Flash存储器的ID号是准确的。

4.2 文件登记表验证

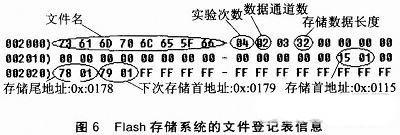

实验中在Flash存储器的特定位置存有标记数据特征的文件登记表,应用程序读取文件登记表中的信息并将相应数据传输到PC机上进行后期分析。文件登记表的存储内容有:文件名、实验的次数、存储数据的长度、本次存储的首尾地址以及下次存储的首地址等。

图6为某次存储实验的文件登记表信息,图中前8个字节为文件名,往后依次为实验次数和数据通道数。本次实验中存储的长度为50 MB,存储首地址和存储尾地址分别为0x0115、0x0178.由于所用的存储策略为4片流水线式存储,每片Flash每块为128 KB,4片组成的模块中每个大块为512 KB(128 KB×4),所以可以计算出存储的数据为512 KB×(0x0178-0x0115+1)=50 MB.这与所指定的本次存储数据的长度吻合,表明存储系统正确可靠。

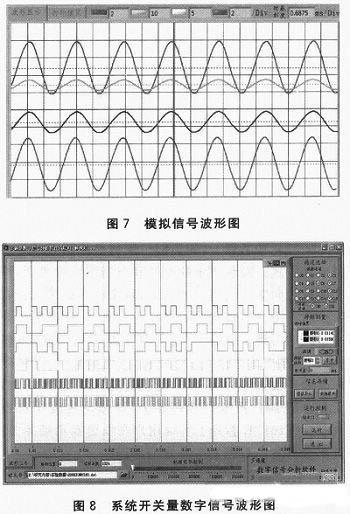

4.3 数据存储验证

系统构建完成后,在实验室环境中,对信号发生器产生的正弦波信号进行采集存储,通过USB接口将存储在NAND Flash芯片中的数据上传到PC机中,利用以LabVIEW为平台设计开发的"多通道数据分析软件"进行分析处理,得到的模拟信号及系统开关量数字信号波形如图7、图8所示。

对比原始信号发现,系统能够快速、无失真地采集并存储信号发生器产生的波形数据,并且能够利用不同的采样速率来记录系统开关量数字信号信息,具有较高的可靠性。

结语

本文设计了基于NAND Flash的数据存储系统,通过时分多路复用式流水线操作,极大地提高了Flash芯片的存储速度。实验表明,该系统能够快速、准确地记录信号发生器产生的波形数据,且具有性能稳定可靠、操作简单、抗过载能力强等优点。

-

如何使用FPGA实现多通道图像采集存储系统的设计2021-01-29 1094

-

NAND Flash 的存储结构以及NAND Flash的接口控制设计2020-11-03 5647

-

基于FPGA器件实现大容量高速存储系统的方案设计2020-07-30 3257

-

采用VHDL语言在FPGA上实现WolfMCU体系结构的设计2020-07-28 1119

-

NAND闪存存储系统的低故障率如何实现?2019-08-01 1735

-

基于FPGA并以Flash为存储介质的高速图像数据存储系统设计2017-11-18 4696

-

NAND Flash存储系统解决方案2017-10-19 1061

-

标准NAND FLASH控制器/超高速NAND FLASH阵列控制器2014-03-01 3568

-

求:基于FPGA的数据采集存储系统的sch原理图2012-10-29 3034

-

标准NAND FLASH控制器2012-02-17 16

-

NAND Flash嵌入式存储系统设计2011-04-25 1700

-

Nand+Flash存储管理在DSP系统中的实现2010-04-12 1823

-

基于套接字的Flash存储系统研究和实现2010-01-20 1420

-

基于FPGA的微型数字存储系统设计2009-11-04 1170

全部0条评论

快来发表一下你的评论吧 !