FPGA器件在游戏控制台设计中的应用

描述

FPGA的简介:

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

游戏控制台设计者必须在实现系统的多功能、可靠性和低成本之间寻找平衡。市场压力经常迫使最初的控制台价格低于可盈利的水平。不过,要在商业上获得成功,游戏控制台就必须能够提供多种功能,如高清晰度图像、网络连接、运动传感控制器以及基于IP的视频内容,并且所有这些都要在用户能承受的价格内。

为保持低成本特性,通常采用基于平台的方法来设计游戏控制台。目标是尽可能地使每个控制台相似,同时还能满足特殊区域的要求。单个平台设计通常是不现实的,经济效益上也不可行,但FPGA所提供的硬件灵活性使得游戏系统能够很容易地针对不同区域、模型、组件和升级版进行重新设计。

一个典型的游戏控制台包括CPU、图形处理器、存储器件、通信单元、I/O和用户接口。游戏控制台的核心通常是几个大规模ASIC(Application Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路)或ASSP(ASSP Application Specific Standard Parts(专用标准产品)是为在特殊应用中使用而设计的集成电路)。例如,iSuppli的报告指出,Sony PS3就包含一个7个核定制基于cell的CPU(ASIC)、一个NVIDIA图形芯片组(ASSP)、XDR存储器和一个flexIO处理器接口。

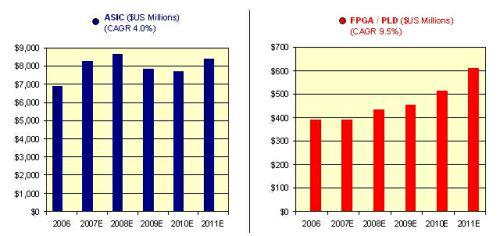

由于FPGA在许多应用中取代了ASIC,或许现在是时候将它用于下一代游戏控制台设计中了。FPGA和PLD相对较低的成本正在推动其在消费电子产品中的使用,尤其是在LCD和等离子电视中。根据Gartner Group的报告(如图1所示),在未来的4年中,用于消费电子产品的PLD和FPGA器件的全球市场年均复合增长率(CAGR)预计将达9.5%,超过了年均复合增长率为4.0%的ASIC器件。

图1:用于消费电子设备的ASIC和FPGA的年收益变化。

基于平台的游戏控制台设计考虑因素

FPGA可以帮助系统设计者尽可能地节约成本并提供最大的灵活性,这是由基于平台方法通过提供以下设计方针来实现的。

需求和模型可随着区域而变化:针对多个标准和格式提供可编程支持能加快产品上市时间;低成本和可靠的设计:集成全部的系统I/O接口、控制逻辑和调试功能,以支持连接至HDD和内部存储器的ASIC/ASSP芯片组的桥接功能,定制的用户接口逻辑可降低在新产品中的风险;在最终测试期间和现场的安全编程能够实现对多种标准的支持、协处理算法的增量升级以及易于对新功能进行测试。

带有嵌入式DSP解决方案的FPGA

在选择面向平台的可编程器件时,通常需考虑三种电路要求:面向协处理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM块(EBR),这种协处理功能利用并行方法,针对具体应用以最优成本对功能和性能进行裁剪。低电压差分信号(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能够安全地保护知识产权。

图2显示了一个满足这些要求的FPGA解决方案。FPGA被连接到主CPU、图像处理芯片、用户接口和诸如无线以太网的其它关键ASSP。FPGA模块执行协处理功能和硬件加速,并具有实现未来功能所必需的定制逻辑,这些功能是针对用户接口或控制台的其它部分。

DSP协处理和硬件加速

尽管低成本FPGA通常工作在小于300MHz的系统时钟频率下,但通过并行地执行串行功能仍然可实现很高的DSP吞吐量(63,000MMAC)。例如,某个应用要求具有100MS/s采样率的32抽头FIR滤波器,那么需要带有4个乘法器的通用DSP处理器以800MHz计算乘累加。具有32个乘法器的FPGA能够在100MHz实现相同的滤波器。

与乘法器一样,能够灵活地利用FPGA的并行特性有益于存储器访问。片上分布式存储器可用来构建小容量高性能临时存储器,而片上嵌入式存储块可用来构建大容量高性能存储器。DDR DRAM等片外存储器则可以提供大容量、高性能存储器

高速的芯片至芯片互连

FPGA通过高速的芯片至芯片互连技术与GPU和CPU连接,这些技术包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技术,即串行地发送数据,并通过LVDS以数据包的形式恢复数据,而不是一次恢复一位。从并行到串行接口的转换系统可用较少的线路达到同样的高速数据速率。

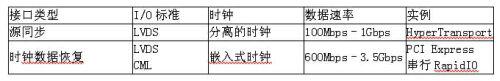

源同步和时钟数据恢复接口

HyperTransport是一个源同步接口,而PCI Express和串行RapidIO采用时钟数据恢复(CDR)技术,如下表所示。对于源同步接口而言,传送方提供数据和差分时钟,这样就能较容易地在高达700Mbps的数据速率捕获数据。

源同步和时钟数据恢复接口。

当数据速率超过700Mbps时,数据通道之间的偏移成为数据有效窗的重要部分,特别是对宽数据通道而言。有些FPGA具有自动对齐功能,能够针对源同步接口管理数据偏移,从而有助于它们达到超过800Mbps的LVDS数据速率(有些情况下高达2Gbps)。

对于CDR接口而言,并没有提供额外的差分时钟。取而代之的是时钟包含在串行数据包中,必须从数据中恢复出来。因此,对于CDR来说时钟偏移不是一个问题,这与源同步不同。利用SERDES高速串行地发送数据包,CDR接收器将对数据本身锁定相位以取得时钟。

对于CDR而言,在高速情况下,SERDES抖动是主要问题。抖动是指期待数据传输的位置发生了变化,使得难以准确地接收到数据包。如图3所示的眼图,抖动使得围绕眼睛的黄色带的宽度发生变化,图中用红色表示。

图3:CDR眼图。

有些抖动是随机的,但大部分抖动是确定性的,是由于其它信号以及靠近数据信号的半导体元件的开关操作引起,或者是由数据模式的特性、传输的不平衡上升及下降时间所引起。

安全配置和现场升级

游戏控制台往往是电脑黑客攻击的目标,因此FPGA不应该在配置期间给系统引入额外的弱点。对于基于SRAM的FPGA而言,配置数据通常来自外部的非易失存储器。为保护该数据,一些FPGA加入了内置的128位AES加密引擎。面向AES的FPGA解密密钥采用一次性可编程(OTP)熔丝编程。OTP密钥是非易失的,且一旦密钥被编程就不能修改,从而可阻止黑客用逆向工程探寻FPGA内部的功能。

此外,FPGA能帮助设计者桥接ASSP功能与图像处理器或系统处理器。桥接的例子包括无线以太网(802.11)和用户接口控制逻辑。定制的用户接口逻辑有助于将游戏控制台与竞争产品区分。用FPGA解决方案可以桥接或控制这两种功能。

成功的策略

根据Booz Allen Hamilton公司今年三月发布的报告,Darden商业研究生院的Tim Laseter在2007年的一项研究认为,许多成功的公司并非是最先进入某个领域的先行者,而是能够发现更多资源的后来者。例如,在Xbox 360和PS3之后,任天堂公司发布了不具有高清晰图像的Wii游戏机。但是,采用Wii游戏控制台的人数在不断增加,因为这种游戏控制台具有运动敏感的控制器和受家庭喜爱的游戏主题。

研究得出的结论是,在各种不同的技术中,多个小实验能够产生对如何创造价值的更多认识。我们不可能在当前就准确地知道客户将来需要什么特性,或者硬件设计是否有小故障,或者主要的可靠性问题。由于“广泛的硬件故障”,微软公司花费了10亿多美元来修补Xbox 360控制台并将其纳入保修范围。

在游戏控制台设计中采用FPGA可对硬件功能进行一些小实验,从而有助于未来验证游戏控制台的设计。设计集成了一个可选的连接器用来连接至FPGA,并能够实现未来的特性,或者FPGA可以通过以太网进行连接,从互联网下载新的位流并实现新的功能。这些实验可能还包括对人工智能、DVD倍线功能、附加的家长控制功能和新型用户接口的测试。

市场要求所有设计游戏控制台的公司能够以尽可能低的制造实现更多的特性。如果设计出来的产品未加入重要的特性或灵活的接口,这些公司将会蒙受亿万美元的损失,更糟的是,产品可能根本没有市场需求。

现在很有机会将一些小型的技术革新加入游戏控制台系统,以支持未来将发生的变化,或者用硬件而不仅仅是固件来试验新的特性。构筑一个在游戏控制台中支持PCI Express、HyperTransport或串行RapidIO、LVDS和DSP的安全FPGA使得这些技术革新都有发展机会。

LatticeECP2M FPGA系列产品可支持许多这方面的要求,包括AES加密位流、PCI Express、LVDS、DSP以及可编程逻辑,以支持多种接口标准和定制功能。此外,由于支持多个DSP知识产权核和MATLAB Simulink,也使设计更加方便。

-

控制台窗口主机是什么2024-10-08 11084

-

实现控制台的输出有两个方法2023-11-26 3936

-

python获取控制台输出内容2023-11-22 3634

-

通过C语言设计的贪吃蛇游戏(控制台终端)2023-06-30 2521

-

设备配置工具控制台在STM32CubeIDE中无法打开的原因?怎么处理?2022-12-29 607

-

带有ESP32 FutureBoard的DIY乐高视频游戏无线控制台2022-11-08 983

-

如何利用低成本FPGA设计下一代游戏控制台?2021-04-30 1520

-

提升.NET控制台应用体验的方案解析2020-10-29 2860

-

UART控制台出现问题2019-08-29 1569

-

采用低成本的FPGA器件和PLD进行游戏控制台的设计2019-05-16 1959

-

SU RUBy控制台如何使用?SU RUBy控制台的一个应用实例说明2018-09-27 2947

-

dmx512控制台是什么_dmx512控制台按键说明2017-11-07 28722

-

YY游戏云平台控制台实践详解2017-10-11 1067

-

电脑灯控制台的使用2009-12-12 2337

全部0条评论

快来发表一下你的评论吧 !