通过采用VHDL语言进行MTM总线主模块有限状态机的设计与仿真验证

描述

MTM总线(Module Testing and Maintenance bus,MTMbus)是一种同步、串行、用于系统级的背板测试及维护总线,可以实现IEEE1149.5标准所规定的故障检测、容错以及扩展的命令集。该技术已经被美军"宝石柱"和"宝石台"计划的航空电子系统体系结构采用。

当前MTM总线主模块有限状态机主要采用VerilogHDL程序编写的状态机描述,Verilog HDL语言并不可以进行系统级的硬件描述。

VHDL是一种标准化的硬件描述语言,不仅可以用于系统级的硬件描述而且在设计系统硬件时没有嵌入与工艺有关的信息,在工艺更新时无须修改原设计程序。文中设计的状态机采用"单进程"式状态机描述,与"三进程"和"双进程"式相比可以有效地节省FPGA芯片的资源,从而进一步减少功耗,提高系统的稳定性。

通过简要分析MTM总线的基本结构、各模块间的通讯方式、主模块有限状态机模型基于VHDL语言设计了主模块有限状态机;并且利用QuartusⅡ9.0版本软件和Cyclone系列EP1C60240C6芯片对所设计的MTM总线主模块状态机的VHDL代码进行了时序仿真和功能仿真。

1 MTM总线结构设计

1.1 MTM总线的基本结构

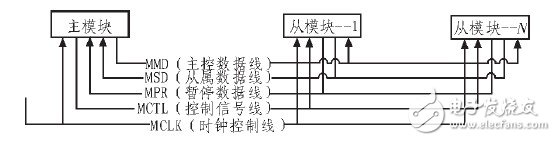

MTM总线的基本结构如图1所示,总线定义了4条必选信号线和一条可选信号线,即MCTL(控制信号线)、MMD(主模数据信号线)、MSD(从模块数据信号线)、MCLK(时钟信号线)和MPR(请求暂停信号线)。

图1 MTM总线结构图

MTM总线上的所有模块采用主从结构的通讯协议,该总线有且只能有一个主模块,最多可以有250个能够被独立寻址的从属模块。MTM总线多站点结构和寻址能力允许主模块一次可以寻址一个从模块、多个从模块(多点寻址方式)和所有的从模块(广播寻址方式),并且与之通讯。M TM总线的主模块有限状态机是MTM总线主模块的核心控制单元,它控制着整个信息传输过程。MTM总线控者使用消息交换的方式与从模块进行通讯,消息是由一系列的包组成,包括一个头包,一个可选答应包和一系列数据包,包的长度为17位,高16位数据信息,最低位用于奇校验,消息包的控制必须由主模块控制。

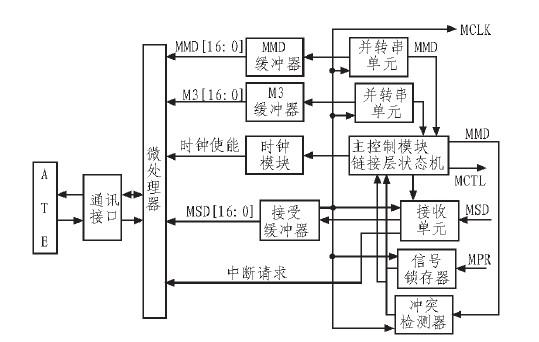

1.2 MTM主模块

主控制模块设计如图2所示。主控制模块在MTM总线协议中处于主控地位,主要功能是将来自微处理器的数据按照IEEE1149.5标准定义的消息格式进行打包送到指定的从控制模块;同时将来自指定从控制模块的消息包进行解包,并且提取有用数据传回微处理器,供微处理器分析和处理。

图2 主控制模块设计

主状态机是主控制模块的核心单元,它的作用是控制整个信息传输过程。

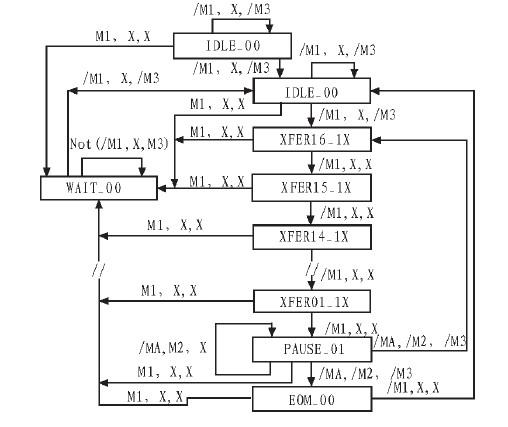

主状态机的状态转换图如图3.当主状态机处于某个给定的状态时,MCTL和MMD信号的逻辑值在MCLK的上升沿产生;在每个MCLK信号周期,主状态机根据控制信号的只发生状态转换;在主状态机的17个传送状态下发送17位的数据包,其他状态不发送数据,同时接收MSD上的数据;在每个数据包发送后,主状态机至少保持在暂停状态不少于4个MCLK周期,若当前接收的MSD数据有效则使接收单元使能信号有效;当主状态机进入结束状态时,当前消息传送结束。

图3 主状态机的状态转换图

2 基于VHDL的主模块有限状态机的的设计

VHDL主要用于描述数字系统的结构、行为、功能和接口,同时支持层次化和模块化设计,并且可以进行仿真和综合。

数字电路分为组合逻辑电路和时序逻辑电路两种。组合逻辑电路的输出只与当前输入有关,时序逻辑电路的输出与当前输入和过去输入都有关。状态机是一种广义的时序电路,一般包括用于状态译码和产生输出信号组合逻辑和存储状态的寄存器逻辑两部分。

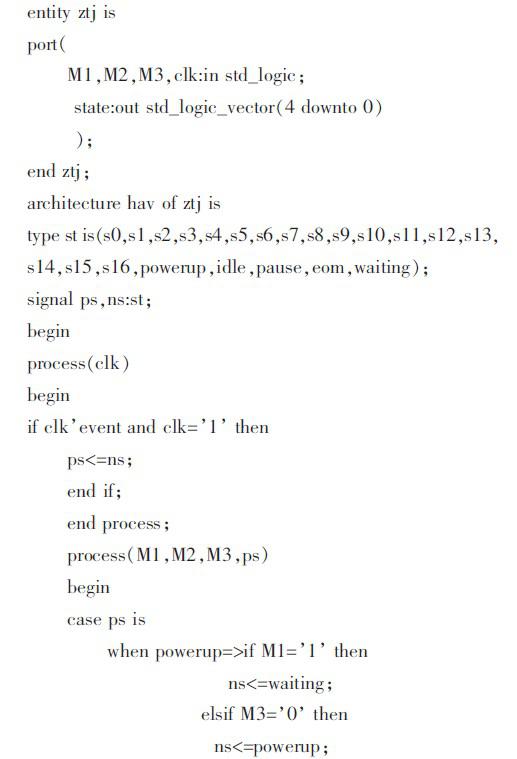

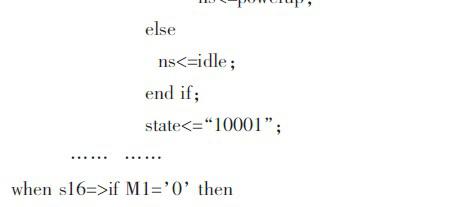

根据MTM总线主模块的状态转换图,其基于VHDL有限状态机的代码如下:

3 仿真验证

QuartusⅡ是Altera公司推出的集成开发软件,使用QuartusⅡ可以完成从设计输入、综合适配、仿真到编程下载整个设计过程,Quart usⅡ也可以直接调用Synplify Pro、以及ModelSim等第3方EDA工具来完成设计任务的综合和仿真。

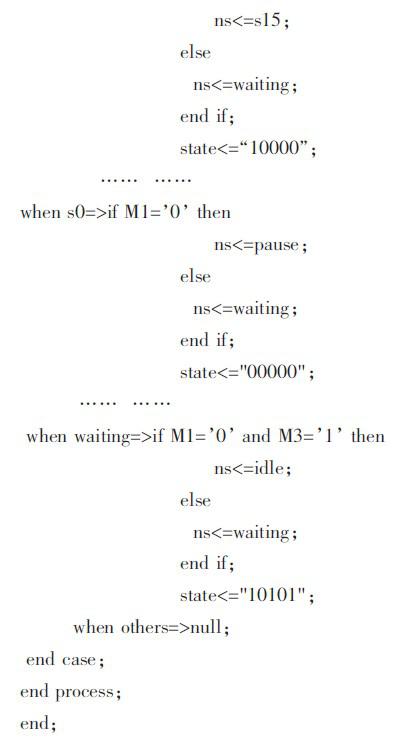

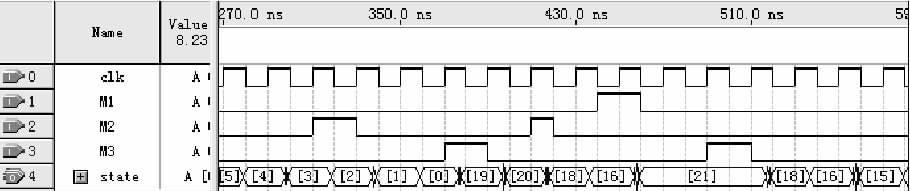

文中利用QuartusⅡ9.0版本软件和Cyclone系列EP1C6Q240C6芯片对所设计的MTM总线主模块状态机的VHDL代码进行了时序仿真和功能仿真,分别如图4、图5所示。

图4 时序仿真波形图

图5 功能仿真波形图

通过波形图可以观察到,该状态机可以很好的实现主状态机的状态转换。当M1输入为"0"时(此时M2、M3为无关状态),MTM总线主模块按照从高到低进行消息传送,直到进入"PAUSE"(暂停状态)然后状态回到"xfer16"(S16)继续进行消息传送;当M1输入为"1"时,主模块无条件进入"waiting"(等待状态);在主模块处于"waiting"状态时若M3输入为"1"状态转入"idle"(空闲状态)再次由高到低位的消息传送。

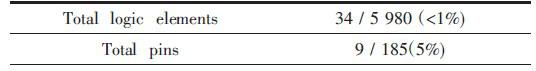

使用VHDL语言描述,语法更为严谨,描述更为清晰简洁;采用"单进程"式状态机描述可以有效地节省FPGA芯片的资源(表1),从而进一步减少功耗,提高系统的稳定性。

表1 编译报告

4 结束语

文中通过研究MTM总线的基本结构和主从模块间的通讯协议,分析了主状态机的状态转换,并使用VHDL语言设计了该有限状态机,并使用QuartusⅡ开发软件对该状态机进行了仿真和验证,仿真结果表明该程序可以正确描述主状态机的状态转换,该有限状态机使用"单进程"式描述,与"三进程"和"双进程"式相比程序简洁明了并且能够有效地节省资源,减少功耗,提高系统的稳定性。

-

有限状态机分割设计2023-10-09 1346

-

基于事件驱动的有限状态机介绍2021-11-16 3110

-

MOORE型有限状态机的几种设计方法是什么2021-05-07 1989

-

有限状态机设计是HDL Designer Series的关键应用2021-04-08 1182

-

有限状态机有什么类型?2020-04-06 4253

-

初学者对有限状态机(FSM)的设计的认识2017-02-11 4779

-

VHDL有限状态机设计-ST2016-06-08 1008

-

有限状态机的建模与优化设计2016-03-22 826

-

基于VHDL的MTM总线主模块有限状态机设计2012-05-29 923

-

有限状态机的硬件描述语言设计方法2010-09-03 788

-

基于有限状态机在LIN总线开发中的应用2010-04-20 1246

-

fsm有限状态机pdf2008-06-04 1503

全部0条评论

快来发表一下你的评论吧 !