利用FPGA对微型计算机的原理及结构进行研究分析

描述

引 言

通常,人们对微型计算机的工作原理及硬件结构的了解于书本知识,深入理解掌握其功能特点比较困难,要自己亲手去做一个类似功能的微型计算机更是不可能。随着可编程逻辑器件的广泛应用,为数字系统的设计带来了极大的灵活性,用户可以利用FPGA(现场可编程门阵列)来开发出一个精简指令的CPU,同时对微型计算机的原理及结构进行充分研究,便于将来进行相关ASIC(专用集成电路)设计,也可用于计算机原理教学之中。

1 微型计算机结构及原理

以一个简化的微型计算机为例,微型计算机的简化结构。

1.1 微型计算机结构

微型计算机由PC(程序计数器)、IR(指令寄存器)、CON(控制部件)、MAR(存储地址寄存器)、ROM(只读存储器)、A(累加器)、ALU(算术逻辑部件)、B(寄存器)、OUTREG(输出寄存器)、DLEDDIS(数码管动态扫描模块)及DECL7S(显示模块)等组成。这里仅介绍有所改变或不同的模块,其余可见文献[1].

L为数据载入控制信号,E为三态输出选通信号,clk为时钟信号,clr为清零信号,Cp为控制PC加1信号,S0-S3为控制ALU进行加减或逻辑运算的选择信号。所有的控制、时钟及清零信号由CON模块给出,而CON模块由外部时钟clkin及清零信号rst控制。PC可以置数,即可执行跳转指令。OUTREG可清零,便于多次调试。DLEDDIS及DECL7S用来把地址及结果在数码管上显示出来。

1.2 微型计算机原理

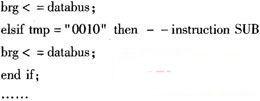

虽然这台微型机可以实现16条指令,但本文对指令不做扩展,仅以5条指令为例。LDA为将数据装入累加器A(操作码0000);ADD为进行加法运算(操作码0001);SUB为进行减法运算(操作码0010);OUT为输出结果(操作码1110);HLT为停机(操作码1111)。

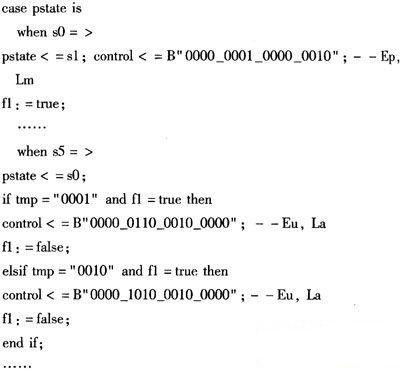

在程序和数据装入后,当外部给出时钟信号及清零信号无效时,由CON模块发出信号及控制字,开始取出和执行每条指令。如控制字顺序为ErLrS3S2S1SOEuLm LbEaLaEi LiCpEpLp,这里Lr可用于存储器为RAM时做写使能信号。由于采用的是数据总线与地址总线合一的总线结构,一条指令的执行需要6个机器节拍,即前3节拍取指周期与后3节拍执行周期。如执行ADD 0AH,机器码为1AH(0001 1001)。第1节拍将PC内容送入MAR,控制字为“0000 0001 00000010”,即Ep与Lm为1;第2节拍将ROM中对应地址单元中的内容送到IR,IR高4位送至CON,控制字为“1000 0000 0000 1000”,即Er与Li为1;第3节拍使PC加1,控制字中Cp为1,其余为0;第4节拍将IR的低4位送至MAR,Ei与Lm为1;第5节拍将ROM中的内容送入累加器A中,Er与La为1;第6节拍为加法运算,Eu与La为1,同时S0-s3选择为加法运算。

2 FPGA实现

2.1 总线方式

总线方式是指严格按图1用FPGA实现相应结构的微型机。本实验采用上海航虹公司的AEDK实验箱,FPGA芯片为Altera公司的EPF10K20TC144-4,软件采用QuartusII4.0、Max+plusII10.0及synplifypr07.5,程序设计采用VHDL语言。

共有11个子模块,最后用元件例化语句构成总模块。以设计程序计数器模块C-PC及控制模块C_CON为例简单做一介绍。

当三态输出信号es选通时,即es=“1”,PC可输出,否则输出为高阻态。数据或地址与总线相关的子模块都需采用三态门。由于采用了三态门,最好用QuartusⅡ软件来进行编译,Max+plusⅡ有时不一定可以通过。

用synplify pro7.5对C_PC模块进行RTL(寄存器传输级)原理图观察,如图2所示。其综合电路与一个4位二进制计数器类似,只是多了一个三态门。用synplify pro7.5不仅可以观察RTL电路,还可以观察门级电路结,深入了解其内部结构。

C_CON模块是最关键的模块,因为所有的控制信号都由它发出。由于指令执行需6个机器节拍,每个节拍对应相应功能,采用状态机是实现此高效率、高可靠逻辑控制的重要途径。如以下程序所示,每个状态对应着不同的控制字,共有6个状态。

只读存储器模块可使用LPM_ROM的LPM_FILE文件,便于调试不同的程序。

2.2 多路选择器方式

多路选择器方式是对总线方式的一种改进,可以实现地址总线与数据总线分离,一条指令的执行只需4个机器节拍,极大地提高了运行速度。对图1进行略微改变,如图3所示。其中程序计数器模块duolu_PC及指令寄存器模块duolu_IR不再有三态门,对其控制也相应简化。增加了2个二选一多路选择器。下面介绍其工作原理。

状态s0(第1节拍)时,首先判断有没有加减法指令,若有则发出控制信号,PC值同时送入MAR.如控制字顺序为ErLrS3S2 S1S0EuLm LbEaLaEi LiCpEpLp,有加法时,其控制字为“0000 1011 0010 0010”,当S3S2S1S0为“0001”时做加法运算;没有加减法时则控制字为“0000 0001 0000 0010”.状态s1时,PC值加1,将存储器单元中的内容读人到IR,其控制字为“1000 0000 0000 1100”,注意当给程序计数器置数时,Lp才为l,多路选择器选通由IR米置数。状态s2和s3与总线方式的第4和第5节拍类似。整个周期可简化为判断与置地址、读数、判断与置地址、读数4个步骤。

这里的多路选择器方式仅仅是略微改变,不是指全部,只是提出一种方法。

2.3 功能描述方式

功能描述方式是指充分利用VHDL语言的行为描述能力,从功能描述的角度来实现简易微型计算机。除了调用ROM模块及OUTREG、DLEDDIS、DECL7S外,其余子模块被包含在一个整体C_SIM_CPU模块内,每一个状态实现一定的功能。同样,C_SIM_CPU模块只需4个状态即可实现相应功能。部分程序如以下所示,不再采用控制字的方式。

C_SIM_CPU模块由于强调实现功能,其语句不同用户有着不同写法,不同的综合软件也会生成不同的结构,因而这里不再展开讨论。

2.4 3种方式比较

用QuartusⅡ4.0对总线方式、多路选择器方式及功能描述方式分别进行编程下载,都可以实现一些简单的计算程序,在数码管上显示出地址及相应结果。如果采用1 Hz的clkin频率,动态扫描频率单独用1 kHz时,可以清楚地看到每一过程。

QuartusⅡ4.0对总线方式、多路选择器方式及功能描述方式编译,其LE(逻辑单元)分别为:232、206、143.功能描述方式资源利用最优,但结构复杂。多路选择器方式优于总线方式,不仅是在资源利用上,还是在执行速度上。当然,总线方式对于模块的扩展方面要强于多路选择器方式。

如果想更深入了解其内部结构,可以使用Synplifypro软件观察这3种方式的RTL电路及门级电路。用Synplify pro软件进行综合,显示所需的LE比QuartusⅡ4.0更少。

3 结束语

微型计算机的原理及结构一般不易理解掌握,利用FPGA来学习并构建一个简易微型计算机无疑是一个好方法,对EDA的软硬件学习也是一个不错的选择,可为将来进行相关ASIC没计打下良好的基础。

-

微型计算机和单片机的基本结构2021-11-22 1900

-

如何去制作一台微型计算机2021-10-09 2701

-

微型计算机原理及应用2021-09-10 2440

-

微型计算机的硬件组成2021-09-02 1186

-

微型计算机的结构2021-07-21 1619

-

什么是微型计算机的组成原理2021-07-16 1526

-

基于FPGA的简易微型计算机结构及原理分析2019-06-27 1833

-

微型计算机基础知识2010-02-23 1412

-

微型计算机原理2009-10-10 1246

-

微型计算机基础与应用,下载2009-04-28 731

-

微型计算机接口技术原理及应用2006-03-21 1718

全部0条评论

快来发表一下你的评论吧 !