Altera Cyclone IV GX系列的特性及FPGA开发套件的设计方案介绍

描述

Altera 公司的Cyclone IV 系列FPGA包括两个系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元,高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业。本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA开发套件主要特性,框图,电路图和材料清单。

Altera 新的Cyclone®IV 系列 FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:

■ Cyclone IV E- 最低的功耗,通过最低的成本实现较高的功能性

■ Cyclone IV GX- 最低的功耗,集成了3.125 Gbps 收发器的最低成本的FPGA

Cyclone IV 器件集成了一个可选择的低成本收发器,在未影响性能的情况下,节省了功耗及成本。针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型应用,Cyclone IV 器件无疑是最理想的选择。

Cyclone IV 器件系列主要特性:

■ 低成本、低功耗的FPGA 架构:

■ 6 K 到150 K 的逻辑单元

■ 高达6.3 Mb 的嵌入式存储器

■ 高达360 个18 × 18 乘法器,实现DSP 处理密集型应用

■ 协议桥接应用,实现小于1.5 W 的总功耗

■ Cyclone IV GX 器件提供高达八个高速收发器以支持:

■ 高达3.125 Gbps 的数据速率

■ 8B/10B 编码器/ 解码器

■ 8-bit 或者10-bit 位物理介质附加子层(PMA) 到物理编码子层(PCS) 接口

■ 字节串化器/ 解串器(SERDES)

■ 字对齐器

■ 速率匹配FIFO

■ 公共无线电接口(CPRI) 的TX 位滑块

■ 电路空闲

■ 动态通道重配置以实现数据速率及协议的即时修改

■ 静态均衡及预加重以实现最佳的信号完整性

■ 每通道150 mW 的功耗

■ 灵活的时钟结构以支持单一收发器模块中的多种协议

■ Cyclone IV GX 器件对PCI Express (PIPE)(PCIe)Gen 1 提供了专用的硬核IP:

■ ×1,×2, 和×4 通道配置

■ 终点和根端口配置

■ 高达256-byte 的有效负载

■ 一个虚拟通道

■ 2 KB 重试缓存

■ 4 KB 接收(Rx) 缓存

■ Cyclone IV GX 器件提供多种协议支持:

■ PCIe (PIPE) Gen 1×1,×2, 和×4 (2.5 Gbps)

■ 千兆以太网(1.25 Gbps)

■ CPRI ( 高达3.072 Gbps)

■ XAUI (3.125 Gbps)

■ 三倍速率串行数字接口(SDI)( 高达2.97 Gbps)

■ 串行RapidIO(3.125 Gbps)

■ Basic 模式( 高达3.125 Gbps)

■ V-by-One( 高达3.0 Gbps)

■ DisplayPort(2.7 Gbps)

■ 串行高级技术附件(Serial Advanced Technology Attachment (SATA))( 高达3.0 Gbps)

■ OBSAI( 高达3.072 Gbps)

■ 高达532 个用户I/O

■ 高达840 Mbps 发送器(Tx), 875 Mbps Rx 的LVDS 接口

■ 支持高达200 MHz 的DDR2 SDRAM 接口

■ 支持高达167 MHz 的QDRII SRAM 和DDR SDRAM

■ 每器件中高达8 个锁相环(PLLs)

■ 支持商业与工业温度等级

Cyclone IV 器件系列体系结构

这一部分介绍了Cyclone IV 器件的体系结构,其中包括以下几方面内容:

■ FPGA 核心架构

■ I/O 特性

■ 时钟管理

■ 外部存储器接口

■ 配置

■ 高速收发器( 仅适用于Cyclone IV GX 器件)

■ PCI Express 的硬核IP( 仅适用于Cyclone IV GX 器件)

FPGA 核心架构

Cyclone IV 器件采用了与成功的Cyclone 系列器件相同的核心架构。这一架构包括由四输入查找表(LUTs) 构成的LE, 存储器模块以及乘法器。

每一个Cyclone IV 器件的M9K 存储器模块都具有9 Kbit 的嵌入式SRAM 存储器。您可以把M9K 模块配置成单端口、简单双端口、真双端口RAM 以及FIFO 缓冲器或者ROM,通过配置也可以实现表1-7 中的数据宽度。

Cyclone IV 器件中的乘法器体系结构与现有的Cyclone 系列器件是相同的。嵌入式乘法器模块可以在单一模块中实现一个18 × 18 或两个 9 × 9 乘法器。Altera 针对乘法器模块的使用提供了一整套的DSP IP,其中包括有限脉冲响应(FIR), 快速傅里叶变换(FFT) 和数字控制震荡器(NCO) 功能。Quartus®II 设计软件中的DSP Builder 工具集成了MathWorks Simulink 与MATLAB 设计环境,从而实现了一体化的DSP 设计流程。

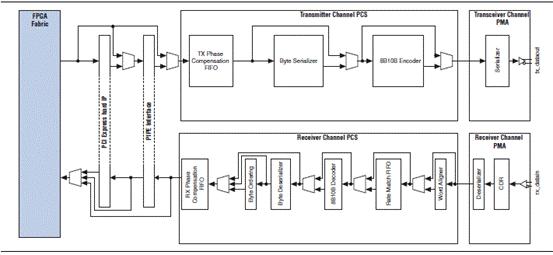

图1.Cyclone IV GX 器件的收发器通道框图

Altera Cyclone IV GX FPGA开发套件

Altera® Cyclone® IV GX FPGA开发套件为迅速开始开发低成本、低功耗FPGA系统级设计提供了全面的、同类最佳的设计环境。该套件帮助您缩短了产品开发周期,使您能够更迅速的将产品推向市场,树立新的产品里程碑。采用这一平台,您能够:

使用Cyclone IV GX PCI Express硬核知识产权(IP)和PCI-SIG®兼容电路板,开发并测试PCI Express® Gen1 x1、x2、x4端点设计。

使用板上DDR2存储器,通过其扩展功能,高速中间链接卡(HSMC)连接器,开发并测试多通路协议桥接设计。Altera合作伙伴提供30多种不同的HSMC,以及CPRI、SATA和SDI等支持协议。

重新使用套件电路板测试系统提供的实例设计,加速您的FPGA设计。

针对您产品的低成本和低功耗电路板,使用套件的主板作为设计模型。

Cyclone IV GX FPGA开发套件包括:

Cyclone IV GX FPGA开发板(参见图1)

安装的器件

F896封装的Cyclone IV GX EP4CGX150N FPGA

配置状态和设置单元

通过MAX® II EPM2210 CPLD和闪存进行被动串行(PS)配置

使用Quartus®II编程器的板上USB-BlasterTM下载电缆

时钟

板上时钟振荡器:50 MHz、100 MHz(可设置)和125 MHz

用于外部时钟输入的SMA连接器

用于时钟输出的SMA连接器

通用用户输入和输出

LED

LCD显示屏

按键和双列直插封装(DIP)开关

存储器件

128-MB DDR2 SDRAM,支持32位数据总线。

64-MB同步闪存和4-MB SSRAM

元件和接口

PCI Express边沿连接器

10/100/1000-Mbps以太网PHY,提供RJ-45连接器。

两个HSMC连接器

电源测量电路

电源

笔记本计算机直流输入

PCI Express边沿连接器电源

其他特性

PCI Express短卡

符合RoHS

Cyclone IV GX FPGA开发套件软件组成

设计实例

电路板更新入口,含有Nios®II处理器网络服务器,支持远程系统更新。

电路板测试系统

免费的Quartus II网络版软件,包括对Cyclone IV FPGA的支持,以及:

Nios II嵌入式设计套装

MegaCore®IP库包括PCI Express、三速以太网、SDI和DDR2高性能控制器MegaCore IP内核

通过OpenCore Plus进行IP评估

回环和调试HSMC

电源适配器和电缆

图2.Cyclone IV GX FPGA开发套件外形图和主要元件分布图

The board features the following major component blocks:

■ Cyclone IV GX EP4CGX150DF31 FPGA in the 896-pin FineLine BGA (FBGA)package

■ 1.2-V core power

■ MAX® II EPM2210GF256 CPLD in the 256-pin FBGA package

■ 1.8-V core power

■ FPGA configuration circuitry

■ MAX II CPLD EPM2210 System Controller and flash fast passive parallel (FPP) configuration

■ Active serial configuration

■ On-board USB-BlasterTM for use with the Quartus® II Programmer

■ JTAG header for external USB-Blaster with the Quartus II Programmer

■ On-Board ports

■ Embedded USB-Blaster

■ One gigabit Ethernet port

■ Communication ports

■ PCI Express (PCIe) edge connector

■ 10/100/1000BASE-T Ethernet PHY with RJ-45 connector

■ Two High-Speed Mezzanine Card (HSMC) interfaces

■ On-Board memory

■ 4-MB (x16) Synchronous Static Random Access Memory (SSRAM)

■ Two 32-MB (x32) DDR2 SDRAM

■ 64-MB flash

■ On-Board clocking circuitry

■ 50.000-MHz oscillator

■ 125.000-MHz oscillator

■ SMA clock input

■ SMA clock output

■ Programmable oscillator (default: 100.000-MHz)

■ General user I/O

■ LEDs and display

■ Eight FPGA user LEDs

■ One configuration done LED

■ One error LED

■ Five Ethernet status LEDs

■ One USB status LED

■ One power status LED

■ Five configuration LEDs

■ A two-line 16-character LCD display

■ Push-Button switches

■ One CPU reset push-button switch

■ One MAX II configuration reset push-button switch

■ One program-load push-button switch-configure the FPGA from flash memory

■ One program-select push-button switch-select image to load from flash memory or serial configuration (EPCS) device

■ Four general user push-button switches

■ DIP switches

■ Board settings DIP switch

■ JTAG chain select DIP switch

■ PCIe control DIP switch

■ Configuration settings DIP switch

■ User DIP switch

■ Power supply

■ 16-V DC input

■ 2.5-mm barrel jack for DC power input

■ On/Off slide power switch

■ On-Board power measurement circuitry

■ 20-W per HSMC interface

■ Mechanical

■ PCIe small form factor board

■ Bench-top operation

-

Altera宣布开始提供Cyclone V SoC开发套件2013-04-23 2720

-

Cyclone IV FPGA 器件系列概述2017-11-13 5089

-

什么是Altera系列低成本Cyclone IV FPGA?2019-07-31 4351

-

Altera交付Stratix IV GX收发器信号完整性开2009-04-23 740

-

Altera提供Arria II GX开发套件,加速高性能32009-07-30 727

-

Altera新Cyclone IV FPGA拓展了Cyclo2009-11-04 1596

-

Altera推出面向Stratix IV FPGA的最新开发2009-12-09 1038

-

Altera推出具有530K逻辑元件FPGA 的开发套件2009-12-10 844

-

低功耗Cyclone IV FPGA2010-03-31 1703

-

基于Arria II GX FPGA的开发方案2010-07-27 3451

-

Altera Cyclone IV GX系列FPGA开发方案2012-05-31 9715

-

Altera交付业界最全面的28nm FPGA系列开发套件2012-09-29 1382

-

Altera全面28nm FPGA及开发套件快速突击2012-11-19 1699

-

Cyclone 10 GX开发套件板的电路原理图免费下载2020-08-19 1248

-

Altera推出面向Stratix® IV FPGA的最新开发套件2020-08-30 1277

全部0条评论

快来发表一下你的评论吧 !