深入剖析ARM64异常处理:开发者必须掌握的底层核心逻辑

电子说

描述

在ARM64架构的开发领域,异常处理绝非单纯的理论知识点,而是直接决定系统稳定性、调试效率和功能实现的关键技术。无论是嵌入式开发、Linux内核移植,还是驱动开发与芯片调试,理解异常发生后CPU与软件的协同操作逻辑,都是开发者必备的核心能力。今天我们就深度拆解ARM64异常处理机制,同时聊聊开发者为何必须关注这一技术点。

一、异常发生后,CPU的自动操作细节

当ARM64处理器检测到异常(如中断、指令错误、数据访问异常、系统调用等)时,硬件会触发一系列原子性的自动操作,这是异常处理的基础,也是开发者分析问题的起点:

1.状态保存与寄存器赋值

CPU会将当前程序状态寄存器PSTATE的内容,自动保存到异常级别对应的SPSR_ELx(Saved Program Status Register)寄存器;同时把异常发生时的下一条指令地址写入ELR_ELx(Exception Link Register),将异常的具体原因和错误编码写入ESR_ELx(Exception Syndrome Register)。这三个寄存器是还原异常现场、定位问题的核心依据。

2.异常级别切换与栈指针选择

根据异常类型和配置,CPU会切换到预设的异常级别(EL0-EL3),并选择对应级别下的栈指针SP_ELx。例如,用户态(EL0)的系统调用会切换到内核态(EL1),并使用SP_EL1作为栈指针,保证内核执行的安全性。

3.向量表跳转

ARM64处理器的异常向量表是一段固定地址的内存区域,包含同步、异步、中断等不同类型异常的入口地址。CPU会根据异常的类型(如IRQ中断、FIQ中断、同步异常)和当前异常级别,跳转到向量表中对应的入口,触发软件层面的异常处理程序。

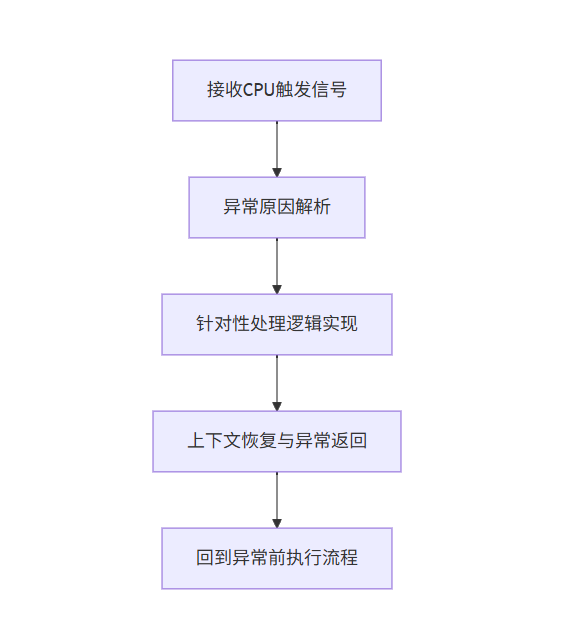

二、软件层面的异常处理核心工作

CPU的硬件操作仅完成了异常的“触发”,真正的处理逻辑需要开发者通过软件实现,核心工作可分为三步:

1.异常原因解析

开发者需通过读取ESR_ELx寄存器的编码,判断异常类型(如数据中止、指令中止、外部中断、系统调用等),以及异常的具体诱因(如内存访问权限不足、外设中断请求、非法指令执行等)。这一步是定位问题、处理异常的前提。

2.针对性处理逻辑实现

○对于外部中断:需根据中断控制器(如GIC)的寄存器,找到对应的外设中断号,调用预先注册的中断服务程序(ISR),处理外设的请求(如数据收发、状态变化)。

○对于数据/指令中止:需检查内存地址的合法性,判断是内存访问越界、页表缺失还是权限错误,进而执行页表修复、错误上报或进程终止等操作。

○对于系统调用:需解析系统调用号,执行内核对应的服务函数(如文件操作、进程管理),完成后将结果返回给用户态。

3.上下文恢复与异常返回

处理完成后,开发者需将SPSR_ELx中的状态恢复到PSTATE,并通过ERET指令将ELR_ELx中的地址加载到程序计数器(PC),让CPU回到异常发生前的执行流程。若涉及嵌套异常,还需通过栈帧管理保证多个异常现场不被覆盖。

三、开发者关注异常处理的核心价值

ARM64异常处理看似是底层硬件逻辑,实则直接影响开发的全流程,其价值主要体现在以下四个维度:

1.系统故障调试的关键抓手

当系统出现崩溃、死机、程序跑飞等问题时,异常处理相关的寄存器(SPSR_ELx、ELR_ELx、ESR_ELx)是定位问题的核心线索。例如,通过ELR_ELx可找到异常发生的指令地址,通过ESR_ELx可判断是内存访问错误还是非法指令,开发者能据此快速定位bug根源,而非盲目排查。

2.嵌入式与驱动开发的必备能力

在嵌入式开发中,外设中断是实现设备交互的核心方式(如按键触发、传感器数据采集),开发者必须掌握中断现场的保存、中断服务程序的编写,以及中断嵌套的处理逻辑,才能实现外设的稳定驱动。而驱动开发中的DMA操作、内存映射等功能,也依赖对异常(如数据中止)的处理来保证可靠性。

3.Linux内核移植与优化的核心环节

进行ARM64架构的Linux内核移植时,需重新实现异常向量表、配置中断控制器、适配异常处理框架。开发者需理解不同异常级别的切换逻辑,以及内核如何通过异常处理实现用户态与内核态的隔离、系统调用的执行,才能完成内核的定制化与优化。

4.提升系统稳定性与安全性

合理的异常处理逻辑能有效规避系统崩溃:例如,对非法内存访问的异常进行捕获,可避免程序直接退出;对中断优先级的合理配置,可防止高优先级中断被低优先级中断阻塞。同时,异常级别(EL)的隔离机制,能防止用户态程序非法访问内核资源,提升系统的安全性。

四、中断现场的关键细节

1.中断返回的指令判定

○同步异常(如指令错误、系统调用):CPU返回导致异常的指令,若为可修复错误(如页表缺失),修复后可重新执行该指令;若为不可修复错误(如非法指令),则终止程序。

○异步异常(如外部中断):CPU返回异常发生时即将执行的下一条指令,保证程序流程的连续性。

2.中断现场的保存规范

○保存内容:除CPU自动保存的寄存器外,开发者需手动保存通用寄存器(X0-X30)、栈指针(SP_ELx)等,避免处理异常时覆盖原有数据。

○保存位置:通常保存到当前异常级别对应的栈(如EL1异常使用SP_EL1);在多任务系统中,会将中断现场保存到任务控制块(TCB),确保任务切换后能恢复现场。

ARM64异常处理是硬件与软件协同的核心体现,也是开发者从“应用层”走向“底层”的必经之路。只有深入掌握这一机制,才能在ARM64开发中应对各类故障、实现复杂功能,构建稳定、高效的系统。

最近在看这本书,介绍的比较详细,不需要购买配套的开发板,在现有的开发板上和代码上就可以体现的淋漓尽致,为什么?因为这些底层技术是一样的也是相通的,一起加油吧!

-

Linux Kernel 6.1 tools目录全解析 | RK平台ARM64交叉编译实战指南2026-04-16 7751

-

深入剖析ARM64内核关键文件:kernel-6.1/arch/arm64/kernel/head.S2026-02-04 1472

-

云端AI开发者工具的核心功能2025-02-28 1146

-

《HarmonyOS第一课》焕新升级,赋能开发者快速掌握鸿蒙应用开发2025-01-02 646

-

ARM64位与ARM32位OP-TEE启动过程的差异2023-11-07 1855

-

海凌科新款arm64开发板wukongPi 4B简述2023-08-07 2625

-

AIO 3399ProC Linux根文件系统镜像(arm64/arm32)2022-09-21 736

-

Core 3399J Linux根文件系统镜像(arm64/arm32)2022-09-14 731

-

在arm64和x86服务器上运行的耗时来发现Docker在arm64架构下的性能问题2022-07-12 5604

-

浅析openat系统调用在arm64下的实现及使用原理2022-06-02 3548

-

微软推出首个可用于ARM64设备的x64仿真2020-12-11 2915

-

微软发布WinUI 3第三个预览版 ARM64 PC原生支持2020-11-18 2050

-

ARM64与ARM32 的Linux程序区别在哪里2019-08-09 29101

全部0条评论

快来发表一下你的评论吧 !