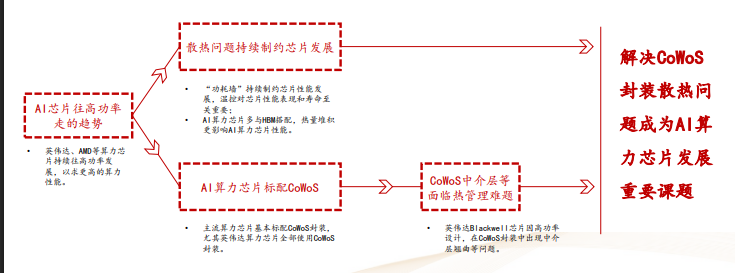

AI芯片发展关键痛点就是:CoWoS封装散热

描述

摘要:由于半导体行业体系庞大,理论知识繁杂,我们将通过多个期次和专题进行全面整理讲解。本专题主要从AI芯片发展关键痛点就是:CoWoS封装散热进行讲解,让大家更准确和全面的认识半导体地整个行业体系。我们分为半导体知识、半导体“芯”闻几个模块,欢迎各位大佬交流学习。

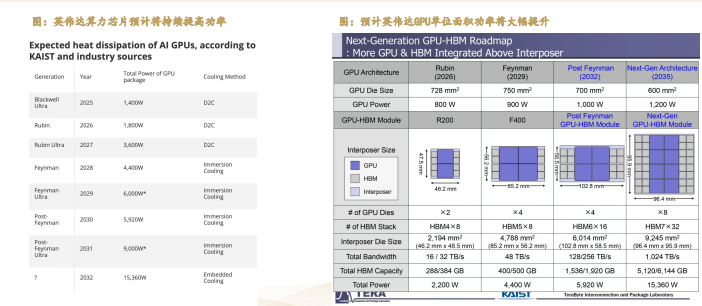

英伟达算力芯片功率持续上升,对散热提出更高要求

根据Nvidia、KAIST、tomshardware,以单die维度,H100单位面积功率约0.86w/mm²,Rubin 约1.1w/mm²,下一代Feynman约 1.2w/mm²,未来的架构甚至将冲高至2w/mm²,将是H100的233%。 我们认为伴随着多die和更多HBM的设计,热传导的压力进一步加大,材料中的热导率等性能变得更加关键。

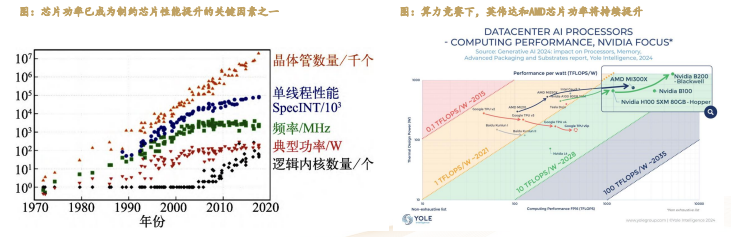

芯片发展遭遇“功耗墙”制约,散热是核心制约之一

根据《高算力Chiplet的热管理技术研究进展》,在微处理器40多年的发展中,晶体管数量呈指数级增加,但是典型的热设计功耗 (TDP)在最近20年基本保持在100~200W,导致芯片性能提升缓慢,集成电路发展受到“功耗墙”的严重制约。相比于SoC,基 于异质集成先进封装的Chiplet 可以实现更大面积、更多功能、更高密度的芯片集成,但也导致总热功耗增加、热分布不均、封装中 的热输运困难,同时存在严重的多物理场耦合效应,给热管理带来了更加严峻的挑战。根据Yole,英伟达和AMD在追求算力大幅提升的情况下,不得不继续提高芯片功率。

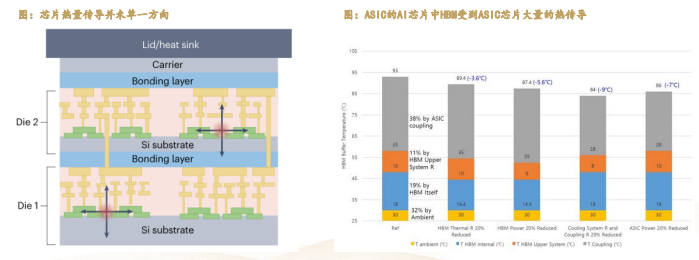

AI芯片与HBM存储紧密结合,热量堆积可能产生更多问题根据

Nature,硅基器件中的热传输基础为了冷却产生的热点,热量必须从产生点或局部最大值沿着系统中的热梯度转移。热传递的 两个最重要的材料属性是热容和热导率。传统层间介电材料提供的热绝缘进一步阻碍了散热,恶化了局部热点问题。这些挑战会导 致结温升高、器件性能下降以及过早失效的可能性增大。 • 根据三星电子相关论文,HBM 的温度升高可归因于环境温升(32%)、HBM 自身热阻(19%)、HBM 上方散热环境(约 11%) 以及来自 ASIC 的热耦合(38%)。

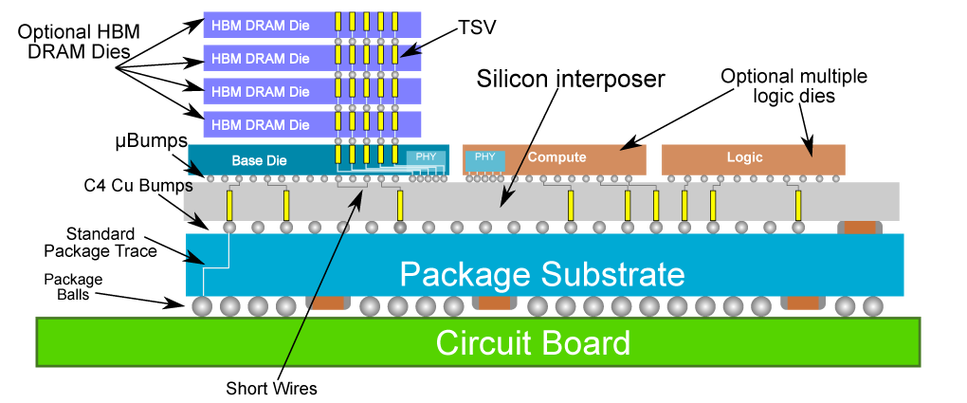

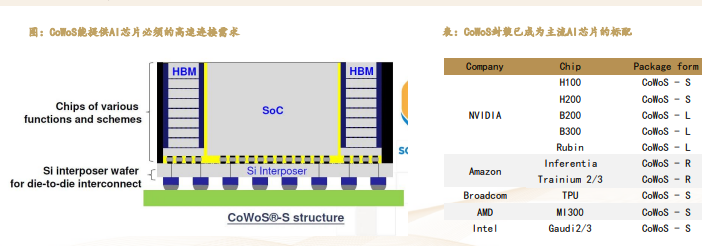

AI芯片因高速链接需求,基本上离不开CoWoS封装

根据Semianalysis,HBM 和 CoWoS 是互补的。HBM 的高焊盘数量和短走线长度要求需要像 CoWoS 这样的 2.5D 先进封装技术来 实现在 PCB 甚至封装基板上无法完成的如此密集、短的连接。CoWoS是主流的封装技术,以合理的成本提供最高的互连密度和最 大的封装尺寸。由于目前几乎所有的 HBM 系统都封装在 CoWoS 上,并且所有先进的 AI 加速器都使用 HBM,因此推论几乎所有 领先的数据中心 GPU 都由台积电封装在 CoWoS 上。 • 根据半导体产业纵横,HBM(高带宽内存)已是 AI 芯片的标配,但它不是随便一个封装就能适配。HBM 必须与处理器核心超近距 离、高带宽连接,这需要极密的走线与超短的连接距离。CoWoS 通过中介层提供这样的环境,让 HBM 的带宽(最高可 达 3.6TB/s)发挥到极致。

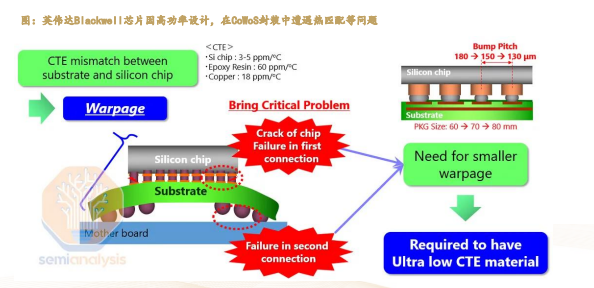

在高功率趋势下,CoWoS中介层已面临多项挑战

根据Semianalysis 24年8月的报道,Blackwell 家族在实现大批量生产方面遇到了重大问题。由于台积电的封装问题和英伟达的设 计,原始Blackwell封装的供应受到限制。Blackwell封装是第一个采用台积电CoWoS-L技术封装的大批量设计。 • 根据Semianalysis,CoWoS-L 是一项更复杂的技术,出现了各种各样的问题。其中一种是与在中介层中嵌入多个Bump有关,在有 机中介层内会导致各模块之间的热膨胀系数 (CTE) 不匹配,从而导致翘曲。

结论梳理:解决CoWoS封装散热问题成为AI算力芯片发展重要课题

根据《大功率电力电子器件散热研究综述》,当前大功率电力电子器件正朝着高功率水平、高集成度的方向发展,因此散热问题不 可避免的受到关注。已有研究表明,半导体芯片的温度每升高10 ℃,芯片的可靠性就会降低一半,器件的工作温度越高,器件的生 命周期越短。

-

台积电CoWoS平台微通道芯片封装液冷技术的演进路线2025-11-10 3641

-

2.5D封装为何成为AI芯片的“宠儿”?2025-03-27 1055

-

国产AI芯片破局:国产TCB设备首次完成CoWoS封装工艺测试2025-03-14 2263

-

日月光扩大CoWoS先进封装产能2025-02-08 1632

-

台积电超大版CoWoS封装技术:重塑高性能计算与AI芯片架构2025-01-17 2489

-

CoWoS先进封装技术介绍2024-12-17 6131

-

台积电CoWoS封装技术引领AI芯片产能大跃进2024-08-21 1722

-

什么是CoWoS封装技术?2024-08-08 10839

-

什么是 CoWoS 封装技术?2024-06-05 2302

-

CoWoS先进封装是什么?2023-07-31 6080

-

如何区分Info与CoWoS封装?2023-06-20 5158

-

如何解决芯片封装散热问题2023-06-04 11001

-

AI发展对芯片技术有什么影响?2019-08-12 3528

全部0条评论

快来发表一下你的评论吧 !