基于FPGA与的VHDL语言驱动时序发生器与数据缓存器的一体化设计

描述

1 引言

近年来,多通道面阵 CCD相机在气象观测、环境检测、海洋遥感和资源调查等领域获得了广泛的应用。而在 CCD的应用技术中,尤其是高速、多通道 CCD的应用中, CCD驱动时序的产生和信号的实时输出是两个非常关键的问题[1]。高速、多通道 CCD器件的驱动时序通常是一组周期性且关系比较复杂的脉冲信号,它是影响 CCD器件性能的一个重要因素;而产生的多组像元信号如何正确的转换成一帧完整图像,也必须根据实际的硬件要求而采取不同的设计方案。

本文在分析了 Sarnoff公司的 VCCD512H型帧转移面阵 CCD芯片的特性和工作过程后,结合整个 CCD相机电子系统的要求,完成了基于 FPGA技术的驱动时序发生器与数据缓存器的一体化设计,即在一块 FPGA芯片上实现对时序与数据缓存系统的控制。昀后针对 Xilinx公司的 FPGA器件 XQ2V3000对设计进行了配置及仿真,从而验证了该设计方案的可行性。 2 驱动时序发生器与数据缓存器一体化设计原理

2.1 CCD器件结构及工作原理

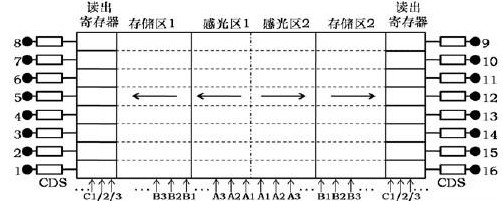

美国 Sarnoff公司的 VCCD512H是背照型帧转移面阵CCD,它由两个感光区、两个存储区和读出寄存器构成。每个感光区(或存储区)包含 8个子阵列,每个子阵列含有 256(行)×64(列)个有效像元,整个像面则由16个子阵列,共 512×512个有效像元构成,我们在应用中,对像元做了水平方向‘二合一’处理,使得整个像面共由 512x256个有效像元构成,昀终 16路信号并行输出。

电荷移动方向如图1中箭头所示,先由感光区转移到存储区(A1,A2,A3为帧转移控制信号),再由存储区转移到读出寄存器(B1,B2,B3为行转移控制信号),而后在读出控制信号(C1,C2,C3为像元转移控制信号)的作用下顺序读出。16个子阵列有各自独立的读出寄存器和 CDS放大器。信号的输出方式是 16个端口并行输出,送到后续的模拟、数字信号处理电路[2]。

2.2 驱动时序分析

由芯片结构可知,CCD的一个工作周期分两个阶段:感光阶段和转移阶段。在感光阶段,感光阵列接受外界光源照射产生电荷,帧转移控制信号 A不变,感光阵列和帧存储区之间为阻断态,不会发生电荷转移现象;同时由行转移控制信号 B控制,存储区中的电荷逐行转移到转移寄存器;行转移时,像元转移控制信号 C不变,无像元信号输出;每行信号中,各像元电荷逐次经过输出放大器输出,每读出一行信号,进行一次行转移。三相 CCD中,电荷的转移是通过三相控制电压按一定顺序依次变化来实现的。此处,进行电荷转移时,三相控制时序依次变化;三相信号不变时,为阻断态。为保证信号电荷的完整转移,各相时序间必须保证一定的电平交叠[3]。

在帧转移阶段,帧转移控制信号 A与行转移控制信号 B相同,且一直有效。同时像元控制信号 C也一直有效,但输出数据无效。进入感光阶段,首先进行一次行转移,开始信号的输出,同时感光区像元进入电荷积累。为保证信号读出的完整性,整帧转移的行数、输出的行数、像元数都进行了一定的冗余设置[4]。

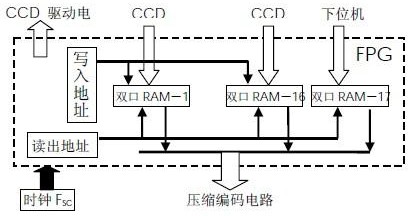

2.3 数据缓存器工作原理 如图 2所示,CCD传感器为 16路并行输出,每路为 256×32×12bit,即8192×12 bit,现采用 VHDL硬件描述语言,设计实现了一种基于片上集成的双口 RAM缓存器。

本设计中选用的控制器件FPGA为Xilinx公司XQ2V3000,其片内的共有96个双口 RAM,每个 RAM的深度为16K,而在该系统中为了实现帧缓存的功能,在设计中采用了两个双口 RAM并行连接的方式,从而组合成了 16K×16bit的双口 RAM缓存单元,共占用 RAM资源34个。双口 RAM的写入地址为 14位,由写入地址发生器统一提供,与 CCD的驱动波形相配合 [5]。具体实现时是将双口RAM 分成上下两区(每个缓冲区共有 64x266个像元),前一幀周期左边写上半区,右边读下半区;后一幀周期,左边写下半区时,右边读上半区。其写入过程为:首先由A 、B三相驱动脉冲(共 266个波形)配合,完成 A->B的电荷转移;然后用 B波形完成两次 B->C转移(两行合并),再用 C波形完成72次串出,其中仅有 64个有效(第 3-66像元),其余为过扫描,用于行箝位。这一过程重复 133次,(前 5次丢弃)。 因为图像数据的读出要按预定顺序,即 512行从上到下,每行 256个像元从左到右。为此,将 17个双口 RAM的输出作为一个整体来考虑,其存储量为(512×256+128)×12 bit,即131,200×12 bit,需要18 位地址,该读出地址的形成可以用一个18 位计数器和一个译码器完成 [6]。

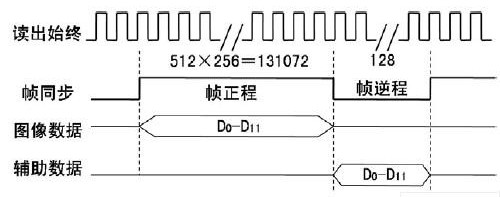

如图 3所示,在幀正程期间,从数据缓存读出 512 × 256 × 12bit的图像数据,在帧逆程期间,缓存器中的辅助数据紧随其后被读出。

3 一体化设计的 FPGA实现及仿真结果

3.1 现场可编程门阵列(FPGA)

系统中采用容量比较大的FPGA,利用 VHDL硬件描述语言完成 CCD驱动时序的设计和数据的高速读写。这种实现方法可以使采集系统灵活、简单、方便,具有很强的可扩展性,可根据需要设计为不同数据宽度、不同容量的数字系统,接口电路简洁且不占用系统地址资源,系统移植或升级换代方便,而且控制简单,易于实现[7]。

3.2 时序仿真结果

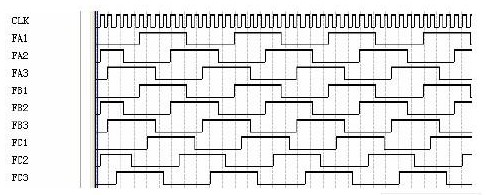

在编程软件 Quartus II集成设计环境下,用 VHDL语言以自上而下的方式,对 CCD驱动时序和数据缓存系统进行了描述,仿真后得到部分结果如下图所示。

图 4为在帧转移过程中,通过对时钟 CLK的计数而产生了频率相同、相位不同的A、B驱动脉冲信号,并且通过后续的示波器检测得知电平交叠达到了75%以上,满足技术手册的要求。

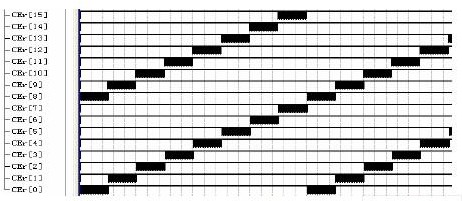

图 5为 RAM选择地址仿真图。系统总共有 17个 RAM缓存器,并且把每个 RAM分为了上、下两个半区。设CEr为 16位用来选择 RAM的位置,其中高8位为上半区,低 8位为下半区,并且交替选择(上半区读出时,下半区为写入,反之亦然)。从昀终的仿真图中可以看出,时序复合设计要求。

4 结束语

本文的创新点在于采用了 FPGA技术设计 CCD驱动时序和缓存器电路,使原来复杂的电路设计变成只需 1片 FPGA就能完成。同时它能够很好地满足 CCD应用向高速、小型化、智能化、低功耗发展的需求,从而提高了系统的集成度。从时序仿真结果来看,该一体化的设计能够较好的产生器件所需的时序脉冲及缓存器所需的读/写地址,并且由于使用了延迟量小的 FPGA使得系统可以工作在百兆赫兹的工作频段,从而增强了电路的抗干扰能力,提高了系统的可靠性与稳定性。

-

一体化高频高压发生器输出模式——每日了解电力知识2024-07-03 996

-

一种步进电机的一体化控制驱动器2021-09-10 2284

-

一体化伺服电机报警信息在哪个参数里面查看?2021-06-28 1453

-

如何完成基于FPGA技术的驱动时序发生器与数据缓存器的一体化设计?2021-06-08 2310

-

T86 带电池一体化高压信号发生器的功能特点介绍2021-06-01 736

-

用VHDL语言编写的基于FPGA的波形发生器,使用了QuartusII程序2019-08-10 2033

-

采用FPGA设计科学级CCD相机时序发生器2017-11-24 2666

-

什么是机电一体化2017-08-29 4283

-

【云智易申请】一体化机柜监控设计2015-07-23 3388

-

浅析机电一体化的发展趋势2012-10-21 3450

-

CCD时序电路与数据缓存器的一体化设计2010-01-06 671

全部0条评论

快来发表一下你的评论吧 !