基于Xilinx开发平台和FPGA器件实现一维成像雷达目标识别

描述

1、引言

目标识别作为现代雷达的重要发展方向之一,成为未来武器系统中的一个重要组成部分和当前国内外关注的热点,具有广泛的民用和军事应用价值。根据雷达的探测手段及应用背景的不同,出现了多种识别方法,其中雷达成像识别技术作为雷达目标识别的一种新技术正在日趋成熟。而与二维成像雷达相比,易于实现的一维成像雷达(高距离分辨率雷达)在目标识别方面有着广阔的前景。

文献[1]对基于一维距离像的子空间方法进行了广泛而深入的研究,在普通特征子空间的基础上,提出了正则子空间法、修正特征子空间法、综合子空间法、子空间串法等多种子空间法,在对仿真与实测数据的识别中均取得较好的效果。其中部分算法的FPGA实现研究正是本文研究的主要任务。

CORDIC算法(The Coordinate Rotation Digital Com-puter)是Voider等人于1959年在美国航空控制系统的设计中提出来的,他是一种用于计算一些常用的基本运算函数和算术操作的循环迭代算法,其基本思想是用一系列与运算基数相关的角度的不断偏摆从而逼近所需旋转的角度。本质上讲他是一个数值性计算逼近的方法,由于这些固定的角度与计算基数有关,运算只有移位和加减。可用该算法来计算的函数包括乘、除、平方根、正弦、余弦、反正切、向量旋转(既复数乘法)以及指数运算等。1971年,J.S.Walther提出了统一的CORDIC算法形式,把圆周旋转、双曲旋转和直线旋转统一到同一个CORDIC迭代方程里。为同一硬件实现多功能提供了前提,随着VLSI技术的发展,CORDIC算法越来越受到研究与应用人员的重视,Xilinx公司于2002年发布了其CORDIC的IP核,由于IP核技术的可重用特性,可以使CORDIC算法获得更广泛的应用。

2、CORDIC原理

CORDIC算法的原始思想一经提出,就受到了人们的普遍关注,随着FPGA技术的发展,CORDIC获得了愈来愈广泛的应用,CORDIC算法可以分解为一些简单的且在硬件中容易实现的基本算法,如加法、移位等,使得这些算法在硬件上可以得到较好的实现。又因为该算法是一种规则化的算法,他满足了硬件对算法的模块化、规则化的要求,因此CORDIC算法可以充分发挥硬件的优势,利用硬件的资源从而实现硬件与资源相结合的一种优化方案,下面简要介绍其基本原理。

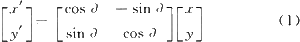

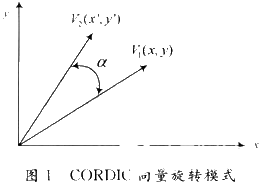

若将向量[z,y]T沿逆时针方向旋转角度a如图1所示,初始向量V1经旋转a角以后得到向量V2。

也即:

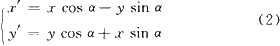

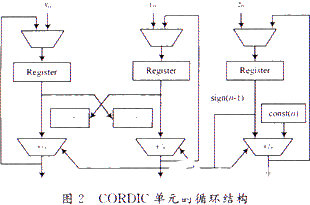

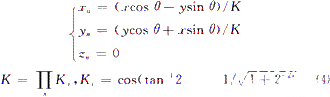

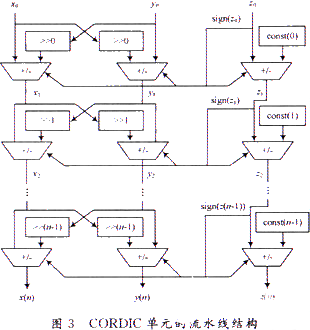

在应用过程中,CORDIC的实现方式我们主要讨论循环结构(图2)以及流水线结构(图3)。图2采用的是并行的数据格式,由于其大的扇人量,不适合在单个逻辑单元扇入量有限的FPGA上实现。如果在FPGA上实现将会占用大量的逻辑块,浪费资源,而且路径的拉长会导致其速度的降低。在图3所示的流水线结构中,每一个移位器都是固定的深度,而且旋转角度集的各个值作为常数值直接连到角累加器件上面,不需要存取空间和读取时间。在FPGA器件中每个细胞元都有寄存器,便于采用流水线技术。

3、实现技术中的IP核的应用

在实际的设计中,我们采用了Xilinx系列芯片中的IP核来完成设计,这样做的目的主要是为了充分利用芯片的内部资源,实现内部结构的优化设计,IP核生成工具可以是各种类型、功能的模块。这些IP核是根据Xilinx的FP-GA器件特点和结构而设计,直接用Xilinx FPGA底层硬件原语进行描述,可充分将FPGA的性能发挥出来,其实现结果在面积和速度上都能达到令人满意的效果。

4、数值精度问题

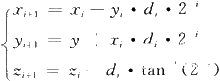

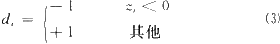

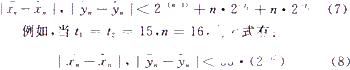

在应用每一个数值实现方法时,他的数值精度是我们不得不考虑的问题,CORDIC算法也不例外。WaltherHu、Kota都对他进行了深入的研究,分别对其定点和浮点实现方式的数值精度给出了定量描述或在数学上进行了分析,不同的算法模式不同的操作模式有着不同的结果。CORDIC的误差主要来自两方面:一方面,在用旋转角度集来表示角度时,有限子集产生了截断误差;另一方面由于有限字长的限制,在数据表示和移位运算中产生了舍人误差。由于CORDIC的3个方程之间相互作用,这为分析CORDIC的误差带来了很大的难度。以旋转模式的误差分析为例,我们以x,y,z表示有限精度下的计算值,xi,yi,zi表示无误差的精确值,z,y,z表示数学意义上得到的值,旋转模式时的迭代方程为:

其中:

经n次迭代后得到:

对于x,y分量来说,若假定z分量对他们的作用因子di是精确的,则他们主要是受舍入误差的影响,设x,y由t1位表示,且均为小数位,则有限精度下的x,y分量经过n次迭代后将产生大约log2n位的舍入误差。对于z分量来说,其误差主要来自两方面:一方面是截断误差,设为ezl,由CORDIC收敛性可知:

另一方面是舍人误差ez2,若假定用t2来表示z分量则│ez2│《2-t2,假定θ为精确值,a为计算值,则:

综上有:

从上面结果中,我们发现只要在算法内部数据中增加log332Δ5位长度的保护位,则可以校正误差,在输出结果中获得15位的精度。

5、 仿真实验

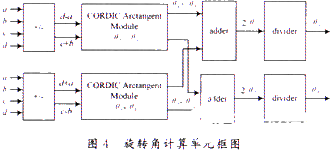

在实现了各种处理单元以后,我们可以很方便地将其应用于阵列中来计算矩阵的奇异值分解。一个2×2矩阵的SVD实际上就是一个旋转角计算单元与双边旋转计算单元的组合,结构框图如图4所示。

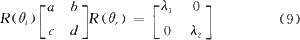

旋转角计算主要按照直接2-角方法,分别计算出θr+θt和θr-θt,通过加法器和减法器以及除法器,得到θr和θt。一个2×2矩阵的双边旋转为:

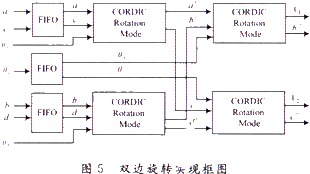

在设计中,我们注意到角θr要等到θt,旋转完成后才输入到旋转器中,我们通过添加FIFO做为延时控制单元,通过控制FIFO的深度来完成数据的同步,获得同时钟频率一样高的数据流量。双边旋转实现框图如图5所示。

使用VHDL语言进行模块功能描述,在Xilinx仿真平台ISE 7.1以及Modelsim SE 5.7d环境下的仿真结果如图6所示,系统工作的时钟频率为50 MHz,在选用高端的Virtcx4系列芯片进行算法的时序仿真时,资源的占用都是比较少的。这为下一步的高阶子空间算法的实现奠定了比较好的基础。

6 、结 语

本文在基于Xilinx的软硬件开发平台上,对用FPGA实现用于雷达一维像目标识别的特征子空间方法进行了一系列的探讨与研究,深入研究了CORDIC理论在数值精度、操作模式上的各种应用,并且用于FPGA设计实现二维子空间的研究并且成功地进行了硬件仿真实现,下面的工作是结合并行雅可比方法采用Systolic阵列结构进行高阶子空间分解的FPGA实现,这部分工作将在后面的研究中完成。

责任编辑:gt

-

开发者手机 AI - 目标识别 demo2024-04-11 1801

-

基于三维激光点云的目标识别与跟踪研究2022-01-17 1220

-

基于DSP的毫米波主被动复合探测器目标识别系统设计【回映分享】2021-12-30 11172

-

一种适用于空间观测任务的实时多目标识别算法分享2021-12-21 1748

-

感知起源招聘FPGA工程师(坐标北京)2021-11-29 1658

-

基于DSP和FPGA组合的嵌入式图像处理平台的实时多目标识别算法2021-10-29 6281

-

Arbe将开发基于成像雷达开发平台的新一代雷达系统2020-10-29 2218

-

【PYNQ-Z2申请】图像目标识别FPGA硬件加速2019-01-09 5287

-

红外动目标识别跟踪系统的实现方案2017-01-12 776

-

Xilinx与IBM通过SuperVesselOpenPOWER开发云平台实现 FPGA加速2016-04-11 932

-

RCS目标识别2015-01-27 2993

-

红外目标识别跟踪系统的DSP+FPGA实现2011-09-16 1724

-

基于USB和目标识别的图像采集系统的设计实现2009-08-13 599

-

改进最优聚类中心雷达目标识别法2009-05-20 453

全部0条评论

快来发表一下你的评论吧 !