集成电路制造中Bosch工艺的关键作用和流程步骤

描述

文章来源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文介绍了集成电路制造中Bosch工艺的特点、流程与优势。

Bosch工艺,又称交替侧壁钝化深层硅蚀刻工艺,是一种在半导体制造中用于刻蚀硅片上特定材料层的先进技术,由Robert Bosch于1993年提出,属于等离子体增强化学刻蚀(反应离子刻蚀)的一种。该工艺通过独特的“刻蚀-钝化”循环,实现了高深宽比、各向异性的微结构加工,广泛应用于微机电系统(MEMS)、深硅刻蚀及硅通孔(TSV)制造等领域。

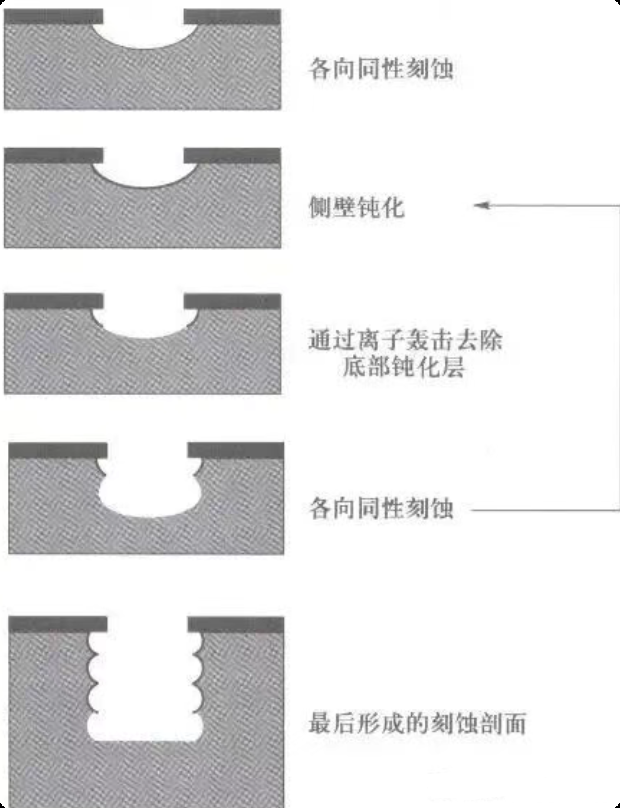

其核心原理基于周期性交替进行的三个子过程:首先进行基础刻蚀,使用SF6气体产生氟离子对硅进行各向异性刻蚀,形成初始沟槽或孔洞;随后进入侧壁保护阶段,通入C4F8气体,在等离子体作用下于侧壁沉积一层聚合物保护膜;最后进行侧壁刻蚀,再次切换回SF6刻蚀环境,去除沟槽底部的硅材料而保护侧壁。这三个阶段构成一个完整循环,通过多次重复,逐步加深结构直至达到所需深度。

在TSV与先进封装中的关键作用

在高性能计算、人工智能等领域广泛应用的HBM(高带宽内存)等3D堆叠技术中,硅通孔(TSV)是实现芯片垂直电气连接的关键。TSV技术要求在硅基板上刻蚀出深且直的高深宽比孔洞。Bosch工艺凭借其高深宽比、高精度和各向异性刻蚀能力,成为制造TSV结构的理想选择,对于HBM和TSV的制造起到了至关重要的作用。

具体而言,在TSV工艺流程的“孔形成”步骤中,普遍采用基于Bosch工艺的深反应离子刻蚀(DRIE)。该工艺能够刻蚀出深度达几十至几百微米、尺寸为几微米到几十微米的高深宽比通孔,确保了垂直互连的可靠性和性能。TSV技术通过这种垂直连接,大幅缩短了互连长度,降低了信号延迟和功耗,提高了数据传输速率,是实现3D IC封装和异构集成的核心技术。

工艺特点与优势

Bosch工艺具备多项显著特点与优势。首先是高深宽比,能够实现几十至几百微米的深宽比,满足深槽、深孔结构的制造需求。其次是优异的各向异性,即垂直刻蚀能力,能有效抑制侧向刻蚀,形成近乎垂直的刻蚀剖面,这对器件小型化和高密度集成至关重要。第三是高选择性,通过调节工艺参数,可以实现对硅、二氧化硅、氮化硅等不同材料的选择性刻蚀。最后是良好的工艺可控性,通过精确控制脉冲频率、气体流量、功率等参数,能够精细调整刻蚀速率、剖面形貌和均匀性,适应复杂的制造要求。

具体工艺流程步骤

一次完整的Bosch工艺通常包含以下步骤:首先是预清洗和腔室准备,确保硅片表面清洁并设定好工艺气体环境。接着进入等离子体生成与刻蚀阶段,启动射频电源产生等离子体,活性粒子与硅反应进行刻蚀。然后切换至钝化阶段,通入钝化气体(如C4F8)在侧壁形成保护膜。之后,重复进行“刻蚀-钝化”循环,逐步加深结构。当达到预定刻蚀深度后,终止刻蚀并进行后处理清洗,去除残留副产物。

该工艺的循环方式本质上是“刻蚀→形成侧壁保护层→重复交替”,通过这种周期性操作实现深度方向的“阶梯状”深刻蚀,同时保护侧壁形态。

应用领域与未来发展

Bosch工艺的应用已扩展到半导体制造的多个关键领域。在MEMS器件制造中,用于加工压力传感器、加速度计等所需的复杂三维微结构。在存储器制造中,用于刻蚀DRAM电容器的深电极孔和3D NAND Flash的深沟槽通道。在功率半导体中,用于制造改善器件性能的深沟槽结构。此外,还应用于光电子器件的微光学结构加工以及深沟槽隔离等。

随着技术发展,Bosch工艺也在不断演进以应对新挑战,如优化工艺参数以减少侧壁“扇贝效应”(波纹),以及将工艺拓展至碳化硅(SiC)等更难刻蚀的宽禁带半导体材料。未来,该工艺将继续推动3D集成、先进封装和异构集成技术的发展,满足后摩尔时代对更高性能、更小尺寸和更优架构的追求。

Bosch工艺作为一种精密的深硅刻蚀技术,通过其创新的循环刻蚀与钝化机制,为现代半导体产业,特别是3D集成与先进封装,提供了制造高深宽比、高精度微结构的关键解决方案,其持续创新将对未来电子器件的发展产生深远影响。

-

CMOS超大规模集成电路制造工艺流程的基础知识2025-06-04 2979

-

集成电路制造中的电镀工艺介绍2025-03-13 3121

-

集成电路制造中的划片工艺介绍2025-03-12 3712

-

Bosch刻蚀工艺的制造过程2024-10-31 4817

-

制造半导体芯片的十个关键步骤2024-02-19 4022

-

国产EDA“夹缝”生存 集成电路设计和制造流程2023-09-28 3596

-

集成电路塑封工艺流程及质量检测2023-09-08 4902

-

集成电路基本的工艺流程步骤2022-02-01 34449

-

芯片制造工艺流程步骤2021-12-15 46656

-

集成电路芯片封装工艺流程2021-07-28 14218

-

CMOS集成电路制造工艺的详细资料说明2019-07-02 3844

-

集成电路制造工艺2016-04-15 1036

-

仿真技术在半导体和集成电路生产流程优化中的应用2009-08-20 3209

全部0条评论

快来发表一下你的评论吧 !