Salicide自对准硅化物工艺的定义和制造流程

描述

文章来源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文介绍了自对准硅化物工艺的特点、优势、以及挑战。

什么是Salicide

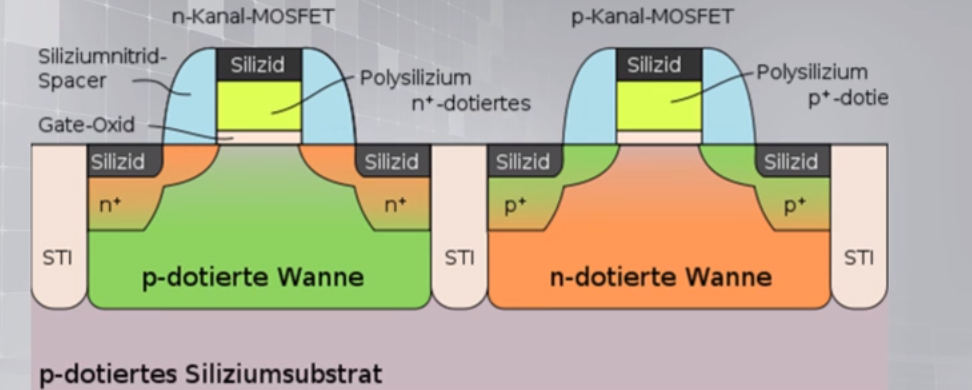

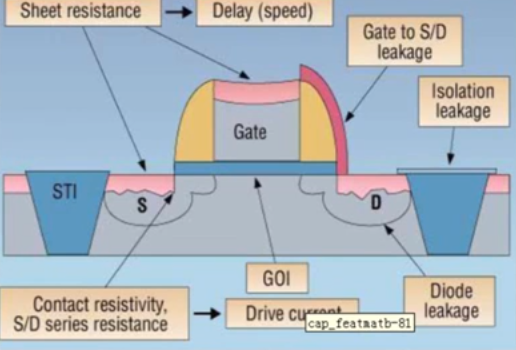

Salicide(Self-Aligned Silicide,自对准硅化物)是一种通过选择性金属沉积与硅反应,在半导体器件的源/漏极(Source/Drain)和栅极(Poly Gate)表面形成低电阻金属硅化物的工艺。其核心在于“自对准”特性:无需额外光刻步骤,仅通过阻挡层(如SAB,Salicide Block)控制硅化物形成区域,从而简化流程并提高精度。

早期工艺采用TiSi₂(硅化钛),但其窄线条效应导致电阻率上升,逐渐被CoSi₂(硅化钴)取代。随着制程微缩至90nm以下,NiSi(硅化镍)因更低电阻、更少硅消耗及低温工艺优势成为主流。例如,NiSi在30nm线宽下仍能保持低电阻,而CoSi₂在40nm以下电阻急剧升高。

硅化物通过减少多晶硅和单晶硅的接触电阻(Contact Resistance)及薄层电阻(Sheet Resistance),显著提升器件速度。以0.15μm CMOS工艺为例,TiSi₂工艺可将栅极和源/漏极的方块电阻降至45Ω/□,使环形振荡器延迟缩短至1.9 ps。

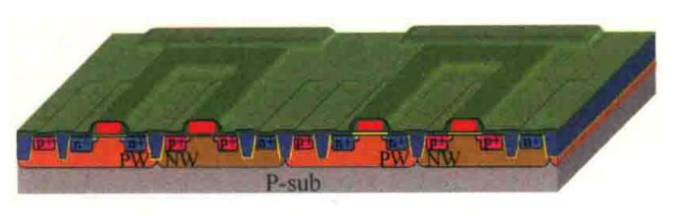

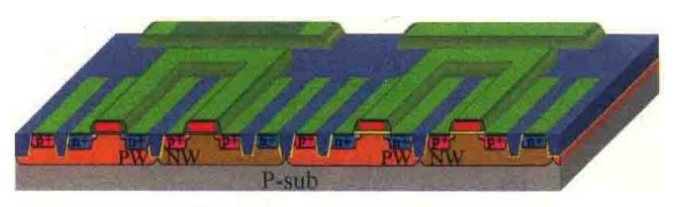

Salicide工艺的制造流程

1. 阻挡层(SAB)的沉积与图形化

通过PECVD(等离子体增强化学气相沉积)在晶圆表面覆盖SiO₂阻挡层,并利用光刻技术定义非硅化物区域。例如,SAB光刻需与有源区(AA)严格对准,避免后续金属硅化物在非目标区域形成,导致短路。

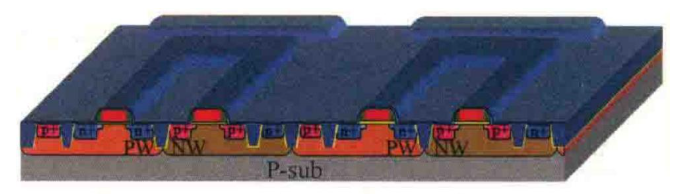

2. 金属沉积与退火反应

采用PVD(物理气相沉积)溅射钴(Co)或镍(Ni)等金属,覆盖TiN作为抗氧化层。随后进行两步快速热退火(RTA):

第一步RTA(约550°C):形成高阻态硅化物(如Co₂Si);

第二步RTA(约850°C):转化为低阻态硅化物(如CoSi₂或NiSi)。

此过程需精准控制温度,防止硅化物横向过度生长引发栅漏短路。

3. 选择性刻蚀与后处理

通过湿法刻蚀(如NH₄OH+H₂O₂)去除未反应的金属和TiN层,并清洗残留氧化物。最后沉积SiON保护层,防止后续工艺中硼磷杂质扩散影响器件性能。

Salicide工艺的优势与技术挑战

1. 性能提升的核心贡献

降低电阻:源/漏极接触电阻降低30%-50%,栅极电阻减少至传统工艺的1/5,显著缩短RC延迟。

提升集成度:自对准特性避免光刻对准误差,支持更小线宽设计,例如0.18μm工艺中CoSi₂取代TiSi₂,突破窄线条效应限制。

2. 工艺中的关键挑战

ESD防护能力下降:低阻硅化物成为ESD电流优先路径,大电流导致局部高温烧毁器件。解决方案包括引入SAB工艺形成非硅化区域,或通过ESD IMP(注入工艺)调整击穿电压。

热稳定性问题:NiSi在600°C以上会相变为高阻态NiSi₂,需采用尖峰退火(Spike Anneal)或毫秒级退火(MSA)优化热预算。

Salicide在先进制程中的应用与未来

1. 当前主流应用场景

逻辑芯片:90nm以下CMOS工艺中,NiSi广泛用于CPU和GPU,支持高频运算;

存储器:DRAM和闪存通过Salicide降低位线电阻,提升读写速度。

2. 未来技术演进方向

新型材料探索:铂(Pt)或稀土金属硅化物因更高热稳定性进入研究视野;

3D集成兼容性:FinFET和GAA结构中,需开发低温激光退火工艺,避免多层堆叠的热应力损伤。

Salicide工艺是半导体微缩化进程中不可或缺的技术,其自对准特性与材料创新持续推动器件性能突破。然而,ESD防护、热稳定性等问题仍需跨学科协作攻克。

-

半导体制造的合金化热处理工艺2022-09-21 7015

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1584

-

双面柔性PCB板制造工艺及流程2011-02-24 3353

-

揭秘十一道独门芯片工艺流程2016-07-13 8448

-

集成电路制造工艺2019-04-26 3097

-

芯片制造全工艺流程解析2020-12-28 18988

-

PCB制造工艺流程是怎样的?2021-11-04 24396

-

芯片制造工艺流程步骤2021-12-15 46091

-

集成电路芯片制造中的3种硅化物工艺介绍2022-11-21 11953

-

自对准硅化物 (Self -Aligned Silicide) 工艺2023-01-10 15339

-

Salicide工艺的制造流程2024-11-11 3305

-

MOSFET晶体管的工艺制造流程2024-11-24 6093

-

IBC技术新突破:基于物理气相沉积(PVD)的自对准背接触SABC太阳能电池开发2025-04-14 1278

-

芯片制造中自对准接触技术介绍2025-05-19 1288

-

自对准硅化物工艺详解2025-05-28 2310

全部0条评论

快来发表一下你的评论吧 !